Создайте модель для этого примера:

Создание модели Simulink ®.

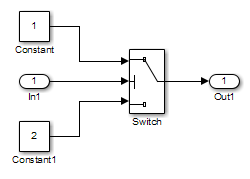

Скопируйте следующие блоки в пустое окно модели:

Из библиотеки источников - блок Inport для инициирования входного сигнала, значение которого Verifier™ Simulink Design управляет.

Из библиотеки Sources два блока констант используются в качестве входных данных блока Switch.

Из библиотеки маршрутизации сигналов блок коммутатора обеспечивает простую логику.

Из библиотеки Sinks - блок Outport для приема выходного сигнала.

В модели дважды щелкните один из блоков константы и укажите его параметр константы как 2.

Подключите блоки таким образом, чтобы модель выглядела аналогично следующей схеме.

На вкладке Приложения щелкните стрелку справа от раздела Приложения.

В разделе Проверка модели (Model Verification), Проверка (Validation) и Тест (Test) щелкните Проверка конструкции (Design Verifier).

На вкладке «Design Verifier» в разделе «Prepare» в раскрывающемся меню параметров режима выберите «Settings».

В диалоговом окне «Параметры конфигурации» выберите панель «Решатель». В списке Решатель (Solver):

Задайте для параметра «Тип» значение Fixed-step.

Задайте для опции «Решатель» значение Discrete (no continuous states).

Simulink Design Verifier анализирует только модели, использующие решатель с фиксированным шагом.

Нажмите кнопку ОК, чтобы сохранить изменения и закрыть диалоговое окно Параметры конфигурации (Configuration Parameters).

Сохраните модель с именем ex_generate_test_cases_example.

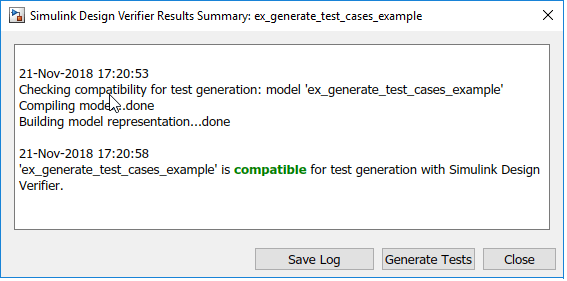

Каждый раз, когда Simulink Design Verifier анализирует модель, перед началом анализа программа выполняет проверку совместимости. Если модель несовместима, программа не может проанализировать ее.

Перед началом анализа можно также убедиться, что модель совместима с программой Simulink Design Verifier:

Откройте окно ex_generate_test_cases_example модель.

На вкладке «Проверка проекта» нажмите кнопку «Проверить совместимость».

Программа отображает окно журнала, в котором указывается, совместима ли модель с анализом.

Только что созданная модель совместима.

Если проверка совместимости показывает, что модель частично совместима, модель содержит по крайней мере один объект, который Simulink Design Verifier не поддерживает. Можно проанализировать частично совместимую модель, но по умолчанию неподдерживаемые объекты блокируются. Результаты анализа могут быть неполными.

Дополнительные сведения об автоматическом блокировании см. в разделе Обработка несовместимости с автоматическим блокированием.

Настройка Simulink Design Verifier для генерации тестовых примеров, которые обеспечивают 100% -ный охват решений для ex_generate_test_cases_example модель:

Откройте окно ex_generate_test_cases_example модель.

На вкладке Design Verifier в разделе Mode выберите Test Generation.

Нажмите кнопку Test Generation Settings (Параметры создания тестов).

В диалоговом окне Configuration Parameters на панели Test Generation установите для параметра Model coverage targets значение Decision.

В этом примере анализ создает тестовые случаи, в которых записывается только покрытие принятия решений.

Параметр оптимизации набора тестов по умолчанию имеет значение Auto. Если требуется создать меньше, но больше тестовых примеров, выберите LongTestcases для параметра оптимизации набора тестов.

Нажмите кнопку ОК, чтобы сохранить изменения и закрыть диалоговое окно Параметры конфигурации (Configuration Parameters).

Сохранить ex_generate_test_cases_example модель.

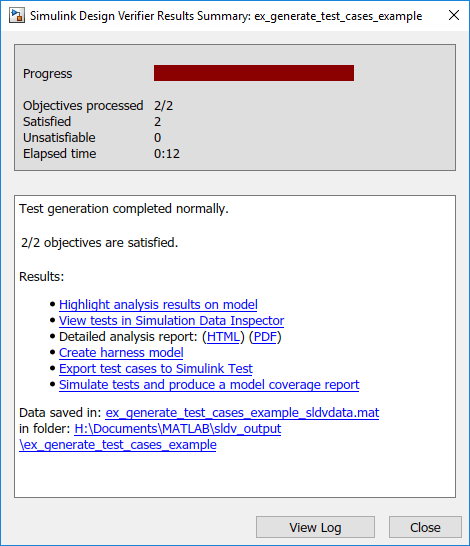

На вкладке Design Verifier щелкните Generate Tests (Генерировать тесты). Simulink Design Verifier анализирует модель для создания тестовых примеров.

Во время анализа в окне Сводка результатов (Results Summary) отображается ход выполнения анализа. Здесь отображается такая информация, как количество обработанных целей тестирования и удовлетворенные цели.

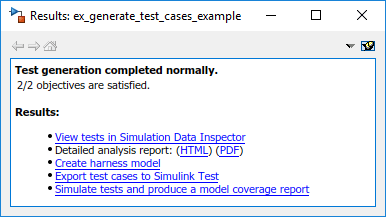

По завершении анализа в окне Сводка результатов (Results Summary) отображаются эти опции для просмотра результатов.

В следующих разделах описывается, как можно просмотреть результаты анализа.

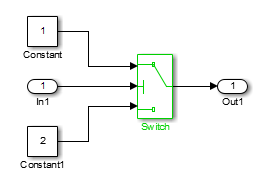

Выделите результаты анализа в примерной модели:

В окне Сводка результатов для ex_generate_test_cases_example щелкните Подсветить результаты анализа на модели (Highlight analysis results on model).

Блок Switch выделен зеленым цветом, что указывает на то, что блок Switch имеет тестовые примеры, удовлетворяющие его контрольным целям.

Окно Результатов Свидетельства Дизайна Simulink открывается. При щелчке объектов в модели это окно изменяется для отображения подробных результатов анализа для этого объекта. По умолчанию окно Результаты Simulink Design Verifier всегда является самым видимым. Чтобы позволить окну перемещаться за другим окном, щелкните![]() и снимите флажок Всегда сверху.

и снимите флажок Всегда сверху.

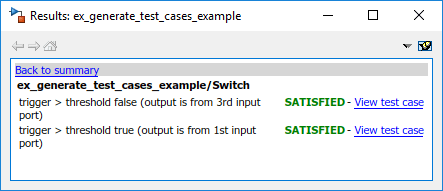

Щелкните выделенный блок переключения.

Окно Результатов Свидетельства Дизайна Simulink указывает, что анализ произвел прецеденты для обеих испытательных целей:

trigger > threshold

trigger < threshold

Дополнительные сведения о выделенных результатах анализа модели см. в разделе Выделенные результаты модели.

Создайте подробный отчет HTML-анализа:

В окне Резюме Результатов Свидетельства Дизайна Simulink, в отчете о Подробном анализе, нажимают HTML.

Отчет HTML открывается в окне браузера.

Отчет включает следующее оглавление. Щелкните гиперссылку, чтобы перейти к разделу отчета.

В оглавлении щелкните Summary для отображения главы Сводка отчета.

В главе Сводка (Summary) содержится информация о модели и статусе целей - удовлетворено или нет.

В оглавлении щелкните Analysis Information для отображения главы «Информация об анализе».

В главе «Информация об анализе» содержится информация о:

Анализируемая модель.

Опции, заданные для анализа.

Аппроксимация программного обеспечения, выполненного во время анализа.

В оглавлении щелкните Test Objectives Status для отображения главы «Test Targets Status» отчета.

Эта таблица показывает, что анализ удовлетворил обе цели теста, связанные с блоком Switch в ex_generate_test_cases_example модель, для которой она сгенерировала два тестовых случая.

В столбце Test Case таблицы щелкните 2 для отображения раздела «Тестовый случай 2».

В этом разделе приводится подробная информация о тестовом случае, который был создан при анализе для достижения цели в модели. Этот тестовый случай достигает тестовой цели 1, когда блок коммутатора передает свой третий вход в свой выходной порт. В частности, программное обеспечение определяет, что значение -1 для управляющего сигнала блока переключения заставляет блок пропускать свой третий вход в качестве выходного сигнала блока.

Дополнительные сведения о HTML-отчетах см. в разделе Отчеты Simulink Design Verifier.

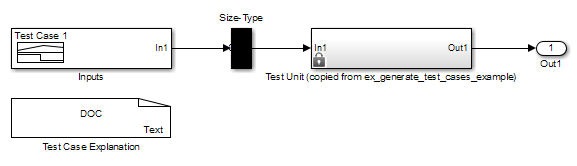

Чтобы создать модель ремня безопасности с прецедентами, которые удовлетворяют испытательные цели в Вашей модели в окне Резюме Результатов Свидетельства Дизайна Simulink, нажимают модель ремня безопасности Create.

Программа создает модель кабельных трасс с именем ex_generate_test_cases_example_harness.

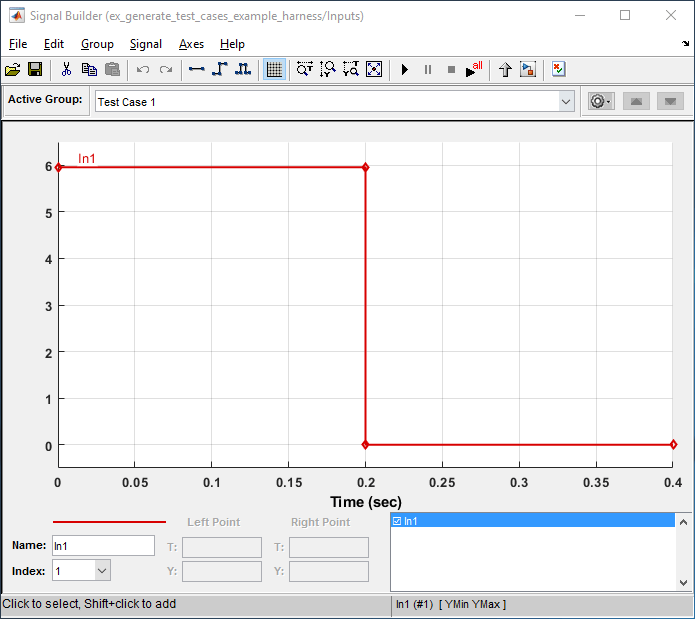

Блок построителя сигналов с именем «Входы» содержит тестовые примеры. Дважды щелкните блок «Inputs» для просмотра тестовых примеров. Из блока Signal Builder можно смоделировать модель с помощью тестовых примеров и создать отчет о покрытии модели, как описано в разделе Моделирование тестов и создание отчета о покрытии модели.

Дополнительные сведения о модели кабельных трасс см. в разделе Simulink Design Verifier Модели кабелей.

Если анализ генерирует множество тестовых примеров. При наличии большой модели анализ может привести к созданию модели кабельных трасс, содержащей большое количество тестовых примеров.

Чтобы создать меньше тестовых случаев:

Задайте для параметра Оптимизация набора тестов значение LongTestcases.

Повторите анализ.

В LongTestcases оптимизация, анализ генерирует меньше, но больше тестовых случаев, каждый из которых удовлетворяет нескольким целям теста.

Чтобы смоделировать модель электрического жгута с использованием созданных тестовых примеров в модели электрического жгута:

В модели кабельных трасс дважды щелкните блок Входы (Inputs), чтобы открыть диалоговое окно Конструктор сигналов (Signal Builder).

В диалоговом окне Signal Builder нажмите кнопку Run all.

![]()

Программа моделирует модель кабельных трасс с использованием обоих тестовых примеров, собирает информацию о покрытии модели и отображает отчет о покрытии. Отчет о покрытии указывает, что тестовые случаи фиксируют 100% -ное покрытие решений для ex_generate_test_cases_example модель.

Модель также можно моделировать без создания модели кабельных трасс. В окне журнала Simulink Design Verifier щелкните Simulate tests и создайте отчет об охвате модели.

Дополнительные сведения о покрытии модели см. в разделе Отчет о покрытии модели верхнего уровня (покрытие Simulink).

sldvData ФайлФайл данных Simulink Design Verifier - это MAT-файл, содержащий структуру с именем sldvData. В этой структуре хранятся все данные, собранные и полученные в ходе анализа. Файл данных можно использовать для проведения собственного анализа или создания пользовательского отчета.

Чтобы просмотреть файл данных, щелкните имя файла данных в окне журнала, в этом примере: ex_generate_test_cases_example_sldvdata.mat. При щелчке по имени файла копия sldvData объект создается в рабочей области MATLAB ® для просмотра и обработки данных.

Дополнительные сведения о файлах данных Simulink Design Verifier см. в разделе Файлы данных Simulink Design Verifier.

Пока модель остается открытой, можно просмотреть результаты последнего анализа Simulink Design Verifier в окне Сводка результатов (Results Summary).

На вкладке «Проверка проекта» в разделе «Результаты проверки» нажмите кнопку «Загрузить более ранние результаты» или «Сводка результатов» для просмотра результатов.

Для любого анализа Simulink Design Verifier эти задачи можно выполнить в окне Сводка результатов (Results Summary).

| Задача | Для получения дополнительной информации |

|---|---|

Выделите результаты анализа в модели. | Выделенные результаты на модели |

Создайте подробный отчет об анализе. | Отчеты Simulink Design Verifier |

Создайте модель электрического жгута или, если модель электрического жгута уже существует, откройте ее. Если во время анализа тестовые примеры не были созданы, эта опция недоступна. | Модели кабелей Simulink Design Verifier |

Просмотрите файл данных. | Файлы данных Simulink Design Verifier |

Просмотрите файл журнала. | Файлы журнала Simulink Design Verifier |

После закрытия модели просмотр результатов анализа невозможен.

Блок тестовых условий можно использовать для ограничения сигналов в модели определенными значениями во время анализа.

В командной строке MATLAB введите sldvlib для отображения библиотеки Simulink Design Verifier.

Откройте подзаголовок «Цели и ограничения».

Скопируйте блок тестовых условий в модель, перетащив его из библиотеки Simulink Design Verifier в окно модели.

В окне модели вставьте блок Test Condition между блоками Inport и Switch.

Дважды щелкните блок «Тестовое условие», чтобы получить доступ к его атрибутам.

Откроется диалоговое окно «Параметры блока условий тестирования».

В поле «Значения» введите [-0.1, 0.1]. При создании тестовых примеров для этой модели анализ ограничивает значения сигнала, вводя порт управления блоком коммутатора в указанный диапазон.

Нажмите кнопку «ОК», чтобы сохранить изменения и закрыть диалоговое окно «Параметры блока условий тестирования».

Сохранение модели как ex_generate_test_cases_with_tc_block и держать его открытым.

Проанализируйте ex_generate_test_cases_with_tc_block модель с блоком тестовых условий. Чтобы проверить, как блок тестовых условий влияет на генерацию теста, сравните результат этого анализа с результатом, полученным в примере анализа модели.

На вкладке Design Verifier щелкните Generate Tests (Генерировать тесты).

Программа Simulink Design Verifier отображает окно журнала и начинает анализ модели для создания тестовых примеров. По завершении анализа в окне Сводка результатов (Results Summary) отображаются опции для просмотра результатов.

В окне Сводка результатов (Results Summary) щелкните Отчет HTML (HTML Report).

Чтобы начать просмотр отчета, в оглавлении щелкните Summary.

В главе Summary (Сводка) указано, что Simulink Design Verifier удовлетворяет двум целям тестирования в модели.

В оглавлении щелкните Analysis Information. Перейдите к нижней части этой главы в раздел «Ограничения».

В этом разделе приводится список блоков тестовых условий, добавленных для ограничения значения управляющего сигнала блока переключения интервалом [-0.1, 0.1].

В оглавлении щелкните Test Objectives Status.

Эта таблица показывает, что Simulink Design Verifier удовлетворил обе цели тестирования для блока Switch в двух созданных тестовых примерах.

В столбце Test Case таблицы щелкните 1.

В этом разделе содержится подробная информация о тестовом примере, созданном программным обеспечением для достижения цели модели. Этот тестовый случай достигает тестовой цели 1, когда блок коммутатора передает свой третий вход в свой выходной порт. Хотя блок Test Condition ограничивает область входных сигналов интервалом [-0.1, 0.1], программное обеспечение определяет, что значение -0.1 для управляющего сигнала Switch block удовлетворяет этой цели.

Чтобы подтвердить, что тестовый случай достигает 100% покрытия принятия решения, откройте модель электрического жгута.

Дважды щелкните блок «Входы», чтобы открыть диалоговое окно «Конструктор сигналов».

В диалоговом окне Signal Builder нажмите кнопку Run all.

![]()

Программа Simulink моделирует модель кабельных трасс с использованием обоих тестовых примеров, собирает информацию о покрытии модели и отображает отчет о покрытии. В разделе Отчет (Summary) указывается, что Simulink Design Verifier создал тестовые примеры, которые обеспечивают полный охват принятия решений для примерной модели.

Если в результате анализа возникает ошибка The model is contradictory in its current configuration, программа обнаружила противоречие в модели и не может проанализировать модель.

Может возникнуть противоречие, если в модели имеются блоки Test Objective с неверными параметрами. Например, противоречие может быть целью, которая утверждает, что сигнал должен быть между 0 и 5, когда сигнал является константой 10.

Если программное обеспечение обнаруживает противоречие, все предыдущие результаты признаются недействительными, и программное обеспечение сообщает, что некоторые из целей не могут быть выполнены.