В этом примере показана проверка подсистемы путем обеспечения того, что выходные данные кода SIL соответствуют данным подсистемы модели. Вы создаете жгут проверки SIL, собираете результаты моделирования и сравниваете результаты с помощью инспектора данных моделирования. Можно применить аналогичный процесс для проверки процессора в цикле (PIL).

Симуляция SIL позволяет проверить поведение производственного исходного кода на хост-компьютере. С помощью моделирования PIL можно проверить скомпилированный объектный код, который планируется развернуть в производстве. Код объекта PIL можно запустить на реальном целевом оборудовании или на симуляторе набора команд.

При наличии лицензии Embedded Coder ® можно создать тестовый электрический жгут в режиме SIL или PIL для проверки модели. Можно сравнить результаты блока SIL или PIL с результатами модели и собрать метрики, включая время выполнения и охват кода модели. Покрытие блоков SIL или PIL невозможно. Используя тестовый жгут для проверки SIL и PIL, можно:

Управление кабельным жгутом с помощью модели. При создании тестового электрического жгута создается блок SIL. Тестовый жгут связан с проверяемым компонентом. Тестовый электрический жгут можно сохранить в главной модели.

Используйте встроенные инструменты для следующих рабочих процессов:

Проверка эквивалентности блоков SIL или PIL

Обновление блока SIL или PIL в соответствии с последней конструкцией модели

Просмотр и сравнение зарегистрированных данных и сигналов с помощью диспетчера тестов и инспектора данных моделирования.

При создании теста эквивалентности, сравнивающего нормальный режим и режим моделирования SIL или PIL, для тестирования каждого режима используется отдельный тестовый жгут. Однако при тестировании эквивалентности атомной подсистемы или блока модели можно использовать один тестовый жгут как для нормального моделирования, так и для моделирования SIL или PIL. Сведения о том, когда один электрический жгут используется для испытаний эквивалентности атомной подсистемы, см. в разделе Создание тестов и тестирование электрических жгутов для компонента или модели.

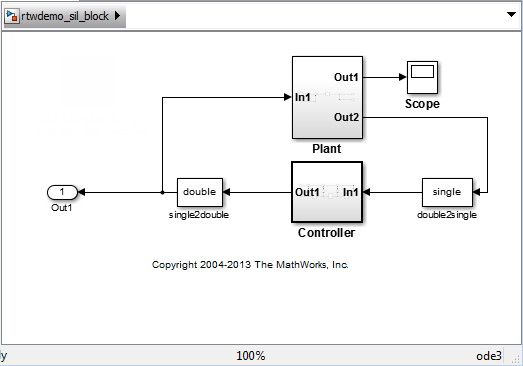

В этом примере моделируется система контроллера с замкнутым контуром. Контроллер регулирует производительность установки.

Создайте проверочный электрический жгут SIL, используя данные, которые регистрируются в системе контроллер-завод с замкнутым контуром. Управляющая подсистема регулирует выходную мощность установки. Для этого примера необходима лицензия Embedded Coder. Другой способ создания кабеля SIL - мастер создания теста для компонента модели (см. раздел «Создание тестов и тестовых жгутов для компонента или модели» и «Создание и выполнение теста»).

Откройте пример модели путем ввода

rtwdemo_sil_block

Сохранение копии модели с использованием имени controller_model в новой папке, в доступном для записи расположении по пути MATLAB.

Включение регистрации сигналов для модели. В командной строке введите

set_param(bdroot,'SignalLogging','on','SignalLoggingName',... 'SIL_signals','SignalLoggingSaveFormat','Dataset')

Щелкните правой кнопкой мыши сигнал в поле Controller port In1 и выберите Properties. В диалоговом окне «Свойства сигнала» в поле «Имя сигнала» введите controller_model_input. Выберите Log signal data и нажмите OK.

Щелкните правой кнопкой мыши сигнал из порта контроллера Out1 и выберите Properties. В диалоговом окне «Свойства сигнала» в поле «Имя сигнала» введите controller_model_output. Выберите Log signal data и нажмите OK.

Моделирование модели.

Получайте записанные сигналы из выходных данных моделирования в рабочую область. В командной строке введите

out_data = out.get('SIL_signals');

control_in1 = out_data.get('controller_model_input');

control_out1 = out_data.get('controller_model_output');Создайте тестовый электрический жгут в контуре программного обеспечения. Щелкните правой кнопкой мыши подсистему контроллера и выберите «Тестовый кабель» > «Создать тестовый кабель (контроллер)».

Задайте свойства электрического жгута:

Имя: SIL_harness

Источники и поглотители: Inport и Outport

После создания выберите «Открыть электрический жгут»

Дополнительные свойства - режим проверки: Software-in-the-loop (SIL)

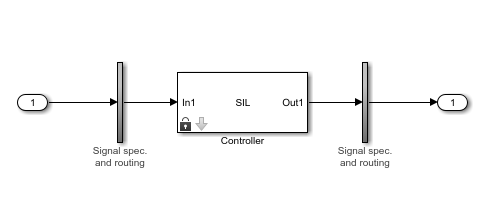

Нажмите кнопку OK. Результирующий тестовый жгут имеет блок SIL.

Сконфигурируйте и смоделируйте кабель проверки SIL для подсистемы контроллера.

Настройте тестовый электрический жгут для импорта введенных значений контроллера. На верхнем уровне тестового электрического жгута в диалоговом окне Параметры конфигурации модели (model Configuration Parameters) на панели Импорт/экспорт данных (Data Import/Export) выберите Ввод (Input). Войти control_in1.Values в качестве входных данных и нажмите кнопку OK.

Включение регистрации сигналов для тестового жгута. В командной строке введите

set_param('SIL_harness','SignalLogging','on','SignalLoggingName',...

'harness_signals','SignalLoggingSaveFormat','Dataset')Щелкните правой кнопкой мыши выходной сигнал блока SIL и выберите «Свойства». В диалоговом окне «Свойства сигнала» в поле «Имя сигнала» введите SIL_block_out. Выберите Log signal data и нажмите OK.

Смоделировать электрический жгут.

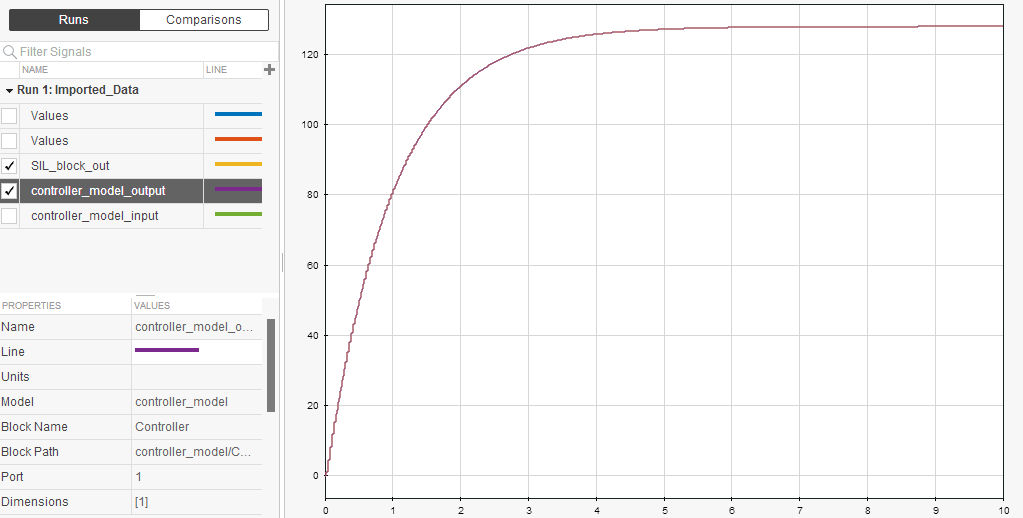

Сравните выходы для проверочного жгута и подсистемы контроллера.

В модели тестового электрического жгута в разделе «Результаты проверки» щелкните Инспектор данных (Data Inspector

), чтобы открыть Инспектор данных моделирования![]() (Simulation Data Inspector).

(Simulation Data Inspector).

В Инспекторе данных моделирования щелкните Импорт. В диалоговом окне «Импорт».

Задать импорт из в: Base workspace.

Задайте для параметра Импорт значение: New Run.

В разделе Данные для импорта (Data to import) выберите Имя сигнала (Signal Name), чтобы импортировать данные из всех источников.

Щелкните Импорт (Import).

Выберите SIL_block_out и controller_model_out сигналы на панели Runs окна инспектора данных.

На диаграмме отображаются два перекрывающихся сигнала. Этот результат предполагает эквивалентность кода SIL. Можно распечатать различия сигналов с помощью вкладки Сравнить (Compare) в SDI и выполнить более подробный анализ для проверки. Дополнительные сведения см. в разделе Сравнение данных моделирования.

Закройте окно тестового электрического жгута. Вернитесь к основной модели. Значок![]() на блоке контроллера указывает, что кабель SIL связан с подсистемой.

на блоке контроллера указывает, что кабель SIL связан с подсистемой.