В Диспетчере испытаний мастер «Создать тест для компонента» создает внутренний тестовый кабель и тестовый пример для модели или компонента в модели. Компоненты, для которых можно создать тестовые жгуты, включают подсистемы, диаграммы Stateflow ® и блоки модели. Полный список компонентов, поддерживаемых тестовыми жгутами, см. в разделе Тестовый жгут и связь модели.

В мастере необходимо указать:

Модель для тестирования.

Тестируемый компонент, если не тестируется целая модель.

Тестовые входы.

Тип теста, выполняемого для компонента.

Сохранение тестовых данных в MAT-файле или Excel ®. Дополнительные сведения об использовании файлов Excel в диспетчере тестов см. в разделе Формат данных контрольного примера в Excel.

Пример использования мастера см. в разделе Создание и запуск теста Back-to-Back.

Перед запуском мастера проверьте модель.

При тестировании компонента можно выбрать этот компонент в модели перед открытием мастера для автоматического заполнения полей модели и компонента.

При тестировании кода для атомной подсистемы с помощью теста эквивалентности, использующего режим «программное обеспечение в цикле» (SIL) или «процессор в цикле» (PIL), убедитесь, что подсистема уже сгенерировала код.

При тестировании кода, созданного для повторно используемой библиотечной подсистемы, перед открытием мастера Create Test for Component убедитесь, что подсистема имеет определенные функциональные интерфейсы и что библиотека уже создала код. Сведения о повторно используемых библиотечных подсистемах, функциональных интерфейсах и сгенерированном коде см. в разделе Создание библиотечного кода для повторно используемых библиотечных подсистем (встроенный кодер). Для проверки созданного кода необходимо иметь лицензию Embedded Coder ®.

Примечание

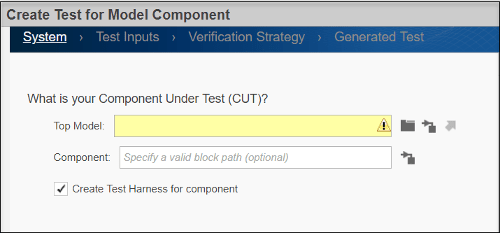

Чтобы открыть мастер создания теста для компонента, в диспетчере тестов выберите New > Test for Model Component.

На первой странице мастера нажмите кнопку Использовать текущую модель![]() , чтобы заполнить поле Верхняя модель.

, чтобы заполнить поле Верхняя модель.

Затем, если вы тестируете:

Вся модель, оставьте поле Компонент пустым.

Один компонент и выбранный компонент в модели перед открытием мастера нажмите кнопку Использовать текущий выбранный компонент модели (Use current selected model component![]() ), чтобы заполнить поле Компонент (Component). В противном случае введите имя компонента.

), чтобы заполнить поле Компонент (Component). В противном случае введите имя компонента.

Компонент в блоке «Ссылка на модель» не требуется указывать блок «Ссылка на модель» в качестве верхней модели. В качестве верхней модели используйте имя модели, содержащей блок «Ссылка на модель».

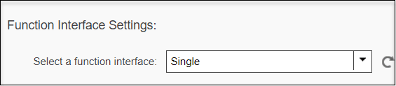

Повторно используемая библиотечная подсистема, имеющая функциональный интерфейс, отображается параметр «Параметры функционального интерфейса». Выберите функциональный интерфейс, для которого требуется создать тест.

Повторно используемые библиотеки содержат компоненты и подсистемы, которые могут использоваться совместно с несколькими моделями. Можно совместно использовать код, созданный подсистемами, если эти подсистемы находятся на верхнем уровне библиотеки многократного использования и имеют функциональные интерфейсы. Функциональные интерфейсы определяют параметры входа и выхода подсистемы.

Чтобы проверить всю модель без создания тестового электрического жгута, снимите флажок «Создать тестовый электрический жгут для компонента». При тестировании определенного компонента в модели тестовый электрический жгут создается автоматически, и опция «Создать тестовый электрический жгут для компонента» не отображается.

Примечание

Для модели с функцией экспорта тестовый электрический жгут автоматически создает блок тестовой последовательности.

Нажмите кнопку Далее, чтобы перейти на следующую страницу мастера.

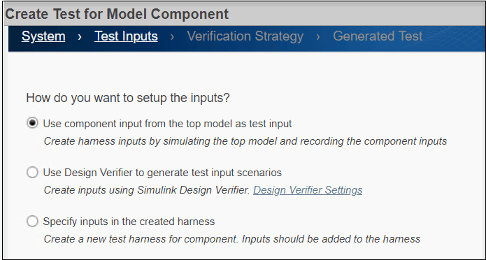

На странице Тестовые входы выберите способ получения тестовых входов.

Использовать ввод компонентов из верхней модели в качестве тестового ввода (Use component input from the top model as test input) - моделирование модели и запись входных данных в компонент. Затем используйте эти входные данные в качестве входных данных для созданного тестового электрического жгута. Используйте этот параметр для отладки.

Примечание

При тестировании подсистемы с функциональными вызовами невозможно получить входные данные путем моделирования модели, поскольку функциональные вызовы не могут быть зарегистрированы. Для получения входных данных используйте одну из двух других опций.

Команда Design Verifier используется для создания сценариев ввода тестовых данных - создание входных данных тестовых кабельных трасс в соответствии с требованиями к покрытию тестовых данных с помощью Simulink ® Design Verifier™. Этот параметр отображается, только если установлен Simulink Design Verifier.

Задать входные данные в созданном электрическом жгуте - после создания электрического жгута мастером откройте электрический жгут в Диспетчере испытаний и вручную задайте входные данные электрического жгута. Эта опция не отображается, если не создать тестовый электрический жгут.

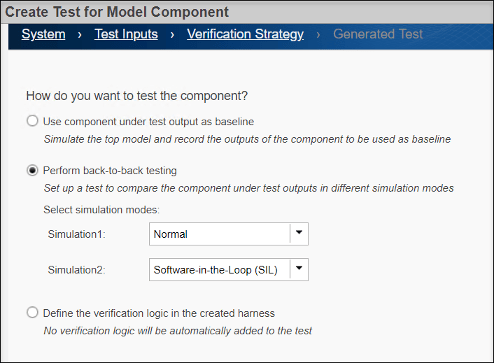

На странице «Стратегия проверки» выберите способ тестирования компонента.

Использовать тестируемые выходные данные компонента в качестве базовой линии - моделирование модели и запись выходных данных компонентов, которые используются в качестве базовой линии.

Выполнять обратное тестирование - сравнивать результаты выполнения компонента в двух различных режимах моделирования. Для каждого моделирования выберите режим в раскрывающемся меню. Для проведения тестирования SIL на атомной или многоразовой библиотечной подсистеме, подсистема или библиотека, содержащая подсистему, должна уже иметь сгенерированный код.

Если на вкладке «Тестовые входы» выбран параметр «Использовать программу Design Verifier» для создания сценариев тестового ввода, то Simulation2 к Software-in-the-Loop (SIL) или Processor-in-the-Loop (PIL), мастер отображает параметр Задать цель покрытия модели как расширенный MCDC. Усовершенствованный MCDC расширяет охват MCDC, генерируя тестовые примеры, которые избегают маскирования эффектов от нисходящих блоков. См. раздел Расширенное покрытие MCDC в программе Simulink Design Verifier (Simulink Design Verifier).

Определить логику проверки в созданном электрическом жгуте - после создания электрического жгута мастером откройте электрический жгут. Вручную задайте логику проверки с помощью блока «Тестовая последовательность» или «Тестовые оценки» в создаваемом кабельном жгуте. Кроме того, в созданном тестовом случае можно использовать логические и временные оценки или пользовательские критерии. Эта опция не отображается, если выполняется тестирование модели верхнего уровня и не создается тестовый электрический жгут.

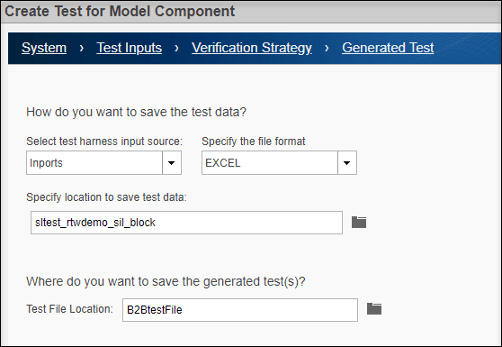

На странице Сгенерированный тест (Generated Test) выберите формат для сохранения тестовых данных и укажите имя файла для сгенерированных тестов.

Выбрать источник ввода тестового электрического жгута (Select test harness input source) - выбор способа применения входных данных, сгенерированных средством Design Verifier, к тестовому электрическому жгуту. Эта опция появляется только в том случае, если на вкладке «Тестовые входы» выбран параметр «Использовать программу Design Verifier» для создания сценариев тестового ввода.

Inports - создание тестового электрического жгута с блоками ввода в качестве источника.

Signal Editor - создание тестового электрического жгута с редактором сигналов в качестве источника, содержащего входные сценарии, созданные программой Design Verifier.

Укажите формат файла - укажите тип файла для сохранения данных. Эта опция появляется только при выборе Inports в качестве источника ввода.

Excel - сохранение тестовых входных данных, выходных данных и параметров на одном листе в файле электронной таблицы Excel. Для тестов с несколькими итерациями каждая итерация находится на отдельном листе. Дополнительные сведения об использовании файлов Excel в диспетчере тестов см. в разделе Формат данных контрольного примера в Excel.

MAT - Сохраняет входные и выходные данные в отдельных файлах MAT. Для тестов, использующих Simulink Design Verifier, мастер сохраняет входные данные и параметры в одном файле, а выходные данные - в файле опорной структуры.

Укажите расположение для сохранения тестовых данных - укажите полный путь к файлу. Кроме того, можно использовать имя файла по умолчанию и расположение, которое сохраняет sltest_<model name> в текущей рабочей папке. Этот параметр доступен только для файлов формата Excel. Файлы MAT сохраняются в расположении по умолчанию, указанном в настройках конфигурации модели.

Расположение тестового файла (Test File Location) - укажите полный путь для сохранения созданных тестовых файлов. Кроме того, можно использовать имя файла по умолчанию: sltest_<model name>_tests. Файл сохраняется в текущей рабочей папке. Это поле появляется только в том случае, если перед открытием мастера в диспетчере тестов не был открыт тестовый файл.

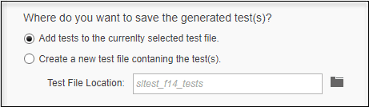

Если перед открытием мастера в диспетчере тестов был открыт тестовый файл, вместо параметра «Расположение тестового файла» отображаются следующие параметры:

Добавить тесты в текущий выбранный тестовый файл - созданные тесты добавляются в тестовый файл, выбранный на панели «Обозреватель тестов» Диспетчера тестов при открытии мастера.

Создать новый тестовый файл, содержащий тесты - для тестов создается новый тестовый файл. Он отображается на панели «Обозреватель тестов» Диспетчера тестов.

Нажмите кнопку Готово (Done), чтобы создать тестовый жгут и тестовый пример. Тестовый электрический жгут не создается, если выполняется тестирование всей модели и на первой вкладке мастера снят флажок «Создать тестовый электрический жгут».

Затем откроется Диспетчер тестов (Test Manager) с тестовым примером на панели «Обозреватель тестов» (Test Browser) и, если тестовый электрический жгут был создан, именем тестового электрического жгута в поле «Электрический жгут» (Harness) раздела «Тестируемая система» (System Under Test). Тестовый случай назван <model name>_Harness<#>.

Примечание

Если модель имеет существующий внешний электрический жгут, мастер создает дополнительный внешний тестовый электрический жгут для тестируемого компонента. Если электрический жгут отсутствует или существует внутренний электрический жгут, мастер создает внутренний тестовый электрический жгут.

При тестировании кода для атомной подсистемы или блока модели с использованием теста эквивалентности и на вкладке «Стратегия проверки» установите для Simulation2 значение Software-in-the-Loop (SIL) или Processor-in-the-Loop (PIL)Мастер создает только один тестовый жгут как нормального, так и SIL или режима моделирования PIL. Для других тестов эквивалентности мастер создает два жгута, по одному для каждого режима моделирования. Для следующих типов подсистем и конфигураций модели мастер создает два тестовых жгута, даже если подсистема является атомной.

Виртуальные подсистемы

Вызов функции, Для каждой подсистемы, Если действие, S-функция, Инициализация функции, Завершение функции и Сброс функции

Диаграммы статофлоу

Подсистемы, в которых ERTFilePackagingFormat свойство имеет значение Compact если код подсистемы имеет PreserveStaticInFcnDecls установить в значение on.

AUTOSAR

Подсистемы, генерирующие встроенный код, например подсистемы, в которых RTWSystemCode свойство не является Nonreusable function или Reusable function).

Подсистемы, содержащие ссылочные модели, S-функции, считывание хранилища данных или блоки записи хранилища данных

Подсистемы, имеющие виртуальные шины на своем интерфейсе

Подсистемы, включающие покрытие кода LDRA или BullsEye

Подсистемы, включающие регистрацию сигналов