Приложение SoC состоит из одного или нескольких алгоритмов. Когда алгоритм передает данные другому алгоритму, данные представляются в Simulink ® в виде сигнальной линии. Для поведенческих моделей передача данных является мгновенной.

На этой диаграмме показана поведенческая модель пути данных между двумя алгоритмами.

В физическом мире алгоритмы могут находиться на двух отдельных устройствах, и передача данных не происходит мгновенно. Кроме того, алгоритмы могут работать с различной скоростью и поэтому требуют буферизации и управляющей логики для квитирования. Например, простое рукопожатие, такое как «данные действительны» от производителя данных и «готовы принять данные» от потребителя, служит логикой управления.

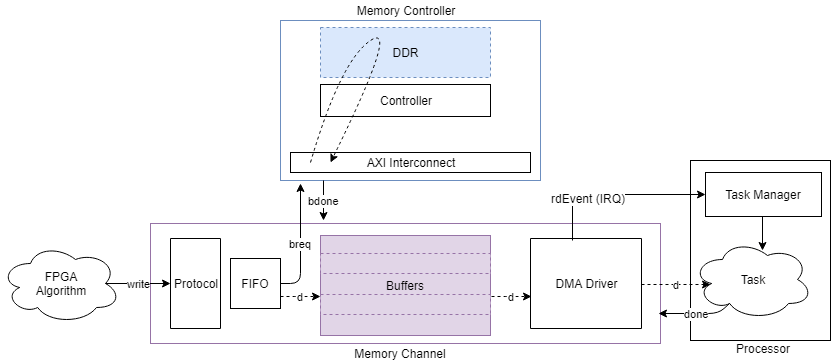

Если один элемент обработки выполняется в FPGA или ASIC, а следующий элемент обработки выполняется на встроенном процессоре, то простая сигнальная линия представляет собой не только сложный аппаратный канал данных. Передача данных также представляет обработчик прерываний процессора, планировщик задач операционной системы и стек драйверов программного обеспечения.

В SoC Blockset™ вы моделируете передачу данных и протоколы квитирования через общую память. Используйте блок канала памяти для внешней памяти или блок канала регистра для регистров.

Блок канала памяти представляет собой абстракцию в сложный канал данных через внешнюю память и поддерживает различные протоколы квитирования. Это облегчает усовершенствование связи между элементами обработки от мгновенного безпротокольного провода до полного соединения прямого доступа к памяти (DMA) между процессором и FPGA.

Добавив блок канала памяти, можно моделировать перемещение данных из одной части алгоритма в другую.

Блок обеспечивает модель коммуникационного конвейера. Канал также обеспечивает интерфейс сигнализации.

Протокол интерфейса зависит от того, где выполняется обработка. Алгоритм FPGA или ASIC может выполнять передачу данных с использованием стандартных протоколов, таких как AXI4-Stream или AXI4. Встроенный алгоритм CPU может использовать драйвер-интерфейс, экспортируемый в пользовательское пространство.

На этом рисунке показана модель канала передачи данных из алгоритма FPGA в алгоритм процессора.

Другие типы каналов памяти моделируют дополнительные общие пути данных через внешнюю память. Дополнительные сведения о конфигурациях канала памяти см. в разделе Канал памяти.

Устройство записи и устройство считывания соединены с памятью и запрашивают доступ к внешней памяти у контроллера памяти. Дополнительные сведения о блоке контроллера памяти см. в разделе Контроллер памяти.

Блок Register Channel представляет сериализацию чтения или записи процессора через общую шину конфигурации, такую как AXI-Lite.

Блок канала регистрации предоставляет модель синхронизации для передачи значений регистров между алгоритмами процессора и аппаратных средств через общую шину конфигурации. Используйте этот блок, когда процессор записывает команду или регистр конфигурации или когда процессор считывает регистр состояния.

Канал памяти | Зарегистрировать канал