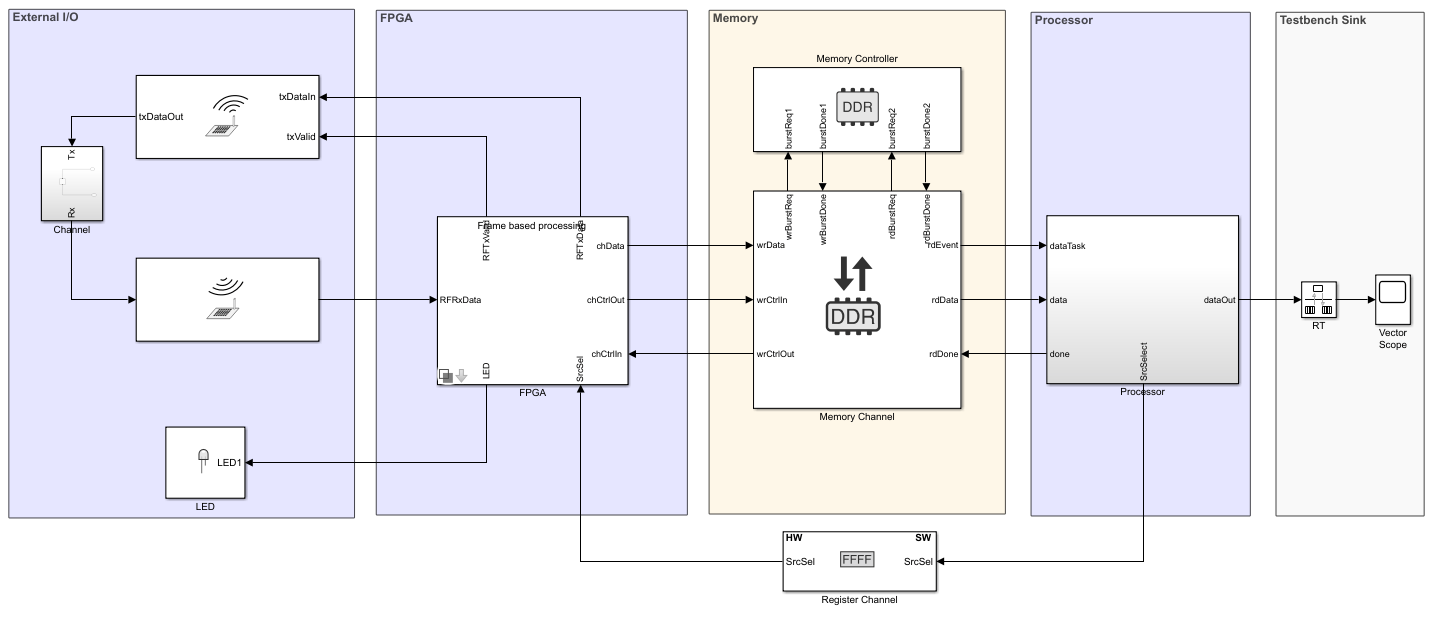

Шаблон программно-определяемого радио (SDR) предоставляет модель моделирования для эталонного проекта SoC, доступного из пакета поддержки Communications Toolbox™ Support Package для радио на базе Xilinx ® Zynq ®. Этот шаблон используется для моделирования всей эталонной конструкции и анализа влияния внутренних и внешних соединений на алгоритм SDR, например, поведение памяти и радиочастотного ввода-вывода.

Для начала работы с моделью SoC Blockset™ для проектирования системы SDR выполните действия по созданию модели SoC с использованием шаблона набора блоков SoC.

Набор средств связи

Пакет поддержки пакетов SoC для устройств Xilinx

Этот шаблон моделирует приемопередатчик SDR, состоящий из AD9361 блоков передатчика и приемника. Приемопередатчик соединяет радиочастотный канал с FPGA, который реализует алгоритм приемника и передатчика. Алгоритм FPGA включает в себя блок тестового источника, который генерирует синусоидальный сигнал и подает его на передатчик. Алгоритм FPGA также включает в себя алгоритм Tx, реализованный как простые проходные провода, и алгоритм Rx, реализованный как блок усиления. Регистр конфигурации srcSel моделируется в FPGA для выбора источника данных для алгоритма Rx. Процессор записывает регистр srcSel для выбора либо тестового источника из FPGA, либо радиочастотных данных из приемопередатчика. Этот регистр моделируется с использованием блока канала регистрации. Данные из алгоритма FPGA передаются процессору через блок канала памяти.

Используйте этот шаблон в качестве руководства и замените алгоритм приема и алгоритм передачи в FPGA и алгоритм процессора в процессоре собственными функциональными возможностями. Для параметра memory Channel Type установлено значение AXI4-Stream to software via DMA, которая моделирует передачу данных прямого доступа к памяти (DMA) через общую внешнюю память.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления (реализованные в шаблоне как проходной провод). Результаты моделирования можно просмотреть, дважды щелкнув блок «Vector Scope» в приемнике testbench.

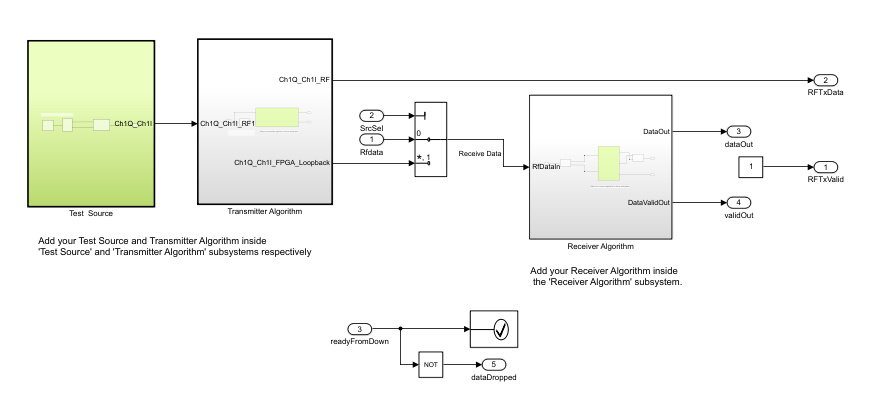

В MATLAB ® на вкладке Ярлыки проекта (Project Shortcuts) щелкните Открыть образец модели FPGA (Open FPGA sample model). Затем откройте обертку FPGA Tx-Rx Alg. Обратите внимание на три области, выделенные зеленым цветом. Эти области представляют код пользователя и расположены в блоке алгоритма приемника, в блоке алгоритма передатчика и в блоке тестового источника.

Модель FPGA содержит следующие разделы для изменения (выделены зеленым цветом):

Блок тестового источника - этот блок генерирует синусоидальный сигнал 10-kHz и передает его в алгоритм передатчика. Измените тестовый источник на необходимый или замените его альтернативным исходным блоком.

Подсистема алгоритма приемника - внутри подсистемы, выделенной зеленым цветом, с именем Rx Algorithm, имеется блок с меткой Algorithm. Алгоритм принимает данные I/Q как входные и выходные с действительным сигналом. Замените этот блок собственным алгоритмом Rx.

Алгоритм передатчика - внутри подсистемы, выделенной зеленым цветом и названной Tx Algorithm, алгоритм имеет вход от тестового источника и два выходных сигнала: один в радиочастотный канал и один в FPGA. Замените этот блок собственным алгоритмом Tx.

Чтобы включить согласованное поведение моделирования, на вкладке «Ярлыки проекта» щелкните «Открыть модель кадра FPGA» и повторите этот шаг.

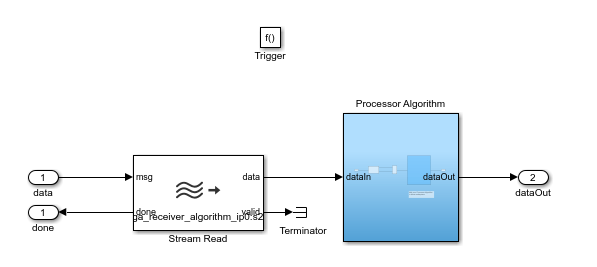

В MATLAB на вкладке Ярлыки проекта (Project Shortcuts) щелкните Открыть модель процессора (Open processor model). Подсистема, выделенная синим цветом, представляет код пользователя для алгоритма процессора. Откройте оболочку алгоритма процессора и замените внутренний блок алгоритма процессора (также выделенный синим цветом) требуемым алгоритмом.

Верхняя модель шаблона также включает в себя канал регистрации для связи между процессором и моделью FPGA. Используйте канал регистрации для конфигурирования модели FPGA или считывания и проверки регистров состояния. Блок канала регистрации в шаблоне включает в себя один регистр. Для добавления дополнительных регистров необходимо изменить параметры блока каналов регистров, алгоритм FPGA и алгоритм процессора:

Добавить регистры в канал регистров - дважды щелкните блок канала регистров, чтобы открыть маску блока и при необходимости добавить дополнительные регистры. Добавление регистров создает дополнительные порты в блоке канала регистрации. Дополнительные сведения см. в разделе Регистрация канала.

Добавление портов в модель процессора - переход к модели оболочки алгоритма процессора. Чтобы перейти к модели процессора, щелкните Открыть модель процессора (Open Processor model) на вкладке Ярлыки проекта (Project Shortcuts). Дважды щелкните обертку алгоритма процессора, чтобы изменить ее.

Для регистров записи добавьте выходной порт в модуль и добавьте логику для управления значением добавленного выходного порта. Для регистров считывания добавьте входной порт и логику для обработки информации, возвращаемой из регистра считывания. Из верхней модели подключите порт к блоку Register Channel.

Добавление портов в модель FPGA - переход к модели оболочки алгоритма FPGA. Для перехода к модели обработки FPGA/Frame щелкните Открыть образец модели FPGA (Open FPGA sample model) на вкладке Быстрые ссылки на проект (Project Shortcuts). Дважды щелкните обертку алгоритма FPGA, чтобы изменить ее.

Для регистров записи добавьте входной порт к модулю и логику для обработки информации, возвращаемой из регистра считывания. Для чтения регистров добавьте выходной порт и логику для управления значением добавленного выходного порта.

Для эквивалентного поведения при использовании варианта на основе образца Simulink ® повторите этот шаг для модели обработки на основе образца в оболочке FPGA.

Из верхней модели подключите новый порт к блоку Register Channel.