Декодировать код LDPC с использованием многоуровневого распространения убеждений с помощью алгоритма аппроксимации с минимальной суммой или нормализованного аппроксимации с минимальной суммой

Беспроводная панель инструментов HDL/обнаружение и исправление ошибок

Блок декодера NR LPDC реализует декодер с низкой плотностью контроля четности (LDPC) с аппаратными управляющими сигналами. Блок принимает проколотые значения логарифмического отношения правдоподобия (LLR), поток управляющих сигналов, номер базового графа и размеры подъема. Блок выводит декодированные биты, поток управляющих сигналов, размеры подъема и сигнал, который указывает, когда блок готов принять новые входы.

Этот блок предоставляет возможность реализовать многоуровневое распространение веры либо с помощью алгоритма аппроксимации с нормализованной минимальной суммой, либо с помощью алгоритма аппроксимации с минимальной суммой. Эта реализация соответствует реализации функции. nrLDPCDecode (5G Панель инструментов). Этот блок можно использовать для канального кодирования совместно используемых каналов нисходящей и восходящей линии связи и пейджингового канала в соответствии 5G новым стандартом радиосвязи (NR) TS 38.212 [1].

Блок декодера NR LDPC поддерживает скалярные и 64-элементные векторные входы столбцов. Блок поддерживает функцию раннего завершения, чтобы помочь улучшить эффективность декодирования и ускорить скорости сходимости при условиях с высоким отношением шумов сигнала (SNR). Блок позволяет декодировать множество кодовых скоростей, чтобы способствовать достижению высокой эффективности пропускной способности с высокой степенью гибкости кодовой скорости. Блок обеспечивает архитектуру, подходящую для генерации кода HDL и аппаратного развертывания. Дополнительные сведения см. в разделе Алгоритмы.

data - Входные значения LLRВходные значения логарифмического отношения правдоподобия (LLR), определенные как скаляр или вектор столбца размера 64.

Тип данных этого входа должен быть подписанным типом данных с фиксированной точкой с длиной слова от 4 до 16 бит. Дополнительные сведения о задании векторных входных данных см. в разделе Указание векторных входных данных.

Типы данных: int8 | int16 | fixed point

ctrl - Управляющие сигналы, сопровождающие поток пробsamplecontrol автобусУправляющие сигналы, сопровождающие поток проб, указанные как samplecontrol Шина включает в себя start, end, и valid управляющие сигналы, которые указывают границы кадра и достоверность выборок.

start - Указывает начало входного кадра.

end - Указывает конец входного кадра

valid - Указывает, что данные на порте входных данных являются допустимыми

Дополнительные сведения см. в разделе Пример шины управления.

Типы данных: bus

bgn - Номер базового графикаНомер базового графа, заданный как скаляр. Когда это значение равно 0, блок применяет bgn 1. Когда это значение равно 1, блок применяет bgn 2. Для получения дополнительной информации о bgn 1 и bgn 2 см. раздел 5.3.2 TS 38.212 [1].

Типы данных: Boolean

liftingSize - Размер входного подъемаВходной размер подъема, заданный как скаляр.

Для недействительной стоимости liftingSize блок отказывается от текущей структуры и ждет новой структуры. Для получения дополнительной информации о поддерживаемых значениях грузоподъемности см. раздел 5.3.2 TS 38.212 [1].

Типы данных: uint16

iter - количество итераций;Число итераций, указанное как целое число в диапазоне от 1 до 63.

Если задать значение iter больше 63, блок автоматически установит значение iter равным 8 и выполняет операцию декодирования.

Для активизации этого порта установите для параметра Decoding termination criteria значение Max и параметр Source для количества итераций для Input port.

Типы данных: uint8

numRows - Количество строкЧисло строк, указанное как скаляр.

При установке значения bgn в 0 блок поддерживает количество строк в диапазоне от 4 до 46. При установке значения bgn в 1блок поддерживает количество строк в диапазоне от 4 до 42.

Чтобы включить этот порт, выберите параметр Enable multiple code rates.

Типы данных: fixdt(0,6,0)

data - Декодированные биты выходных данныхДекодированные выходные биты данных, возвращенные как скаляр или вектор столбца размера 64.

Блок выводит биты данных в формате, аналогичном входным значениям LLR. Извлеките эти выходные биты данных в подобном формате для дальнейшей обработки.

Типы данных: Boolean

ctrl - Управляющие сигналы, сопровождающие поток пробsamplecontrol автобусУправляющие сигналы, сопровождающие поток проб, возвращаемые в виде samplecontrol Шина включает в себя start, end, и valid управляющие сигналы, которые указывают границы кадра и достоверность выборок.

start - Указывает начало выходного кадра.

end - Указывает конец выходного кадра

valid - Указывает, что данные порта выходных данных являются допустимыми

Дополнительные сведения см. в разделе Пример шины управления.

Типы данных: bus

liftingSize - Размер выходного подъемаВыходной размер подъема, возвращаемый как скаляр.

Типы данных: uint16

nextFrame - Готовность к новым вводамБлок устанавливает этот сигнал на 1 когда блок готов принять начало следующего кадра. Если блок принимает входной начальный сигнал, пока nextFrame имеет значение 0блок отбрасывает текущий кадр и начинает обработку новых данных.

Дополнительные сведения см. в разделе Использование выходного сигнала nextFrame.

Типы данных: Boolean

actIter - Фактическое число итерацийФактическое количество итераций, которое блок принимает для декодирования выходного сигнала, возвращаемого в виде скаляра.

Для активизации этого порта установите для параметра Decoding termination criteria значение Early.

Типы данных: uint8

parityCheck - Индикатор состояния проверки четностиИндикатор состояния проверки четности, возвращаемый как логический скаляр. Порт указывает состояние проверки четности после операции декодирования.

0 - Указывает, что проверка четности не выполнена

1 - Указывает, что проверка четности пройдена

Чтобы включить этот порт, выберите параметр Включить выходной порт проверки четности.

Типы данных: Boolean

Algorithm - Тип алгоритмаMin-sum (по умолчанию) | Normalized min-sumВыберите тип алгоритма. Дополнительные сведения см. в разделе Алгоритм (5G Toolbox).

Scaling factor - Коэффициент масштабирования0.75 (по умолчанию) | значения в диапазоне от 0,5 до 1, увеличенные на 0,0625Укажите коэффициент масштабирования.

Чтобы включить этот параметр, установите для параметра Algorithm значение Normalized min-sum.

Decoding termination criteria - Критерии прекращенияMax (по умолчанию) | EarlyВыберите критерии завершения декодирования.

Max - прекращает декодирование, когда блок достигает числа итераций, указанного в маске блока, или через входной порт итера.

Early - прекращает декодирование при выполнении всех проверок четности или при достижении блоком максимального количества итераций, предусмотренных в маске блока;

Source for number of iterations - Выбор источника для количества итерацийProperty (по умолчанию) | Input portВыберите источник для указания количества итераций.

Можно задать количество итераций с помощью входного порта или параметра.

Выбрать Property для включения параметра Количество итераций.

Выбрать Input port для активизации порта итера.

Чтобы включить этот параметр, установите для параметра Decoding termination criteria значение Max.

Number of iterations - количество итераций;8 (по умолчанию) | целое число в диапазоне от 1 до 63Укажите количество итераций.

Чтобы включить этот параметр, задайте для параметра Источник для числа итераций значение Property.

Maximum number of iterations - Максимальное число итераций8 (по умолчанию) | целое число в диапазоне от 1 до 63Укажите максимальное число итераций.

Чтобы включить этот параметр, установите для параметра Decoding termination criteria значение Early.

Enable multiple code rates - Несколько кодовых скоростейoff (по умолчанию) | onВыберите этот параметр, чтобы включить входной порт numRows для поддержки нескольких кодовых скоростей. Дополнительные сведения о нескольких кодовых скоростях см. в разделе Несколько кодовых скоростей.

Enable parity check output port - Состояние проверки на четностьoff (по умолчанию) | onВыберите этот параметр, чтобы включить выходной порт проверки четности для просмотра состояния проверки четности.

Входные данные вектора для блока должны быть указаны как вектор столбца размером 64. Необходимо ввести целое число ceil(liftingSize/64) тактовых циклов.

Общее число тактовых циклов, которые требуются блоку для приема кадра значений LLR для декодирования, равно n x ceil (liftingSize/64), где n - количество колонок в паритетной клетчатой матрице. n зависит от номера базового графа, заданного входным портом bgn. Если значение порта bgn равно0блок устанавливает n в 66. Если значение порта bgn равно 1блок устанавливает n в 50.

Эти разделы шоу, как блок принимает, вводят ценности LLR на основе liftingSize и bgn ценности порта.

Поскольку liftingSize ввел ценность 2 и входное значение bgn 0блок может принимать 132 LLR. В этом случае блок принимает первые два входных бита LLR в каждом такте и игнорирует остальные 62 элемента в этом такте. Общее число тактовых циклов, необходимых блоку для приема кадра значений LLR, равно 66.

Элементы Ln представляют биты LLR, а элементы X представляют пропущенные значения.

| Входные значения LLR | Количество тактовых циклов | |||||

|---|---|---|---|---|---|---|

| 1 тактовый цикл | 2 тактовых цикла | 3 тактовых цикла | 4 тактовых цикла | ... | 66 тактовых циклов | |

data[0] | L0 | L2 | L4 | L6 | ... | L130 |

data[1] | L1 | L3 | L5 | L7 | ... | L131 |

| ... | X | X | X | X | X | X |

data[63] | X | X | X | X | X | X |

Поскольку liftingSize ввел ценность 104 и входное значение bgn 0блок может принимать 6864 LLR. В этом случае блок принимает 104 значения LLR в двух тактах: 64 LLR в первом такте и 40 LLR во втором такте. Блок игнорирует оставшиеся 24 элемента во втором такте. Общее число тактовых циклов, необходимых блоку для приема входных значений LLR, составляет 132.

Элементы Ln представляют биты LLR, а элементы X представляют пропущенные значения.

| Входные значения LLR | Количество тактовых циклов | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 тактовый цикл | 2 тактовых цикла | 3 тактовых цикла | 4 тактовых цикла | ... | ... | 131 Тактовые циклы | 132 Тактовых цикла | |

data[0] | L0 | L64 | L104 | L168 | ... | ... | L6760 | L6824 |

data[1] | L1 | L65 | L105 | L169 | ... | ... | L6761 | L6825 |

| ... | ... | ... | ... | ... | ... | ... | ||

| ... | ... | L103 | ... | L207 | ... | ... | ... | L6863 |

| ... | ... | X | ... | X | ... | ... | ... | X |

data[63] | L63 | X | L167 | X | ... | ... | L6823 | X |

Коды NR LDPC могут поддерживать гибкие скорости кодирования на основе расширения матрицы контроля четности (PCM) для достижения высокой пропускной способности и удовлетворения требований к низкой задержке. Блок поддерживает множество кодовых скоростей путем изменения количества строк матрицы контроля четности.

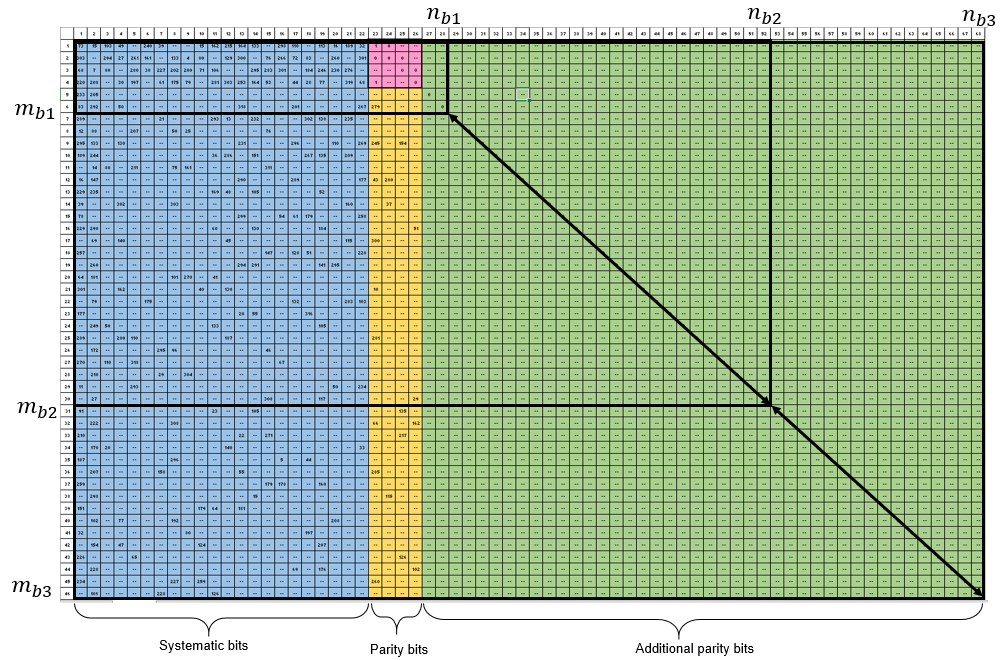

Для кодов LDPC базовая матрица контроля четности (Hb) является произведением количества строк (mb) и количества столбцов (nb) матрицы. Выходной сигнал (K) блока вычисляется как kb x Z, где Z - коэффициент расширения или размер подъема, который может находиться в диапазоне от 2 до 384, а kb равен 22 для значения bgn 0 и 10 для значения bgn 1 как определено в стандарте [1].

Входной размер (N) вычисляется как, nb x Z, где nb равен mb + kb.

На этом рисунке показана матрица контроля четности, помеченная указанным количеством строк и столбцов, которую можно использовать для вычисления кодовых скоростей блока. Кодовая скорость R вычисляется как, kb/( kb - 2 + mb) для указанного значения bgn. На этом рисунке значения nb1, nb2 и nb3 указывают количество столбцов для указанного значения bgn, а значения mb1, mb2 и mb3 указывают количество строк для указанного значения bgn.

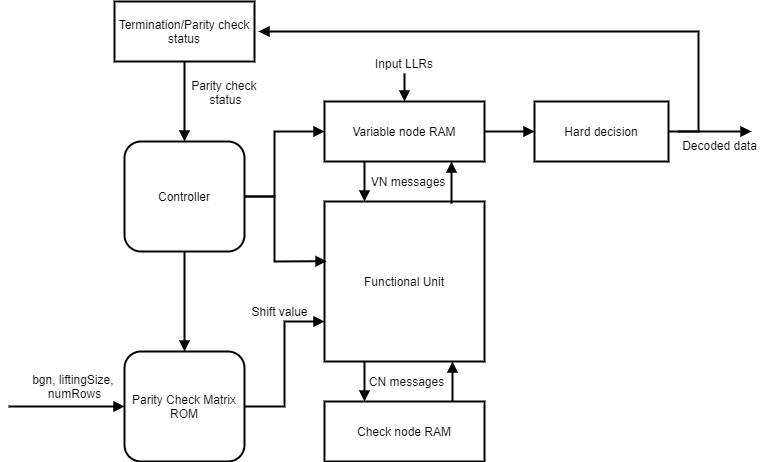

На этом рисунке показана блок-схема архитектуры блока декодера NR LDPC. Блок контроллера управляет подсчетом уровней и итераций процесса декодирования. Блок RAM переменного узла хранит сообщения переменного узла (VN), а блок RAM контрольного узла хранит сообщения контрольного узла (CN). Блок функционального блока вычисляет сообщения переменного узла (VN) и сообщения контрольного узла (CN) на основе многоуровневого распространения верования и либо алгоритма аппроксимации нормализованной минимальной суммы, либо алгоритма аппроксимации минимальной суммы. Блок состояния проверки окончания/проверки четности вычисляет проверки четности и предоставляет статус проверки четности после каждой итерации. Дополнительные сведения о алгоритмах декодирования см. в разделе Алгоритм (5G Toolbox).

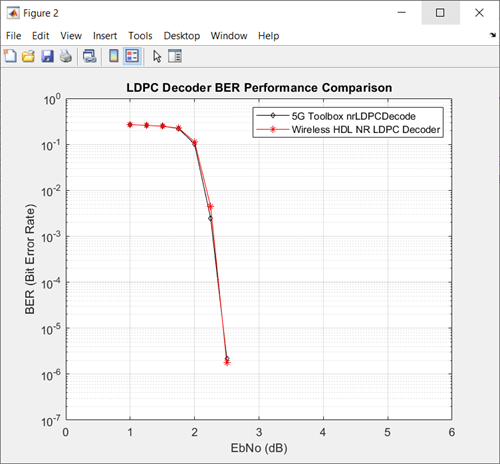

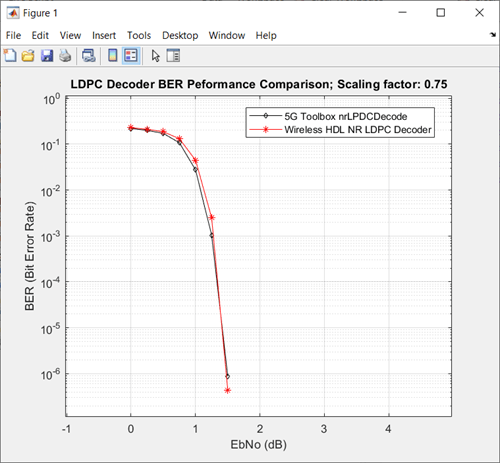

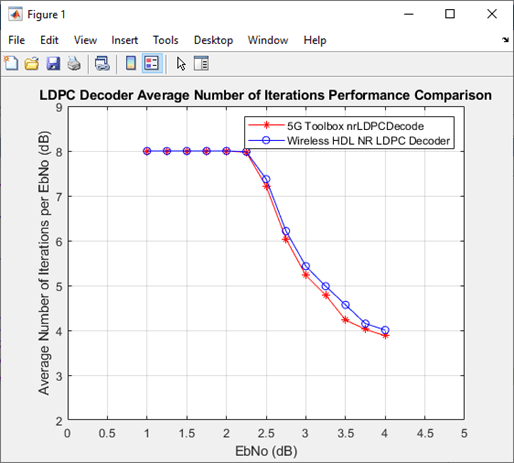

Реализация блока соответствует производительности функции nrLDPCDecode (5G Панель инструментов).

На этом графике показана производительность блока для 4-битного входа LLR при установке параметра Algorithm в значение Min-sum.

На этом графике показана производительность блока для 4-битного входа LLR при установке параметра Algorithm в значение Normalized min-sum .

Этот график показывает среднее количество итераций, принимаемых для декодирования данных на EbNo для 4-битного входа LLR при установке параметра Algorithm равным Min-sum и параметр Decoding termination criteria to Early.

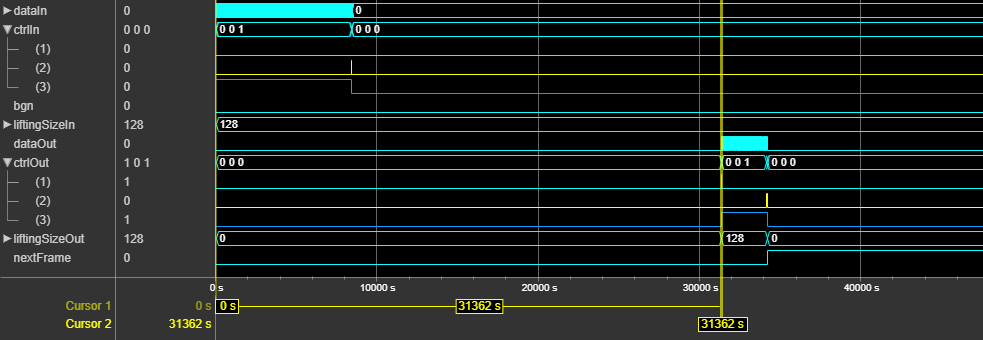

Время ожидания блока варьируется на основе ценностей bgn, liftingSize, и входных портов numRows и количества повторений. Поскольку задержка изменяется, используйте выходной порт управляющего сигнала nextFrame для определения готовности блока к новому входному кадру.

Задержка блока равна r x (t + (m x 8) x ceil(liftingSize/64) + t + m x (7 - ceil (liftingSize/64))) + (n x liftingSize) + 18. В этом вычислении r - количество итераций, n - количество столбцов в матрице проверки на четность, t - вдвое больше общего числа элементов, не являющихся -1 в матрице проверки на четность, m - количество строк в матрице проверки на четность, и d - задержки конвейера. Если выбран параметр Enable multiple code rates, d равно 26. В противном случае d равно 18.

На этом рисунке показан пример выходного сигнала блока декодера NR LDPC с задержкой. В этом случае bgn и входные ценности порта liftingSize установлены в 0 и 128, соответственно, и параметр Число итераций имеет значение 8. Задержка блока составляет 31 362 тактовых цикла.

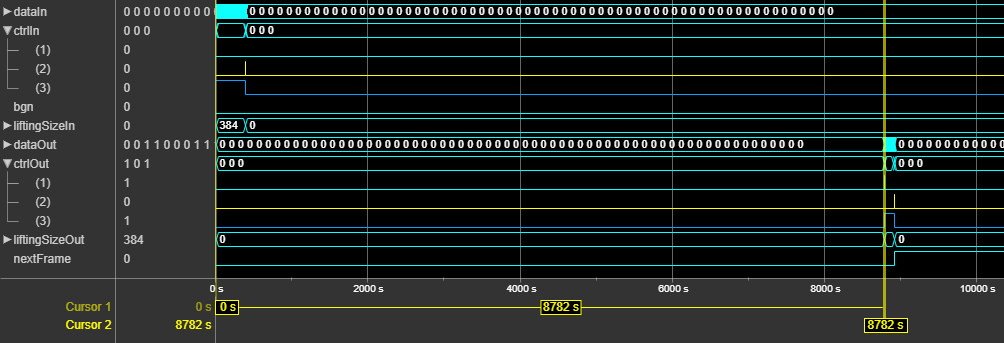

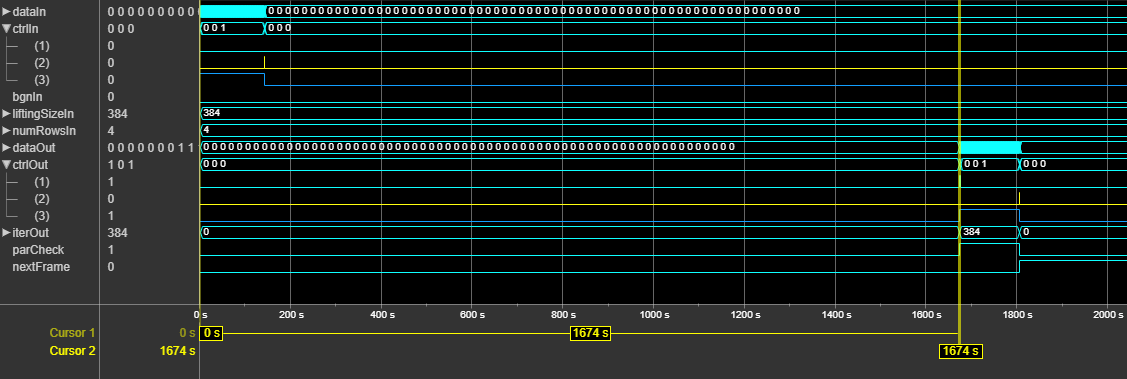

Для векторных входов задержка блока равна r x (t + (m x 9)) + n x (ceil (liftingSize/64)) + d. В этом вычислении r - количество итераций, n - количество столбцов в матрице проверки на четность, t - вдвое больше общего числа элементов, не являющихся -1 в матрице проверки на четность, m - количество строк в матрице проверки на четность, и d - задержки конвейера. Если выбран параметр Enable multiple code rates, d равно 26. В противном случае d равно 18.

На этом рисунке показан пример выходного сигнала блока декодера NR LDPC с задержкой. В этом случае bgn и входные ценности порта liftingSize установлены в 0 и 384, соответственно, и параметр Число итераций имеет значение 8. Задержка блока составляет 8782 тактовых цикла.

На этом рисунке показан пример выходного сигнала блока декодера NR LDPC с задержкой. В этом случае bgn, liftingSize, и входные ценности порта numRows установлены в 0, 384, и 4, соответственно, и параметр Число итераций имеет значение 8. Задержка блока составляет 1674 тактовых цикла.

Пропускная способность блока вычисляется как (cwLen/latency) x fmax. В этом расчете:

cwLen - длина кодового слова, которая равна kb x Z, где kb - 22 для значения bgn 0 и 10 для значения bgn 1.

latency - задержка блока для указанной конфигурации.

fmax - максимальная рабочая частота

Дополнительные сведения о вычислении задержки см. в разделе Задержка. Дополнительные сведения о максимальной рабочей частоте см. в разделе Производительность.

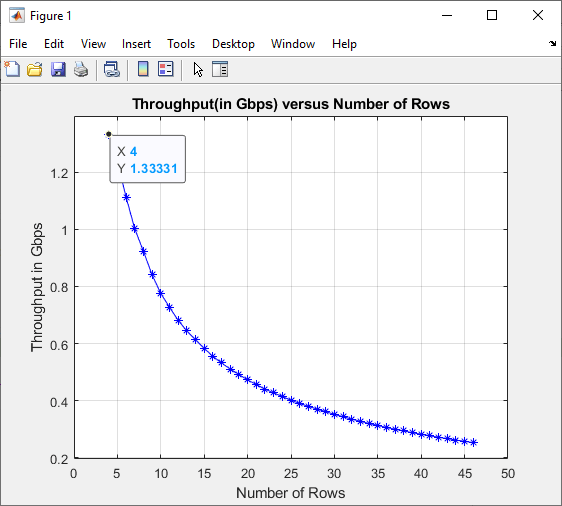

На этом графике показана пропускная способность по сравнению с количеством строк, указанным на входе блока, если для параметра Algorithm задано значение Min-sum, параметр Количество итераций для 8и входной порт bgn для 0.

Производительность синтезированного HDL-кода зависит от цели и вариантов синтеза. Он также изменяется в зависимости от типа алгоритма и длины слова входных значений LLR.

В этой таблице показаны результаты синтеза данных о ресурсах и производительности блока, если для параметра Algorithm установлено значение Min-sum, задайте для параметра Количество итераций значение 8и укажите входные значения LLR типа данных fixdt(1,4,0). Сгенерированный HDL предназначен для платы оценки Xilinx ® Zynq®Ultrascale+™ RASEoC.

| Входные данные | LUT среза | Регистры среза | Блокировать RAM | Максимальная частота в МГц |

|---|---|---|---|---|

| Скаляр | 45461 | 58331 | 192.5 | 291 |

| Вектор | 67410 | 75217 | 128.5 | 291.5 |

В этой таблице показаны результаты синтеза данных о ресурсах и производительности блока для векторного ввода при установке параметра Algorithm равным Min-sum, задайте для параметра Decoding termination criteria значение Max, задайте для параметра Количество итераций значение 8, выберите параметр Enable multiple code rates и укажите входные значения LLR типа данных fixdt(1,4,0). Созданный HDL предназначен для платы оценки Xilinx ZynqUltrascale + RASEoC.

| LUT среза | Регистры среза | Блокировать RAM | Максимальная частота в МГц |

|---|---|---|---|

| 72527 | 76002 | 128.5 | 264.2 |

[1] 3GPP TS 38.212. "НР; мультиплексирование и канальное кодирование. "Проект партнерства 3-го поколения; Техническая спецификация на сеть радиодоступа группы.

[2] Галлагер, Р. «Коды проверки четности с низкой плотностью». Сделки IEEE по теории информации 8, № 1 (январь 1962 года): 21-28. www.doi.org/10.1109/TIT.1962.1057683.

Этот блок поддерживает генерацию кода C/C + + для режимов ускорения Simulink ® и быстрого ускорения, а также для генерации компонентов DPI.

HDL Coder™ предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет единую архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

Невозможно создать HDL для этого блока в переустановляемой синхронной подсистеме (кодере HDL).

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.