Некоторые модели требуют, чтобы вы знали, сколько времени требуется для данных в одном фрагменте модели, чтобы повлиять на сигнал в другом фрагменте модели. Для примера при конфигурировании калькулятора частоты ошибок необходимо указать задержку между передатчиком и приемником. Если вы просчитываете задержку, калькулятор частоты ошибок обрабатывает несоответствующие пары данных и, следовательно, возвращает бессмысленный результат.

Этот раздел иллюстрирует расчет задержек в многоскоростных моделях и в моделях, где общая задержка в последовательности блоков содержит несколько задержек от отдельных блоков. В этом разделе также указывается, как использовать блоки Find Delay и Delay для борьбы с задержками в модели.

В других частях этого набора документации также рассматриваются задержки. Для получения информации о работе с задержками или о задержках в определенных типах блоков, смотрите

Find Delay страницу с описанием блока

Delay страницу с описанием блока

Viterbi Decoder страницу с описанием блока

Derepeat страницу с описанием блока

Для обсуждения задержек в более простых примерах, чем таковые в этом разделе, смотрите

В то время как некоторые блоки могут определять свое текущее выходное значение, используя только текущее входное значение, другие блоки нуждаются в входных значениях из нескольких временных шагов, чтобы вычислить текущее выходное значение. В последней ситуации блок несет задержку. Примером этого случая является то, что блок Derepeat должен иметь в среднем пять выборок от скалярного сигнала. Блок должен задержать вычисление среднего значения, пока не получит все пять выборок.

В целом задержки в вашей модели могут исходить из различных источников:

Цифровые демодуляторы

Сверточные перемежители или обращенные перемежители

Уравнители

Блок декодера Viterbi

Буферизация, понижающая дискретизация, дерепеация и аналогичные операции сигнала

Явные блоки задержки, такие как задержка и переменная целочисленная задержка

Фильтры

Следующие обсуждения включают некоторые из этих источников задержек.

В этом разделе рассматривается 256-Channel пример ADSL и показано, как вычислить правильное значение параметров Receive delay в одном из блоков вычисления частоты ошибок в модели. Модель включает задержки от сверточного перемежения и явный блок задержки. Чтобы открыть модель примера ADSL, введите commadsl в командной строке MATLAB.

В примере ADSL данные следуют один из двух параллельных путей, один с ненулевой задержкой, а другой с задержкой нуля. Один путь включает сверточный перемежитель и обратный перемежитель, другой - нет. Около конца каждого пути находится блок Вычисления Частоты Ошибок, чей параметр Receive delay должен отражать задержку заданного пути. Остальная часть обсуждения делает наблюдение за периодами системы координат в модели, а затем рассматривает путь для перемеженных данных.

Перед поиском отдельных задержек сначала наблюдайте, что большинство сигнальных линий на протяжении модели имеют один и тот же период системы координат. На вкладке Debug разверните Information Overlays. В Sample Time разделе выберите Colors. Эта опция блокирует блоки и сигналы в соответствии с их периодами системы координат (или периодами дискретизации, в случае сигналов, основанных на дискретизации). Все сигнальные линии на верхнем уровне модели имеют одинаковый цвет, что означает, что они разделяют один и тот же период системы координат. Как следствие, системы координат являются удобным модулем для измерения задержек в блоках, которые обрабатывают эти сигналы. В расчет совокупной задержки вдоль пути взвешенное среднее значение (из числа систем координат, взвешенных по каждому периоду системы координат) уменьшается до суммы.

В фрагмент передатчика модели перемеженный путь является нижней ветвью, показанной желтым цветом ниже. Точно так же перемеженный путь в фрагменты приемника модели является нижней ветвью. Рядом с концом перемеженного пути находится блок Error Rate Calculation, который вычисляет значение, помеченное Interleaved BER.

В следующей таблице суммированы задержки в пути для неперемеженных данных. Последующие абзацы объясняют задержки более подробно и объясняют, почему общая задержка относительно блока Вычисления Частоты Ошибок является одной системой координат или 776 выборками.

| Блок | Задержка в выходе выборок из отдельного блока | Задержка, в системах координат | Задержка, во входных выборках к блоку вычисления частоты ошибок |

|---|---|---|---|

| Сверточный перемежитель и сверточная пара Deinterleaver | 40 | 1 (комбинированный) | 776 (комбинированный) |

| Задержка | 800 | ||

| Общее количество | Н/Д | 1 | 776 |

Перемежение. В отличие от неперемеженного пути, перемеженный путь содержит блок Сверточного Перемежителя в передатчике и блок Сверточного Перемежителя в приемнике. Задержка пары перемежитель/перемежитель является продуктом параметра Rows of shift registers, параметра Register length step и на единицу меньше параметра Rows of shift registers. В этом случае задержка пары перемежитель/обратный перемежитель оказывается 5 * 2 * 4 = 40 отсчетов.

Блок задержки. Приемный фрагмент перемеженного пути также содержит блок Delay. Этот блок явным образом вызывает задержку 800 выборки, имеющих тот же шаг расчета, что и 40 выборки задержки от пары перемежитель/перемежитель. Поэтому общая задержка от чередования, обратного перемежения и явной задержки составляет 840 выборки. Эти 840 выборок составляют одну систему координат данных, покидающих блок Delay.

Суммирование задержек. Никакие другие блоки в перемеженном пути примера не вызывают задержек. Добавление задержек от пары перемежитель/обратный перемежитель и блока Delay указывает, что общая задержка в перемеженном пути является одной системой координат.

Общая задержка относительно блока вычисления частоты ошибок. Блок Вычисления Частоты Ошибок, который вычисляет значение, маркированное Interleaved BER требует Receive delay значение параметров, которое эквивалентно одной системе координат. Параметр Receive delay измеряется в выборках, и каждый входной кадр в блок Вычисления Частоты Ошибок содержит 776 выборок. Кроме того, частота систем координат в выходных портах всех блоков, вызывающих задержку в перемеженном пути, равна частоте систем координат на входе блока вычисления частоты ошибок. Поэтому правильное значение для параметра Receive delay 776 выборки.

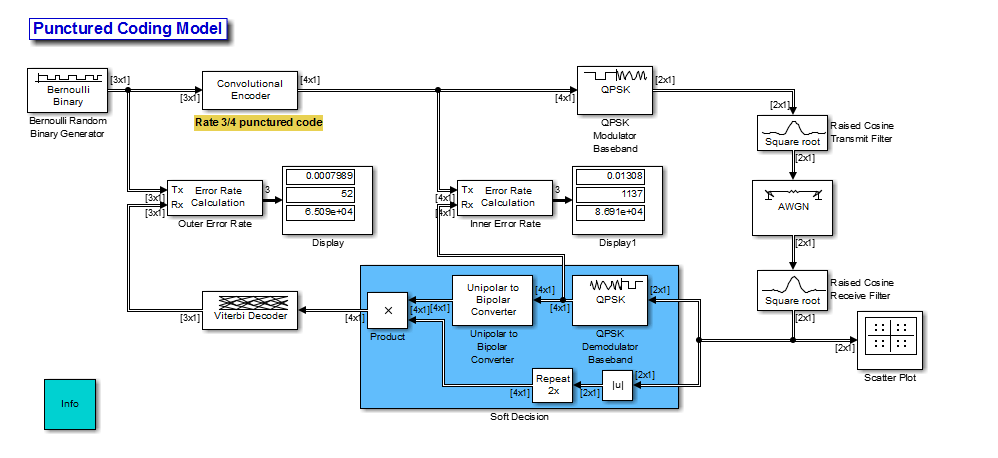

В этом разделе рассматривается проколотая модель кодирования, которая включает задержки от декодирования, понижающей дискретизации и фильтрации. Два блока вычисления частоты ошибок в модели работают правильно тогда и только тогда, когда их параметры Receive delay точно отражают задержки в модели. Чтобы открыть модель, введите doc_punct в командной строке MATLAB.

Перед поиском отдельных задержек, если панель Timing Legend еще не открыта, на вкладке Debug разверните Information Overlays. В Sample Time разделе выберите Legend. На панели Timing Legend > Highlight > All. Только самый правый фрагмент модели отличается цветом от остальной части модели. Это означает, что все сигналы и блоки в модели, кроме сигналов в самом правом ребре, имеют один и тот же период системы координат. Следовательно, системы координат с этой преобладающей частотой систем координат являются удобным модулем для измерения задержек в блоках, которые обрабатывают эти сигналы. В расчет совокупной задержки вдоль пути взвешенное среднее значение (из числа систем координат, взвешенных по каждому периоду системы координат) уменьшается до суммы.

Желтые блоки представляют многоуровневые системы, в то время как блок AWGN Channel запускается с более высокой частотой систем координат, чем все другие блоки в модели.

Блок с меткой Inner Error Rate, расположенный недалеко от центра модели, является копией блока Error Rate Calculation из библиотеки Comm Sinks. Он вычисляет вероятность битовой ошибки для фрагмента модели, которая исключает проколотый сверточный код. В части модели между двумя входными сигналами этого блока задержки исходят из Tx-фильтра и Rx-фильтра. В этом разделе объясняется, почему Receive delay параметр блока Inner Error Rate является общим значением задержки 16.

Блок фильтра Tx. Блок с меткой Tx Filter является копией блока Raised Cosine Transmit Filter. Он интерполирует входной сигнал в множитель 8 и применяет квадратный корневой фильтр приподнятого косинуса. Значение параметра Filter span in symbols блока равняется 6, что означает, что его групповая задержка составляет 3 символа. Поскольку частота дискретизации этого блока увеличивается от входного порта до выходного порта, он должен вывести начальную систему координат нулей в начале симуляции. Поскольку размер входного кадра равен 2, общая задержка блока составляет 2 + 3 = 5 символов. Это соответствует 5 выборкам на входном порту блока.

Блок фильтра Rx. Блок с меткой Rx Filter является копией блока Raised Cosine Receive Filter. Он децимирует свой входной сигнал в 8 раз и применяет другой фильтр приподнятого косинуса с квадратным корнем. Значение Filter span in symbols параметра этого блока равняется 6, что означает, что его групповая задержка составляет 3 символа. На выходе блока 3 символа соответствуют 3 выборкам.

Блок демодулятора QPSK. Блок с меткой QPSK Demodulator Baseband принимает комплексные сигналы QPSK и выводит 2 бита для каждого комплексного входа. Это преобразование в выходные биты удваивает совокупную задержку на входе блока.

Суммирование задержек. Никакие другие блоки в части модели между двумя входными сигналами блока Inner Error Rate не вызывают задержек. Общая задержка затем (2 + 3 + 3) * 2 = 16 выборки. Это значение может использоваться как параметр Receive Delay в блоке Inner Error Rate.

Блок с меткой Outer Error Rate, расположенный слева от модели, является копией блока Error Rate Calculation из библиотеки Comm Sinks. Он вычисляет вероятность битовой ошибки для всей модели, включая проколотый сверточный код. Задержки возникают из блоков Tx Filter, Rx Filter и Viterbi Decoder. В этом разделе объясняется, почему параметр Receive delay блока Внешней Частоты Ошибок является общим значением задержки 108.

Фильтрация и демпфирование блоков. Блоки Tx Filter, Rx Filter и Downsample имеют комбинированную задержку 16 выборок. Для получения дополнительной информации смотрите Внутренний Блок Частоты Ошибок.

Блок декодера Viterbi. Потому что блок Viterbi Decoder декодирует скорость 3/4 проколотый код, он фактически уменьшает задержку, наблюдаемую на его входе. Это сокращение дано как 16 * 3/4 = 12 выборки.

Блок Viterbi Decoder декодирует сверточный код, и использование алгоритмом пути трассировки вызывает задержку. Блок обрабатывает сигнал на основе кадра и имеет Operation mode значение Continuous. Поэтому задержка, измеренная в выходных выборках, равна Traceback depth значению параметров 96. (Величина задержки указывается на странице с описанием для блока Viterbi Decoder.) Поскольку выход блока Viterbi Decoder является именно одним из входов в блок Outer Ошибки Rate, легче считать задержку 96 выборок, а не преобразовывать ее в эквивалентное количество систем координат.

Общая задержка относительно внешнего блока вероятности ошибок. Блок Outer Error Rate требует Receive delay значения параметров, которое является суммой всех задержек в системе. Общая задержка 12 + 96 = 108 выборки.

Предыдущие обсуждения объяснили, почему определенные блоки вычисления частоты ошибок в моделях имели определенные Receive delay значения параметров. Вы могли прийти к этим номерам независимо при помощи блока Find Delay. В этом разделе объясняется, как найти задержку сигнала с помощью модели примера ADSL, commadsl, в качестве примера. Применение метода к проколотому примеру сверточного кодирования, обсуждаемому в модели проколотого кодирования, было бы аналогичным.

Напомните из пути для перемеженных данных, что задержка в пути для перемеженных данных составляет 776 выборок. Чтобы блок Find Delay вычислил это значение для вас, используйте эту процедуру:

Вставьте блок Find Delay и блок Display в модель около блока Error Rate Calculation, который вычисляет значение, помеченное Interleaved BER.

Соедините блоки как показано ниже.

Установите параметр Correlation window length блока Find Delay на значение, существенно больше 776, например 2000.

Примечание

Необходимо использовать достаточно большую длину окна корреляции, иначе значения, произведенные блоком Find Delay, не стабилизируются при правильном значении.

Запустите симуляцию.

Новый блок Display теперь показывает значение 776, как и ожидалось.

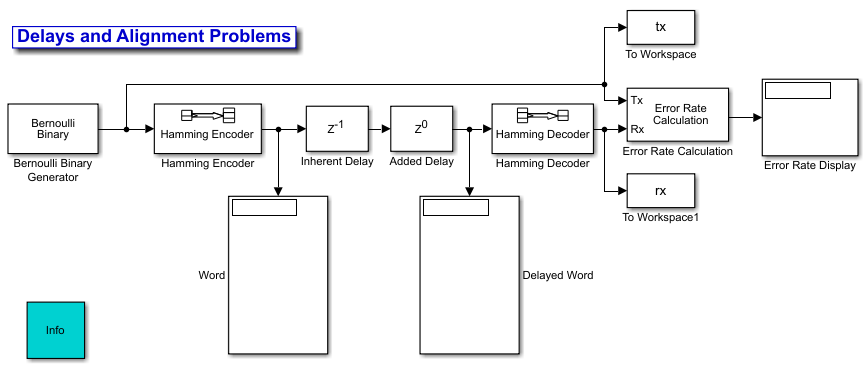

Задержки и проблемы выравнивания. Некоторые модели требуют, чтобы вы не только вычисляли задержки, но и манипулировали ими. Для примера, если модель несет задержку между блочным энкодером и его соответствующим декодером, декодер может неправильно истолковать контуры между кодовыми словами, которые она получает, и, следовательно, возвращать бессмысленные результаты. В более общем случае такая ситуация может возникнуть, когда путь между парными компонентами блочно-ориентированной операции (такой как перемежение, блочное кодирование или преобразование бит в целое) включает в себя операцию, вызывающую задержку (такую как перечисленные в Источниках задержек).

Чтобы избежать этой проблемы, можно вставить дополнительную задержку на соответствующую величину между энкодером и декодером. Если модель также вычисляет частоту ошибок, то дополнительная задержка влияет на этот процесс, как описано в Delays. Этот раздел использует примеры, чтобы проиллюстрировать цель, методы и последствия манипулирования задержками в различных обстоятельствах.

Этот раздел иллюстрирует чувствительность блочно-ориентированных операций к задержкам, используя небольшую модель, которая предназначена для захвата сути задачи в простой форме. Откройте модель путем ввода doc_alignment в MATLAB® командная строка. Затем запустите симуляцию, чтобы блоки Display показали соответствующие значения.

В этой модели два блока кодирования создают и декодируют блочный код. Две копии блока Delay создают задержку между энкодером и декодером. Два блока Delay имеют различные цели в этой иллюстративной модели:

Блок Inherent Delay представляет любые вызывающие задержку блоки, которые могут возникнуть в модели между энкодером и декодером. Список возможностей, которые могут возникнуть в более реалистичной модели, см. в разделе «Источники задержек».

Блок Add Delay является явной задержкой, которую вы вставляете, чтобы создать соответствующую общую задержку между энкодером и декодером. Для примера, commadsl модель содержит блок Delay, который служит этой цели.

Наблюдение за проблемой. По умолчанию для параметров Delay в блоках Inherent Delay и Added Delay задано значение 1 и 0, соответственно. Это представляет ситуацию, в которой некоторая операция вызывает однобитовую задержку между энкодером и декодером, но вы еще не пытались ее компенсировать. Общая задержка между энкодером и декодером составляет один бит. Из блоков, помеченных Word и Delayed Word, видно, что кодовое слово, которое покидает энкодер, смещено вниз на один бит к моменту его входа в декодер. Декодер принимает сигнал, в котором контур кодового слова находится во втором бите в системе координат, вместо совпадения с началом системы координат. То есть кодовые слова и системы координат, которые их удерживают, не выравниваются друг с другом.

Это несоответствие проблематично, потому что блок Hamming Decoder принимает, что каждая система координат начинает новое кодовое слово. В результате он пытается декодировать слово, которое состоит из последнего бита одной выходной системы координат от энкодера, за которым следуют первые шесть битов следующего выхода системы координат от энкодера. Из блока Error Rate Display видно, что вероятность ошибок от этой операции декодирования близка к 1/2. То есть декодер редко восстанавливает исходное сообщение правильно.

Чтобы использовать аналогию, предположим, что кто-то развращает абзац прозы, перемещая каждый символ периода из конца предложения в конец первого слова следующего предложения. Если вы пытаетесь прочитать такой абзац, принимая, что новое предложение начинается через период, вы неправильно понимаете начало и конец каждого предложения. В результате вы можете не понять смысла этого пункта.

Чтобы увидеть, как задержки различных сумм влияют на эффективность декодера, измените значения параметра Delay в блоке Addusted Delay и параметра Receive delay в блоке Error Rate Calculation, а затем запустите симуляцию снова. Многие комбинации значений параметров приводят к частоте ошибок, которая близка к 1/2. Кроме того, если вы исследуете переданные и полученные данные путем ввода

[tx rx]

в командной строке MATLAB можно не обнаружить корреляции между переданными и принятыми данными.

Исправление задержек

Некоторые комбинации значений параметров дают нулевую частоту ошибок, потому что задержки подходят для системы. Для примера:

В блоке Add Delay установите Delay равным 6.

В блоке Error Rate Calculation установите Receive delay равной 4.

Запустите симуляцию.

Введите [tx rx] в командной строке MATLAB.

Верхний номер в блоке Error Rate Display показывает, что вероятность ошибок равна нулю. Декодер правильно восстановил каждое переданное сообщение. Однако блоки Word и Displayed Word не показывают совпадающих значений. Не сразу ясно, как выход энкодера и вход декодера связаны друг с другом. Чтобы прояснить вопрос, исследуйте выход в командном окне MATLAB. Последовательность вдоль первого столбца (tx) появляется во втором столбце (rx) четыре строки позже. Чтобы подтвердить это, введите

isequal(tx(1:end-4),rx(5:end))

в командной строке MATLAB и наблюдайте, что результат 1 Правда. Эта последняя команда проверяет, соответствует ли первый столбец сдвинутой версии второго столбца. Сдвиг вектора MATLAB rx на четыре строки соответствует поведению блока Error Rate Calculation, когда его параметр Receive delay установлен в 4.

Результирующие, эти специальные значения параметров Delay и Receive delay работают по этим причинам:

В совокупности блоки Inherent Delay и Added Delay задерживают кодированный сигнал полным кодовым словом, а не частичным кодовым словом. Таким образом, декодер верен в своем допущении, что контур кодового слова падает в начале входного кадра и правильно декодирует слова. Однако задержка в кодированном сигнале заставляет каждое восстановленное сообщение появляться на одно слово позже, то есть на четыре бита позже.

Блок Вычисления Частоты Ошибок компенсирует задержку в одном слове в системе путем сравнения каждого слова переданного сигнала с данными четырёх бит позже в принятом сигнале. Таким образом, он правильно заключает, что вероятность ошибки декодера равна нулю.

Примечание

Это не единственные значения параметров, которые приводят к нулевой частоте ошибок. Поскольку код в этой модели является (7, 4) блочным кодом, и неотъемлемое значение задержки 1, можно задать параметры Delay и Receive delay 7k-1 и 4k, соответственно, для любого положительного целого числа k. Важно, чтобы сумма неотъемлемой задержки (1) и добавленной задержки (7 к-1) была кратна длине кодового слова (7).

Выравнивание слов блочного кода. Пример ADSL, обсуждаемый в модели примера ADSL, иллюстрирует необходимость манипулировать задержкой в модели так, чтобы каждая система координат данных, который входит в блочный декодер, имела контур кодового слова в начале системы координат. Необходимость возникает из-за того, что путь между блочным энкодером и блочным декодером включает в себя операцию сверточного перемежения, вызывающую задержку. Этот раздел объясняет, почему модель использует блок Delay, чтобы манипулировать задержкой между сверточным обратным перемежителем и блочным декодером, и почему блок Delay сконфигурирован таким, какой он есть. Чтобы открыть модель примера ADSL, введите commadsl в командной строке MATLAB.

Расхождение кодовых слов

В примере ADSL блоки Convolutional Interleaver и Convolutional Deinterleaver появляются после подсистем Scrambler & FEC, но перед подсистемами Descrambler & FEC. Эти две подсистемы содержат блоки, которые выполняют кодирование Рида-Соломона, и блоки кодирования ожидают, что каждая система координат входных данных начнётся с нового слова, а не с середины слова.

Как обсуждалось в путь для перемеженных данных, задержка пары перемежитель/обратный перемежитель составляет 40 выборки. Однако вход в подсистему Descrambler и FEC является системой координат размера 840, и 40 не является кратным 840. Следовательно, сигнал, который выходит из блока Convolutional Deinterleaver, является системой координат, первый вход которого не представляет начало нового кодового слова. Как описано в «Наблюдении проблемы», это расхождение между кодовыми словами и системами координат, которые их содержат, препятствует правильному декодированию декодером.

Вставка задержки для исправления выравнивания

Пример ADSL решает проблему путем перемещения контура слова из 41-й выборки 840-выборочной системы координат в первую выборку последующей системы координат. Перемещение контура слова эквивалентно задержке сигнала. С этой целью пример содержит блок Delay между блоком Convolutional Deinterleaver и подсистемой Descrambler & FEC.

Параметр Delay в блоке Delay 800 потому что это минимальное количество выборок, требуемых для сдвига 41-й выборки одной системы координат с 840 выборками к первой выборке следующей системы координат с 840 выборками. Другими словами, сумма неотъемлемой задержки с 40 выборками (от процесса перемежения/перемежения) и искусственной задержки с 800 выборками является полной системой координат данных, а не частичной системой координат.

Эта 800-выборочная задержка имеет значение для других частей модели, в частности, параметра Receive delay в одном из блоков Вычисления Частоты Ошибок. Для получения дополнительной информации о том, как задержка влияет на значение этого параметра, смотрите Путь для перемеженных данных.

Использование блока Find Delay

В предыдущем обсуждении объяснялось, почему 800-выборочная задержка необходима, чтобы исправить расхождение между кодовыми словами и системами координат, которые их содержат. Зная, что подсистема Descrambler & FEC требует, чтобы контуры системы координат происходили на контурах слова, вы могли прийти к числу 800 независимо при помощи блока Find Delay. Используйте следующую процедуру:

Вставьте блок Find Delay и блок Display в модель.

Создайте линию ветви, который соединяет вход блока Convolutional Interleaver с sRef вход блока Find Delay.

Создайте другую линию ветви, которая соединяет выход блока Convolutional Deinterleaver с sDel вход блока Find Delay.

Соедините delay выход блока Find Delay в новый блок Display. Измененная часть модели теперь выглядит как следующее изображение (которое также показывает тени на ключевых блоках, чтобы подчеркнуть изменения).

Покажите размерности каждого сигнала в модели. На вкладке Debug разверните Information Overlays. В Signals разделе выберите Signal Dimensions.

Запустите симуляцию.

Новый блок Display теперь показывает значение 40. Кроме того, отображение размерностей сигнала показывает, что выход от блока Convolutional Deinterleaver является системой координат длины 840. Эти результаты показывают, что последовательность блоков между Сверточным Перемежителем и Сверточным Deinterleaver, включительно, задерживает система координат с 840 выборками на 40 выборок. Дополнительная задержка в 800 выборки приводит к общей задержке в 840. Поскольку общая задержка теперь является произведением, кратным длине системы координат, задержанные данные с обращенным перемежением могут быть декодированы.

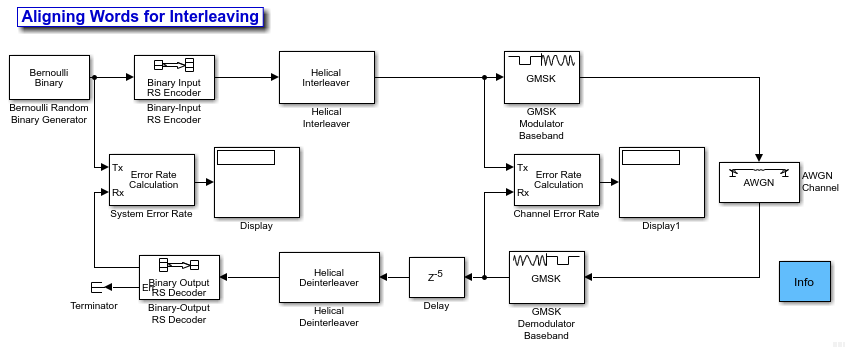

Выравнивание слов для перемежения. Этот раздел описывает пример, который манипулирует задержкой перед обратным перемежителем, потому что путь между перемежителем и обратным перемежителем включает задержку от демодуляции. Чтобы открыть модель, введите doc_gmskint в командной строке MATLAB.

Модель включает блочное кодирование, спиральное перемежение и GMSK модуляцию. В таблице ниже приведены отдельные задержки блоков в модели.

| Блок | Задержка в выходе выборок из отдельного блока | Ссылка |

|---|---|---|

| Базовая полоса демодулятора GMSK | 16 | Задержки в цифровой модуляции |

| Спиральный перемежитель | 42 | Задержки сверточных перемежителей |

| Задержка | 5 | Delay страницу с описанием |

Расхождение чередующихся слов

Процесс демодуляции в этой модели вызывает задержку между перемежителем и обратным перемежителем. Поскольку перемежитель ожидает, что каждая система координат входных данных начнётся с нового слова, важно убедиться, что общая задержка между перемежителем и перемежителем включает в себя одни или несколько полных систем координат, но без частичных систем координат.

Задержка демодулятора составляет 16 выходных выборок. Однако вход блока Helical Deinterleaver является системой координат размера 21 и 16 не является кратным 21. Следовательно, сигнал, который выходит из блока Baseband демодулятора GMSK, является системой координат, первый вход которого не представляет начало нового слова. Как описано в Наблюдении Задачи, это расхождение между словами и системами координат, которые их содержат, препятствует обращению перемежителя.

Вставка задержки для исправления выравнивания

Модель перемещает слово контура из 17-й выборки 21-выборочной системы координат в первую выборку следующей системы координат. Перемещение контура слова эквивалентно задержке сигнала на пять выборок. Блок Delay между блоком Baseband демодулятора GMSK и блоком Helical Deinterleaver выполняет такую задержку. Блок Delay имеет Delay набора параметров, чтобы 5.

Объединяя эффекты демодулятора и блока Delay, общая задержка между перемежителем и обращенным перемежителем является полной системой координат данных с 21 выборкой, а не частичной системой координат.

Проверка выравнивания блочных кодовых слов

Перемежитель и перемежитель вызывают комбинированную задержку из 42 выборок, измеренных на выходе из блока Helical Deinterleaver. Поскольку задержанный выход от обратного перемежителя идет рядом с декодером кода Рида-Соломона, и поскольку декодер ожидает, что каждая система координат входных данных начнётся с нового слова, важно гарантировать, что общая задержка между энкодером и декодером включает в себя одни или несколько полных систем координат, но без частичных систем координат.

В этом случае задержка с 42 отсчетами является в точности двумя системами координат. Поэтому нет необходимости вставлять блок Delay между блоком Helical Deinterleaver и блоком Binary-Output RS Decoder.

Вычисление задержек для настройки блоков вычисления частоты ошибок

Модель содержит два блока Вычисления Частоты Ошибок, помеченные как Вероятность Ошибок в Канале и Вероятность Системных Ошибок. Каждый из этих блоков имеет параметр Receive delay, который должен отражать задержку пути между блоками Tx и Rx сигналы. В следующей таблице объясняются значения Receive delay в двух блоках.

| Блок | Получение значения задержки | Причина |

|---|---|---|

| Вероятность ошибок в канале | 16

| Задержка блока Baseband демодулятора GMSK в выборках |

| Вероятность системных ошибок | 15*3

| Три пятнадцатисерийные системы координат: один кадр из блоков Baseband и Delay демодулятора GMSK и два кадра из пары перемежитель/перемежитель |

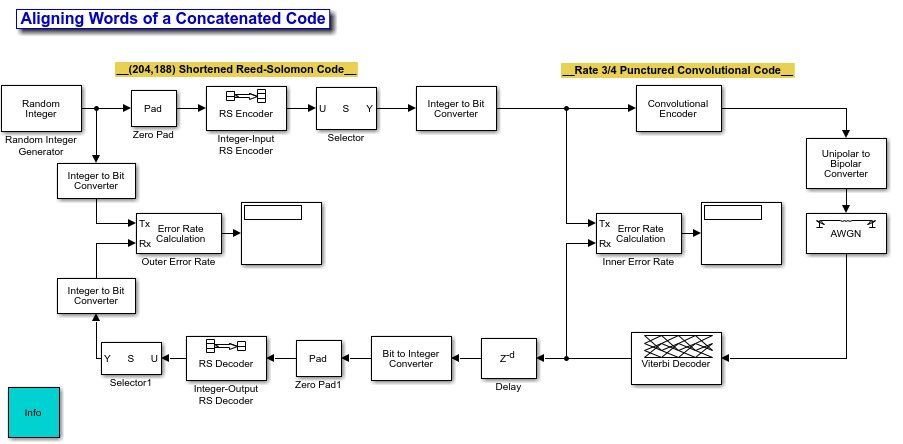

Согласование слов конкатенированного кода. Этот раздел описывает пример, который манипулирует задержкой между двумя фрагментами декодера конкатенированного кода, поскольку первый фрагмент включает задержку от декодирования Viterbi, в то время как второй фрагмент ожидает, что контуры системы координат совпадают с контурами слова. Чтобы открыть модель, введите doc_concat в командной строке MATLAB. Он использует блочный и сверточный коды из commdvbt пример, но упрощает общий проект много.

Модель включает укороченный блочный код и проколотый сверточный код. Все сигналы и блоки в модели имеют один и тот же период системы координат. В следующей таблице представлены отдельные задержки блоков в модели.

| Блок | Задержка в выходе выборок из отдельного блока |

|---|---|

| Viterbi Decoder | 136 |

| Delay | 1496 (то есть 1632 - 136) |

Расхождение Блока кодовых слов

Процесс декодирования Viterbi в этой модели вызывает задержку между блоком Integer to Bit Converter и блоком Bit to Integer Converter. Поскольку последний блок ожидает, что каждая система координат входных данных начнётся с нового 8-битового слова, важно убедиться, что общая задержка между двумя блоками конвертера включает в себя одни или несколько полных систем координат, но без частичных систем координат.

Задержка блока Viterbi Decoder составляет 136 выходных выборок. Однако вход блока Bit to Integer Converter является системой координат размера 1632. Следовательно, сигнал, который выходит из блока Viterbi Decoder, является системой координат, первый вход которого не представляет начало нового слова. Как описано в Наблюдении Задачи, это расхождение между словами и системами координат, которые их содержат, препятствует блоку конвертера.

Примечание

Внешний декодер в этой модели (Integer-Output RS Decoder) также ожидает, что каждая система координат входных данных начнётся с нового кодового слова. Поэтому проблема расхождения в этой модели влияет на многие проекты конкатенированного кода, а не только на те, которые преобразуются между двоичными и целочисленными сигналами.

Вставка задержки для исправления выравнивания

Модель перемещает слово контура из 137-й выборки 1632- систем координат выборки в первую выборку следующей системы координат. Перемещение контура слова эквивалентно задержке сигнала на 1632-136 выборки. Блок Delay между блоком Viterbi Decoder и блоком Bit to Integer Converter выполняет такую задержку. Блок Delay имеет Delay набора параметров, чтобы 1496.

Объединяя эффекты блока Viterbi Decoder и блока Delay, общая задержка между перемежителем и обращенным перемежителем является полным 1632- система координат данных, а не частичной системой координат.

Вычисление задержек для настройки блоков вычисления частоты ошибок

Модель содержит два блока Вычисления Частоты Ошибок, помеченные Внутренней Частотой Ошибок и Внешней Частотой Ошибок. Каждый из этих блоков имеет параметр Receive delay, который должен отражать задержку пути между блоками Tx и Rx сигналы. В приведенной ниже таблице поясняются значения Receive delay в двух блоках.

| Блок | Получение значения задержки | Причина |

|---|---|---|

| Внутренняя вероятность ошибок | 136

| Задержка блока Viterbi Decoder, в выборках |

| Вероятность внешних ошибок | 1504 (188*8 bits) | Одна 188-выборочная система координат из комбинации неотъемлемой задержки блока Viterbi Decoder и добавленной задержки блока Delay |

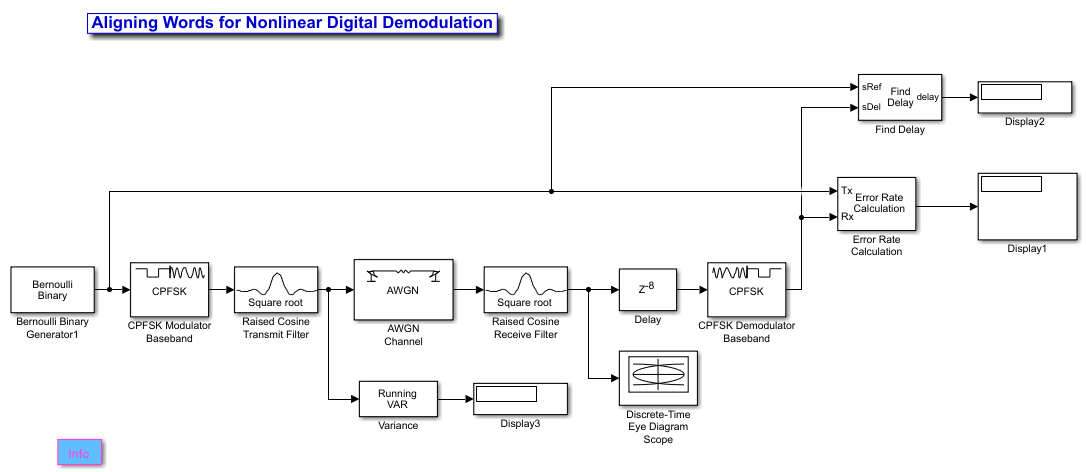

Выравнивание слов для нелинейной цифровой демодуляции. Этот пример управляет задержкой в порядке получения правильной символьной синхронизации сигнала, так что контуры символов правильно выравниваются до того, как происходит демодуляция.

Чтобы открыть эту модель, введите doc_nonlinear_digital_demod в командной строке MATLAB.

Эта модель включает схему модуляции CPFSK и фильтр формирования импульсов. Чтобы демодуляция работала должным образом, входной сигнал к блоку демодулятора CPFSK должен иметь правильное выравнивание. Различные блоки в этой модели вводят задержки обработки. Из-за этих задержек входной сигнал к блоку демодулятора CPFSK не находится в правильном выравнивании.

Оба блоков Raised Cosine Transmit и Receive Filter вводят задержку. Задержка определяется как:

где Ts представляет входный шаг расчета блока Raised Cosine Transmit Filter.

Входный шаг расчета блока Raised Cosine Transmit Filter равняется выходному шагу расчета блока Raised Cosine Receive Filter. Поэтому общая задержка на выходе приёмного фильтра приподнятого косинуса:

или

как GroupDelay = 4

Блок демодулятора CPFSK принимает этот задержанный сигнал, и затем он обрабатывает каждый набор из 8 выборок на символ, чтобы вычислить 1 выходной символ. Необходимо убедиться, что демодулятор CPFSK получает входные выборки в правильном наборе выборок. Для двоичного CPFSK с Modulation index 1/2, вход демодулятора должен выровняться по четному числу символов. Обратите внимание, что это требование применяется только к двоичному CPFSK с индексом модуляции 1/2. Другие схемы CPM с различными M-арными значениями и индексами модуляции имеют различные требования.

Чтобы убедиться, что демодулятор CPFSK в этой модели получит правильный набор входа отсчетов с правильным выравниванием, введите задержку в 8 отсчетов (в этом примере, ). Общая задержка на входе демодулятора CPFSK , что равняется двум задержкам символов (2.T, где T - период символов).

В основанном на выборке режиме демодулятор CPFSK вводит задержку в Traceback length + 1 отсчета на своем выходе. В этом примере Traceback length равняется 16. Поэтому общая Receiver delay в блоке вычисления частоты ошибок равна 17 + 2 или 19. Для получения дополнительной информации см. «Задержки в цифровой модуляции».