Вы можете следовать этому руководству как общей практике для моделирования вашего проекта с различными блоками в Simulink® Браузер библиотек.

Каждое руководство имеет уровень серьезности, который указывает на уровень податливостей. Для получения дополнительной информации см. HDL-руководства по моделированию уровней серьезности.

1.1.8

Информативный

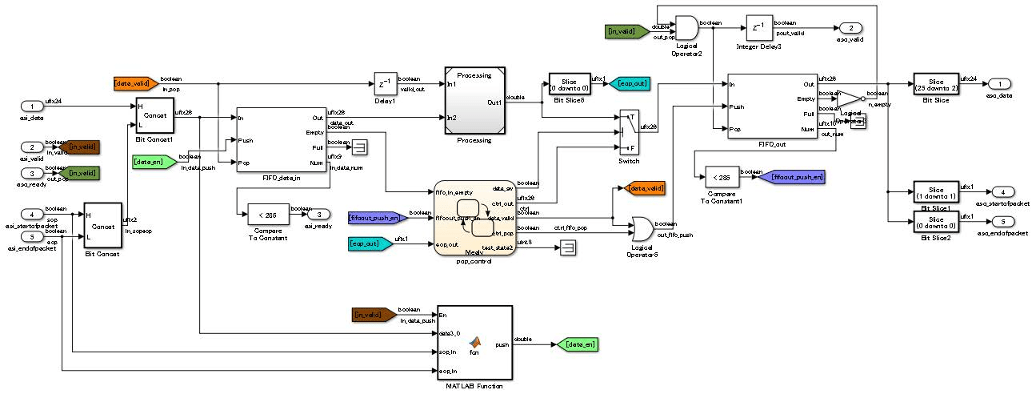

Когда вы создаете модель Simulink для генерации HDL-кода, используйте блоки Simulink, блоки MATLAB Function и Stateflow® блоки на основе приложения. Этот рисунок показывает пример того, как можно использовать различные блоки внутри DUT.

Используйте блоки Simulink, чтобы смоделировать арифметические алгоритмы, которые выполняют числовую обработку или содержат циклы обратной связи.

Используйте MATLAB Function блоки для моделирования логики управления, условные ветви, такие как операторы if-else и простые машины состояний. Можно также использовать блоки MATLAB Function для моделирования IP, который записывается с помощью MATLAB® код.

Используйте эти блоки Stateflow, чтобы смоделировать свой алгоритм:

State Transition Table (Stateflow): Используйте эти блоки для моделирования машин состояний, которые управляют выходом, используя знание прошлого и настоящего.

Chart (Stateflow): Используйте эти блоки для моделирования графиков потока с помощью условных ветвей if-else и машин состояний, которые управляют выходом, используя знание прошлого и настоящего.

Truth Table (Stateflow): Используйте эти блоки для моделирования условных ветвей if-else.

Можно смоделировать комбинационную логику, используя блоки Stateflow. Для более сложных операций и операций, которые изменяют время, таких как вставка и обработка трубопровода, используйте блоки Simulink. Затем можно использовать логику Stateflow, чтобы обработать результат, вычисленный из блоков Simulink

Для значительно больших алгоритмов, которые имеют сложные расчеты, можно разбить проект на иерархию небольших проектов. Используйте это разбиение для повторного использования, модульной разработки и ускоренной симуляции. Можно повторно использовать модели, включив их в качестве Model блоков внутри верхней модели. Модель, которая повторно использует этот блок, называется верхней моделью, а блок, который повторно используется или включен в верхнюю модель, называется ссылочной моделью.

Примечание

Когда вы генерируете HDL-код для Subsystem, которая не находится на верхнем уровне модели, HDL- Coder™ преобразует Subsystem в модель-ссылку.

Ссылка на модель обрабатывается аналогично Atomic Subsystem. В некоторых случаях может потенциально возникнуть алгебраический цикл, который может предотвратить генерацию HDL-кода. Чтобы сгенерировать код, либо удалите алгебраический цикл в проекте, либо, в Параметры конфигурации окне, задайте настройку Minimize algebraic loop occurrences.

Для подсистем, которые вы хотите симулировать в проекте и включить HDL-код, который вы создали, используйте подсистемы BlackBox. Чтобы создать BlackBox Подсистему, установите HDL- Архитектуры Subsystem или Модели-ссылки на BlackBox. Можно использовать эту архитектуру для включения рукописного HDL-кода в модель Simulink. Для получения дополнительной информации см. раздел «Проверка комбинации ручной записи и Сгенерированного HDL-кода (HDL Verifier)».

Если вы генерируете модель Simulink, используя HDL-код, который вы создали, используйте HDL-импорт. Дополнительные сведения см. в разделах Импорт кода Verilog и Генерация модели Simulink.

Если у вас есть Симулятор HDL, такой как Mentor Graphics® ModelSim® или Cadence Incisive®можно использовать блоки HDL Cosimulation (HDL Verifier) для моделирования HDL-кода для DUT и создания экземпляров этого HDL-кода в сгенерированном коде.