Используйте эти рекомендации для разработки алгоритма HDL в Simulink®. Инструкции включают использование поддерживаемых HDL блоков при моделировании вашего проекта и способы разбиения вашего проекта при разработке алгоритма.

Каждое руководство имеет уровень серьезности, который указывает на уровень податливостей. Для получения дополнительной информации см. HDL-руководства по моделированию уровней серьезности.

1.1.1

Очень рекомендуем

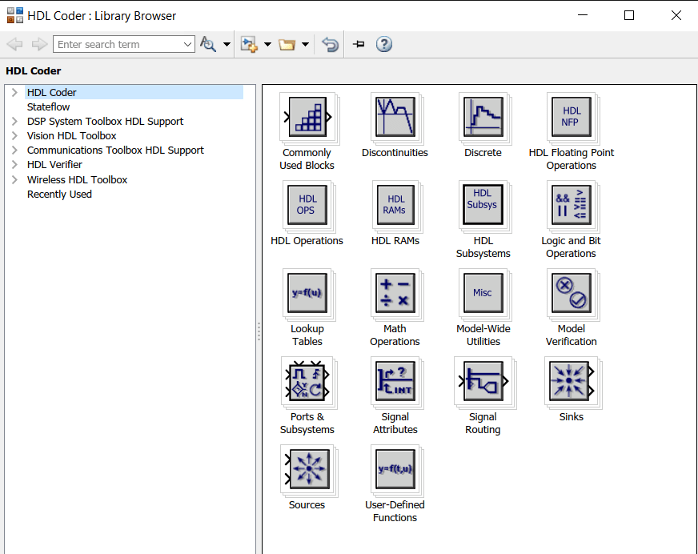

Когда вы создаете модель Simulink, используйте блоки из библиотеки Simulink Library Browser > HDL Coder. Несколько блоков в этой библиотеке предварительно сконфигурированы для генерации HDL-кода. Блоки в этой библиотеке доступны с Simulink. Если у вас нет HDL Coder™, можно симулировать блоки в модели, но невозможно сгенерировать HDL-код.

Дополнительные поддерживаемые HDL блоки можно найти в следующих библиотеках блоков Simulink:

DSP System Toolbox HDL Support

Communications Toolbox HDL Support

Vision HDL Toolbox

Wireless HDL Toolbox

Для отображения в браузере библиотек только блоков, поддерживаемых HDL:

на вкладке Apps выберите HDL Coder. Появится вкладка HDL Code. Выберите HDL Block Properties > Open HDL Block Library.

Также в MATLAB® Командное окно, введите hdllib.

hdllib

Чтобы восстановить браузер библиотеки к представлению по умолчанию, введите эту команду:

hdllib('off')Примечание

Набор поддерживаемых блоков изменится в будущих релизах, поэтому при установке новой версии этого продукта следует перестраивать библиотеку поддерживаемых блоков.

1.1.2

Рекомендуется

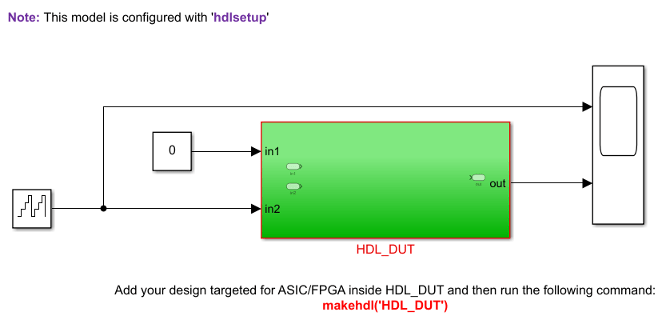

Когда вы создаете модель Simulink для генерации HDL-кода, Subsystem, для которого вы хотите сгенерировать HDL-код, является Design-Under-Test (DUT). Эта Подсистема содержит блоки Simulink, которые могут быть реализованы на вашем целевом устройстве FPGA или ASIC. Можно далее разбить логику внутри DUT на меньшие подсистемы на основе функциональности, частот дискретизации в проекте и так далее. При генерации HDL-кода DUT становится модулем или сущностью верхнего уровня, а Подсистемы внутри DUT становятся подмодулями или меньшими сущностями.

Блоки за пределами Подсистемы DUT становятся частью испытательного стенда. Испытательный стенд может состоять из блоков, которые не поддерживаются для генерации HDL-кода. Моделируйте испытательный стенд для:

Проверьте функциональность DUT в модели Simulink.

Проверьте функциональную эквивалентность сгенерированной модели с помощью исходной модели.

Для примера, если вы открываете Blank_DUT шаблона модели Simulink, эта модель открывается в редакторе Simulink.

В этой модели HDL_DUT Subsystem является DUT и блоки вне этой Подсистемы образуют испытательный стенд. Можно разработать алгоритм HDL в Подсистеме HDL_DUT. Эта модель шаблона предварительно сконфигурирована для генерации HDL-кода.

1.1.3

Очень рекомендуем

Нисходящие инструменты синтеза и симуляции не поддерживают двухбайтовые символы, такие как японские и китайские символы. HDL Coder не поддерживает использование:

Двухбайтовые символы в именах модели и блоков.

Зарезервированные слова вашей операционной системы в модели и имена блоков, такие как CR, con, prn, aux, ptr, null, ipt1, ipt2, ipt3, и ipt4, com1, com2, com3, и com4.

Двухбайтовые символы в комментариях, потому что комментарии передаются в сгенерированный код. Вместо этого используйте комментарии на английском языке.

1.1.4

Рекомендуется

Чтобы упростить управление сгенерированным HDL-кодом, можно документировать справочную информацию как часть настроек модели следующими способами:

Пользовательские комментарии к заголовкам файлов и нижним колонтитулам в HDL-коде для проекта и тестирования

На вкладке HDL Code Generation > Global Settings > Coding Style диалогового окна Configuration Parameters с помощью параметров Custom File Header Comment и Custom File Footer Comment можно ввести собственные пользовательские комментарии, которые будут отображаться в качестве колонтитулов во всех сгенерированных HDL-файлах. Дополнительные сведения см. в разделе Параметры индивидуальной настройки комментария к файлу.

Аннотации модели и блока, текстовые комментарии и комментарии к требованию

Можно добавить аннотации в виде аннотаций модели, текстовых комментариев или комментариев требования к сгенерированному коду. Например, можно вводить текст непосредственно на блоке в виде аннотаций Simulink или вставлять текстовые комментарии, помещая DocBlock в модель. Чтобы связать аннотации в блок-схеме с блоками в модели, используйте линии, чтобы соединить аннотации с этими блоками. Эти аннотации отображаются как комментарии рядом с блоками в сгенерированном коде. Дополнительные сведения см. в разделе Генерация кода с аннотациями или комментариями.

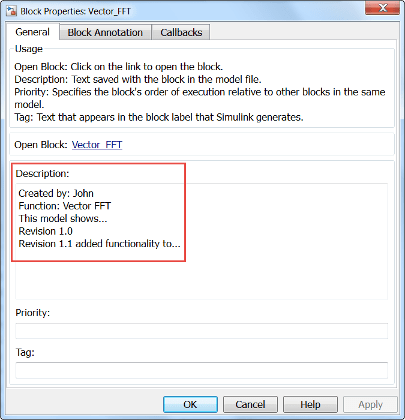

Функции блоков и атрибуты как пользовательские комментарии заголовка для каждого файла

В Description разделе Блока Свойств для подсистем, которые вы используете в проекте. Эта информация отображается как заголовки комментариев в HDL-коде. Для примера этот рисунок иллюстрирует комментарии блоков, добавленные для Vector FFT

Subsystem в вашем проекте.

Комментарии блока появляются как заголовки в сгенерированном HDL-коде.

-- Simulink subsystem description for vector_fft_implementation_example/Vector_FFT: -- -- Created by: John -- Function: Vector FFT -- This model shows... -- Revision 1.0 -- Revision 1.1 added functionality to... -- -- ------------------------------------------------------------- LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; ENTITY Vector_FFT IS