Можно просматривать и редактировать опции и параметры, которые влияют на генерацию HDL-кода, в диалоговом окне Параметры конфигурации (Configuration Parameters) или в Обозревателе моделей (Model Explorer). Этот пример иллюстрирует, как можно использовать диалоговое окно Параметры конфигурации (Configuration Parameters) для генерации HDL-кода для модели Symmetric конечной импульсной характеристики filter.

Прежде чем вы сгенерируете HDL-код, модель должна быть совместима с генерацией HDL-кода. Чтобы проверить и обновить свою модель на совместимость с HDL, смотрите Проверку совместимости HDL модели Simulink с использованием HDL-код Advisor.

В этом примере используется модель Symmetric конечной импульсной характеристики, которая совместима с генерацией HDL-кода. Чтобы открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует деление труда, которая подходит для HDL- проекта.

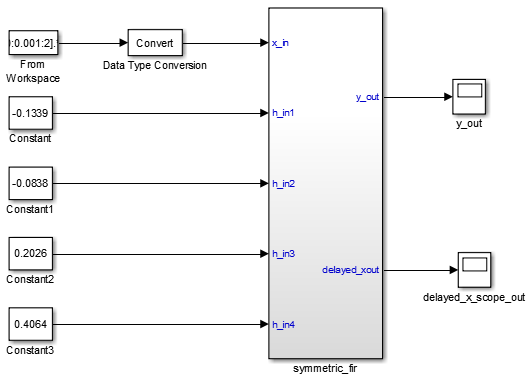

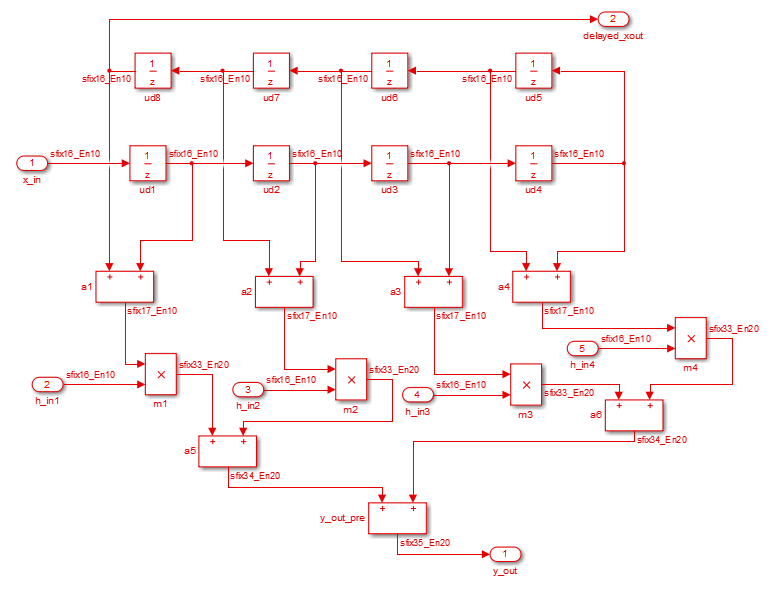

The symmetric_fir подсистема, реализующая алгоритм фильтра, является тестируемым устройством (DUT). Из этой подсистемы генерируется сущность HDL.

Компоненты модели верхнего уровня, которые управляют подсистемой, работают как испытательный стенд.

Модель верхнего уровня генерирует 16-битные входные сигналы с фиксированной точкой для symmetric_fir подсистема. Блок Рабочая область Signal From генерирует тестовое воздействие (стимулирующий) сигнал для фильтра. Четыре блока Constant обеспечивают коэффициенты фильтра. Блоки Scope используются для симуляции и не используются для генерации HDL-кода.

Для перехода к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB®:

Создайте папку с именем sl_hdlcoder_work, для примера:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели примера и папки и сгенерированный HDL-код. Используйте папку, которая не находится в дереве папок MATLAB.

Сделайте sl_hdlcoder_work папка в рабочей папке, например:

cd C:\work\sl_hdlcoder_workСохраните локальную копию sfir_fixed моделируйте в текущую рабочую папку. Оставьте модель открытой.

Этот рисунок показывает панель HDL Code Generation верхнего уровня диалогового окна Параметров конфигурации. Чтобы открыть это диалоговое окно, в галерее приложений нажмите HDL Coder. Появится вкладка HDL Code. В Prepare разделе нажмите Settings.

Панель HDL Code Generation состоит из основных опций, которые задают DUT, для которого требуется сгенерировать код, целевой язык и параметры папки. Настройка Generate HDL for синхронизируется с меню Code for на вкладке HDL Code. Можно также использовать кнопки на этой панели, чтобы инициировать генерацию кода и выполнить проверку совместимости. Панель HDL Code Generation состоит из различных подпанелей, которые можно использовать, чтобы задать различные настройки, связанные с сигналами синхроимпульса и сброса в настройки отчетов и оптимизации.

На панели HDL Code Generation

Поле Generate HDL for задает sfir_fixed/symmetric_fir подсистема для генерации кода.

Поле Language задает генерацию кода VHDL.

Поле Folder задает целевую папку, в которой хранятся сгенерированные коды файлы и скрипты.

Дополнительные сведения о различных параметрах на панели HDL Code Generation см. в разделе «Опции генерации HDL-кода» Диалогового окна параметров конфигурации.

Чтобы сгенерировать код, нажмите кнопку Generate. По умолчанию HDL- Coder™ генерирует VHDL- кода в целевой hdlsrc папка.

Чтобы сгенерировать код Verilog для модели:

На вкладке HDL Code нажмите Settings.

На панели HDL Code Generation для Language выберите Verilog. Оставьте другие настройки по умолчанию. Щелкните Apply и затем щелкните Generate.

HDL Coder компилирует модель перед генерацией кода. В зависимости от параметров отображения модели, таких как типы данных портов, модель может измениться во внешнем виде после генерации кода. Когда генерация кода продолжается, HDL Coder отображает сообщения о прогрессе в командной строке MATLAB с:

Ссылка на Конфигурацию модели, который указывает модель, к которой применяются Параметры конфигурации.

Ссылки на сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните ссылки.

symmetric_fir.vhd: VHDL код. Этот файл содержит определение сущности и архитектуру RTL, реализующую symmetric_fir.vhd фильтр.

symmetric_fir_compile.do: Менторская графика® ModelSim® скрипт компиляции (команда vcom) для компиляции сгенерированных VHDL- кода.

symmetric_fir_synplify.tcl: Синхронизация® скрипт синтеза.

symmetric_fir_map.txt: Этот отчет сопоставляет сгенерированные сущности с подсистемами, которые их сгенерировали. Смотрите код трассировки, используя файл отображения

Процесс завершается сообщением:

### HDL Code Generation Complete.