Когда вы запускаете рабочий процесс совместного проектирования аппаратного и программного обеспечения для однокристальных платформ, вы генерируете HDL-ядро IP для алгоритма DUT, а затем интегрируете IP-ядро в исходный проект. Смотрите рабочий процесс «Совместное проектирование аппаратного и программного обеспечения» для однокристальных платформ.

Чтобы быстро прототипировать и протестировать IP-ядро HDL на целевом компьютере, можно сгенерировать скрипт программного интерфейса. Скрипт содержит порты DUT и информацию о отображении интерфейсов, которую HDL- Coder™ использует для создания драйверов AXI и доступа к IP-ядру HDL.

Целевая платформа, такая как ZedBoard, где необходимо развернуть модель интерфейса программного обеспечения.

Последняя версия стороннего инструмента синтеза, такого как Xilinx® Vivado®. См. раздел Поддержка языка HDL и поддерживаемые Сторонние программы и оборудование. В вашем MATLAB® сеанс, установите путь к установленному инструменту синтеза при помощи hdlsetuptoolpath функция.

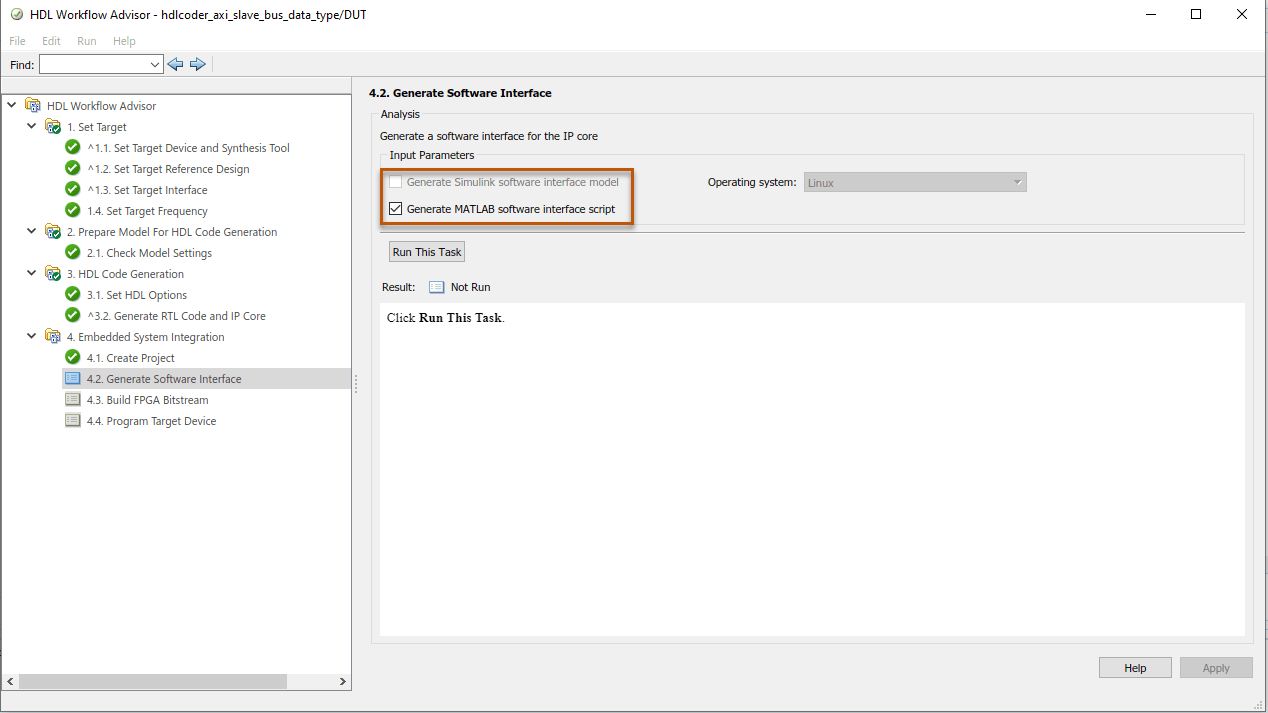

При запуске рабочего процесса генерации IP Core можно сгенерировать скрипт и модель программного интерфейса из интерфейса HDL Workflow Advisor или в командной строке.

В пользовательском интерфейсе в задаче Embedded System Integration > Generate Software Interface установите флажок Generate Software interface script.

Когда вы запускаете рабочий процесс генерации IP Core к Generate Software Interface задаче и устанавливаете флажок Generate MATLAB software interface script, генерируются два файла MATLAB:

gs_modelName_setup.m, которая является установочным скриптом, которая добавляет AXI4 подчиненный и AXI4-Stream интерфейсы. Скрипт также содержит объекты портов DUT, которые имеют имя порта, направление, тип данных и информацию о отображении интерфейсов. Затем скрипт сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, который создает целевой объект, создает экземпляры скрипта настройки gs_modelName_setup.m, а затем соединяется с целевым компьютером. Затем скрипт отправляет команды чтения и записи в сгенерированное IP-ядро HDL.

Если вы нацелены на автономные платы FPGA, вы не можете сгенерировать модель интерфейса программного обеспечения. Вместо этого можно сгенерировать скрипт программного интерфейса и протестировать IP-ядро с помощью драйвера MATLAB AXI Master.

В задаче Set Target Reference Design установите Insert JTAG MATLAB as AXI Master на on. Запустите рабочий процесс к Generate Software Interface задаче.

В Generate Software Interface задаче установите флажок Generate Software interface script и запустите эту задачу.

В командной строке экспортируйте настройки HDL Workflow Advisor в скрипт, а затем используйте эти свойства с объектом Workflow Configuration. Этот скрипт задает выполнение задачи программного интерфейса путем генерации модели и скрипта. Если вы пропустите задачу, задав для RunTaskGenerateSoftwareInterface значение false, то модель и скрипт не генерируются. Смотрите Рабочий процесс настройки и запуска генерации IP-ядра с помощью скрипта.

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateSoftwareInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

Для быстрого прототипирования и проверки функциональности IP-ядра HDL используйте скрипт программного интерфейса. Скрипт является файлом MATLAB, который генерируется на основе настроек исходного проекта и целевой таблицы интерфейса платформы. Он содержит команды, которые позволяют вам подключаться к целевому компьютеру, записывать или читать из сгенерированного IP-ядра из MATLAB. Для автономных плат FPGA используйте скрипт сгенерированного программного обеспечения интерфейса, чтобы проверить функциональность HDL-ядра IP с помощью MATLAB AXI Master.

Скрипт интерфейса программного обеспечения имеет то же имя что и ваша исходная модель с префиксом gs_ и постфикс _interface. Скрипт создает экземпляр функции настройки, которая генерируется, когда вы активируете генерацию скрипта интерфейса программного обеспечения. Для примера этот код показывает функцию настройки, сгенерированную для модели hdlcoder_sfir_fixed_stream.slx, с предварительно заданными настройками исходного проекта и интерфейса целевой платформы. Функция setup содержит команды для AXI4 ведомого и AXI4-Stream интерфейсов, которые HDL Coder использует для управления портами DUT в сгенерированном IP-ядре HDL, которые сопоставлены с соответствующими интерфейсами.

function gs_hdlcoder_sfir_fixed_stream_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 09:13:05 on 10/07/2020. % This function was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Run this function on an "fpga" object to configure it with % the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4-Lite addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000); hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100"); hPort_h_in2 = hdlcoder.DUTPort("h_in2", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x104"); hPort_h_in3 = hdlcoder.DUTPort("h_in3", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x108"); hPort_h_in4 = hdlcoder.DUTPort("h_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x10C"); mapPort(hFPGA, [hPort_h_in1, hPort_h_in2, hPort_h_in3, hPort_h_in4]); %% AXI4-Stream addAXI4StreamInterface(hFPGA, ... "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "WriteFrameLength", 1024, ... "ReadEnable", true, ... "ReadFrameLength", 1024); hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]); end

Это пример функции настройки для модели с шиной, сопоставленной с AXI4 подчиненным интерфейсом. Как показано в скрипте, элементы шины представлены как подпорты hdlcoder.DUTPort объекты.

function gs_AXI4SlaveMultipleBus_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 16:20:32 on 16/11/2020. % This function was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Run this function on an "fpga" object to configure it with the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4 addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4", ... "BaseAddress", 0x400D0000, ... "AddressRange", 0x10000); hPort_bus1_in_scalar_in1 = hdlcoder.DUTPort("scalar_in1", ... "Direction", "IN", ... "DataType", numerictype('single'), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x100"); hPort_bus1_in_scalar_in2 = hdlcoder.DUTPort("scalar_in2", ... "Direction", "IN", ... "DataType", numerictype(1,8,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x104"); hPort_bus1_in_scalar_in3 = hdlcoder.DUTPort("scalar_in3", ... "Direction", "IN", ... "DataType", numerictype(1,32,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x108"); hPort_bus1_in_scalar_in4 = hdlcoder.DUTPort("scalar_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x10C"); hPort_bus1_in_vector_in = hdlcoder.DUTPort("vector_in", ... "Direction", "IN", ... "DataType", numerictype(0,32,0), ... "Dimension", [1 2], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x110"); hPort_bus1_in = hdlcoder.DUTPort("bus1_in", ... "Direction", "IN", ... "DataType", "Bus", ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "SubPorts", [hPort_bus1_in_scalar_in1, hPort_bus1_in_scalar_in2, hPort_bus1_in_scalar_in3, hPort_bus1_in_scalar_in4, hPort_bus1_in_vector_in]);

Скрипт интерфейса программного обеспечения создает экземпляры этой функции настройки для подключения к целевому объекту и отправки команд чтения или записи. Можно раскомментировать и отправить значимые данные при помощи входов в DUT в вашей исходной модели. После взаимодействия с оборудованием скрипт отключается от аппаратного ресурса, связанного с fpga объект.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2020b) at 09:13:10 on 10/07/2020. % This script was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Use this script to access DUT ports in the design mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % % To write to input ports, use the "writePort" command and specify port name and input data. % The input data will be cast to the DUT port's data type before writing. % % To read from output ports, use the "readPort" command and specify the port name. % The output data will be returned with the same data type as the DUT port. % % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures "fpga" object with same interfaces as the generated IP core gs_hdlcoder_sfir_fixed_stream_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4-Lite writePort(hFPGA, "h_in1", zeros([1 1])); writePort(hFPGA, "h_in2", zeros([1 1])); writePort(hFPGA, "h_in3", zeros([1 1])); writePort(hFPGA, "h_in4", zeros([1 1])); %% AXI4-Stream writePort(hFPGA, "x_in_data", zeros([1 1024])); data_y_out_data = readPort(hFPGA, "y_out_data"); %% Release hardware resources release(hFPGA)

Смотрите проект прототипа FPGA на оборудовании с Live Data при помощи команд MATLAB

Это пример скрипта программного интерфейса для чтения и записи данных для моделей, которые имеют типы данных шины, сопоставленные с AXI4 подчиненными интерфейсами.

Чтобы записать в шинный порт, можно либо:

Запись в отдельные подпорты путем определения полного имени подпорта, такого как bus1_in.scalar_in1.

Запись на всю шину путем определения верхнего имени порта, например bus1_in. Передайте данные, которые будут записаны как struct, имена которых совпадают с именами подпортов. Не все имена подпортов должны быть частью struct. Подпорты без соответствующих структурных полей пропускаются при записи в порт.

Для чтения с автобусного порта можно либо:

Считайте отдельный подпорт, указав полное имя подпорта, например bus1_out.scalar.in1.

Считайте весь порт шины, указав верхнее имя порта, например bus1_out.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2021a) at 16:20:33 on 16/11/2020. % This script was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Use this script to access DUT ports in the design that were mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % To write to input ports, use the "writePort" command and specify the port name and input data. The input data will be cast to the DUT port's data type before writing. % To read from output ports, use the "readPort" command and specify the port name. The output data will be returned with the same data type as the DUT port. % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures the "fpga" object with the same interfaces as the generated IP core gs_AXI4SlaveMultipleBus_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4 % There are two ways to write a DUT bus ports % (1). Prepare a struct value and write it to the whole bus port. writePort(hFPGA, "bus1_in", struct()); % (2). Prepare a value for each member of the bus and write it individually. writePort(hFPGA, "bus1_in.scalar_in1", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in2", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in3", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in4", zeros([1 1])); writePort(hFPGA, "bus1_in.vector_in", zeros([1 2]));