Быстрое прототипирование ядра IP HDL путем взаимодействия с целевой платой через Ethernet или JTAG. Используйте подключение Ethernet для плат с процессором ARM. Используйте соединение JTAG для плат, не имеющих процессора ARM.

Целевая платформа, такая как ZedBoard™, где вы развертываете модель программного интерфейса

Последняя версия стороннего инструмента синтеза, такого как Xilinx® Vivado®. См. раздел Поддержка языка HDL и поддерживаемые Сторонние программы и оборудование. В вашем MATLAB® сеанс, установите путь к установленному инструменту синтеза при помощи hdlsetuptoolpath функция.

Чтобы использовать подключение на основе Ethernet к вашим целевым аппаратным платам, которые имеют встроенный ARM-процессор, можно либо сгенерировать скрипт программного интерфейса, либо создать пользовательский программный скрипт. Перед настройкой интерфейса на базе Ethernet настройте карту SD платы с помощью MathWorks® изображение микропрограммного обеспечения. Чтобы настроить изображение микропрограммного обеспечения для целевой платы:

Для Intel® соответствующие платы, см. Guided SD Card Setup (HDL Coder Support Package for Intel SoC Devices)

Для плат, связанных с Xilinx, смотрите Guided SD Card Setup (HDL Coder Support Package for Xilinx Zynq Platform).

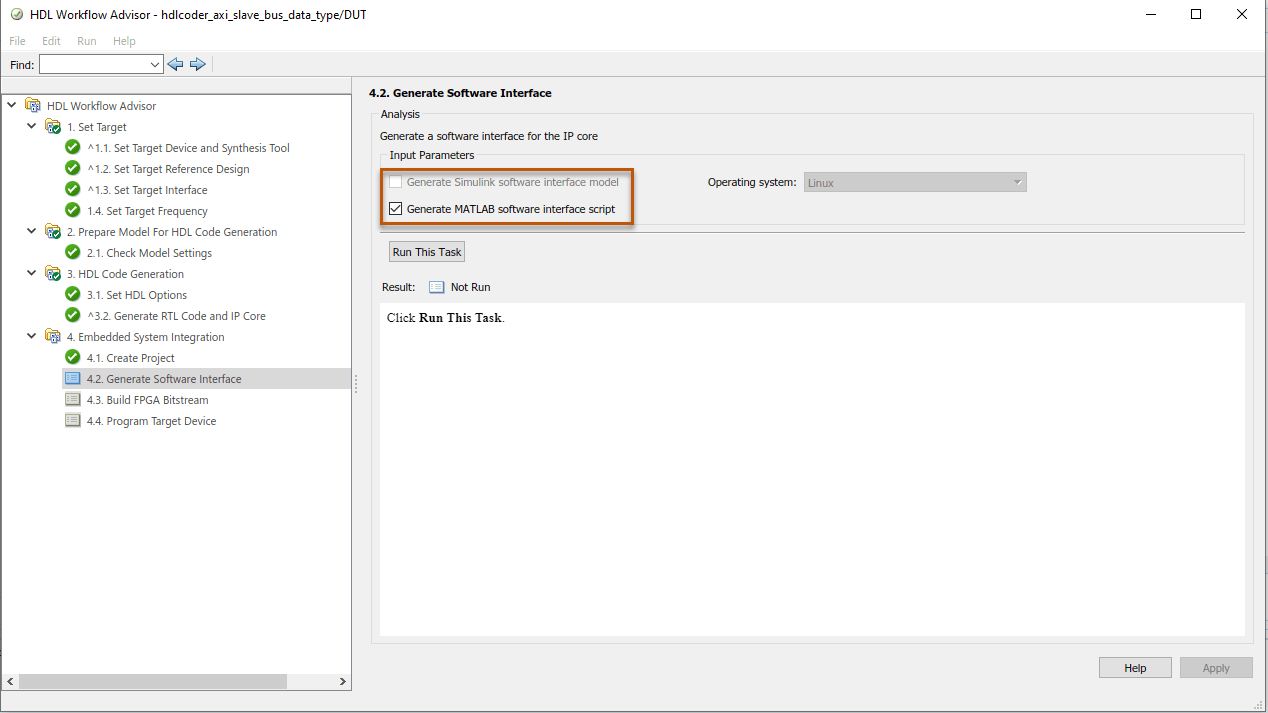

Когда вы запускаете Generate Software Interface задачу и устанавливаете флажок Generate MATLAB software interface script.

Сгенерированные файлы MATLAB:

gs_modelName_setup.m, которая является установочным скриптом, которая добавляет AXI4 подчиненный и AXI4-Stream интерфейсы. Скрипт также содержит объекты портов DUT, которые имеют имя порта, направление, тип данных и информацию о отображении интерфейсов. Затем скрипт сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, который создает целевой объект, создает экземпляры скрипта настройки gs_modelName_setup.m, а затем соединяется с целевым компьютером. Затем скрипт отправляет команды чтения и записи в сгенерированное IP-ядро HDL.

Для быстрого прототипирования настройте скрипт интерфейса программного обеспечения или создайте свой собственный скрипт на основе того, как вы изменяете свой оригинальный проект. Настройте скрипт, чтобы указать:

Целевой объект для другого поставщика FPGA.

Дополнительные интерфейсы или конфигурация существующих интерфейсов на основе изменений вашего исходного проекта. HDL Coder™ использует эту информацию для создания драйверов IIO для доступа к IP-ядру HDL.

Дополнительные объекты портов DUT или удалите существующие объекты в зависимости от способа изменения проекта, а затем измените информацию отображения соответственно.

Входные данные для записи в порты DUT и выходные данные для чтения из портов.

Вы можете настроить скрипт сгенерированного программного обеспечения или создать свой собственный скрипт программного интерфейса. Чтобы создать пользовательский программный скрипт:

Создайте fpga объект для целевого устройства и хранения в hFPGA.

hFPGA = fpga("Xilinx")

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Использование целевого устройства Intel:

hFPGA = fpga("Intel")

hFPGA =

fpga with properties:

Vendor: "Intel"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Сконфигурируйте интерфейсы AXI, чтобы сопоставить порты DUT в сгенерированном IP-ядре HDL. Можно добавить AXI4 подчиненный и AXI4-Stream интерфейсы. Чтобы добавить AXI4 подчиненные интерфейсы, используйте addAXI4SlaveInterface функция.

addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mmwr0", ... "ReadDeviceName", "mwipcore0:mmrd0");

Чтобы добавить AXI4-Stream интерфейсы, используйте addAXI4StreamInterface функция.

addAXI4StreamInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "ReadEnable", true, ... "WriteFrameLength", 1024, ... "ReadFrameLength", 1024, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mm2s0", ... "ReadDeviceName", "mwipcore0:s2mm0");

Заданная информация о отображении интерфейсов сохранена как свойство на fpga объект, hFPGA.

hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]Для автономных плат FPGA, не имеющих встроенного процессора ARM, можно создать объект, а затем использовать aximaster объект. Затем используйте этот объект в качестве драйвера для addAXI4SlaveInterface функция. The aximaster Для объекта требуется пакет поддержки HDL Verifier™ для плат Intel или Xilinx FPGA.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Укажите информацию о портах DUT в сгенерированном IP-ядре HDL в качестве порта, объектном массиве при помощи hdlcoder.DUTPort объект. Объект представляет порты вашего DUT на целевом компьютере.

hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100")

hPort_h_in1 =

DUTPort with properties:

Name: "h_in1"

Direction: IN

DataType: [1×1 embedded.numerictype]

Dimension: [1 1]

IOInterface: "AXI4-Lite"

IOInterfaceMapping: "0x100"Чтобы записать или считать из портов DUT в сгенерированном IP-ядре HDL, сопоставьте порты с интерфейсом AXI с помощью mapPort функция. После сопоставления портов с интерфейсами эта информация сохраняется на fpga объект как Interfaces свойство.

mapPort(hFPGA, hPort_h_in1); hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

Можно также задать эту информацию для портов, сопоставленных с AXI4-Stream интерфейсами.

hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream");

Чтобы записать или считать из портов DUT в сгенерированном IP-ядре HDL, сопоставьте порты с интерфейсом AXI с помощью mapPort функция.

mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]);

fpga объект как Interfaces свойство.hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

AXI4Stream with properties:

InterfaceID: "AXI4-Stream"

WriteEnable: 1

ReadEnable: 1

WriteFrameLength: 1024

ReadFrameLength: 1024

WriteDriver: [1×1 fpgaio.driver.AXIStreamIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIStreamIIORead]

InputPorts: "x_in_data"

OutputPorts: "y_out_data"

Чтобы протестировать функциональность ядра IP HDL, используйте readPort и writePort функции для записи данных в или чтения данных из этих портов.

writePort(hFPGA, "h_in1", 5); writePort(hFPGA, "x_in", sin(linspace(0, 2*pi, 1024))); data = readPort(hFPGA, "y_out");

После тестирования IP-ядра HDL можно выпустить аппаратный ресурс, сопоставленный с fpga объект при помощи release функция.

release(hFPGA)

Для примера создания пользовательского скрипта интерфейса и прототипирования вашего проекта на целевой плате FPGA через подключение Ethernet, смотрите Prototype FPGA Design on Hardware with Live Data by Using MATLAB Commands.

Для автономных плат FPGA, не имеющих встроенного процессора ARM, можно вставить JTAG MATLAB в качестве AXI Master IP в исходный проект. Создайте скрипт, который использует aximaster объект, который соединяется с IP по физическому кабелю JTAG. Этот скрипт включает команды чтения и записи в подчиненные местоположения памяти из командной строки MATLAB.

Для использования MATLAB в качестве мастера AXI:

Установите пакеты аппаратной поддержки HDL Verifier.

Не целевые автономные платы, не имеющие hRD.AXI4SlaveInterface функциональность или платы, основанные на Xilinx ISE.

Когда вы запускаете рабочий процесс генерации ядра IP, в задаче Set Target > Set Target Reference Design, выберите Default system для Reference Design и установите Insert JTAG MATLAB as AXI Master on.

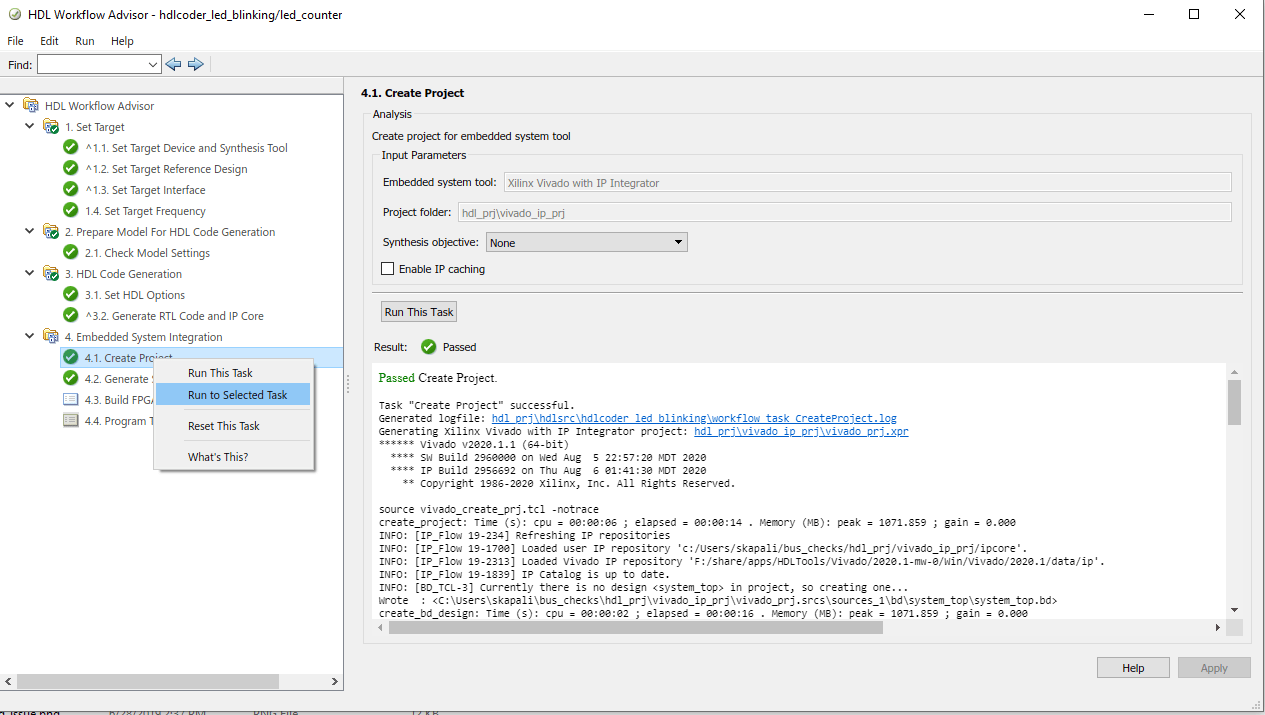

Чтобы сгенерировать IP Core и создать проект с AXI Master IP, щелкните правой кнопкой мыши Create Project задачу и выберите Run to Selected Task.

Теперь можно взаимодействовать с целевой платой FPGA, используя JTAG MATLAB в качестве функции AXI Master. Создайте объект при помощи aximaster объект. Используйте созданный объект в качестве драйвера для addAXI4SlaveInterface функция.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Для примера взаимодействия с целевой платой через JTAG смотрите Использование JTAG MATLAB в качестве AXI Master HDL Coder для управления сгенерированным IP-ядром.