Чтобы использовать эту функцию, установка должна включать лицензию HDL- Verifier™.

Убедитесь, что подсистема DUT не имеет несвязанных выходных портов. См. «Завершение работы несоединенных блоков Выходов и Использование блоков с комментариями».

Модель косимуляции является автоматически сгенерированной Simulink® модель, сконфигурированная для симуляции Simulink и косимуляции вашего проекта с помощью Симулятора HDL. HDL Coder™ поддерживает автоматическую генерацию модели косимуляции в рамках процесса генерации испытательного стенда.

Модель косимуляции включает:

Поведенческая модель вашего проекта, реализованная в подсистеме Simulink.

Соответствующий HDL Cosimulation блок, настроенный для косимуляции проекта с помощью HDL Verifier. HDL Coder настраивает блок HDL Cosimulation для использования с Mentor Graphics® ModelSim® или Cadence Incisive®.

Тестовые входные данные, рассчитанные из заданного вами стимула испытательного стенда.

Блоки Scope, которые позволяют вам наблюдать и сравнивать выходы DUT и HDL cosimulation, и любую ошибку между этими сигналами.

Блоки Goto и From, которые захватывают входные и ответные сигналы от DUT и используют эти сигналы для управления косимуляцией.

Механизм сравнения/утверждения, который сообщает о расхождениях между исходным выходом DUT и выходом косимуляции.

В дополнение к сгенерированной модели HDL Coder генерирует TCL скрипт, который запускает и конфигурирует ваш инструмент косимуляции. Комментарии в цикле документа файла скрипта, сброс и другая информация о синхронизирующем сигнале, заданная кодером для инструмента косимуляции.

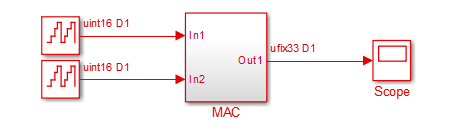

Этот пример демонстрирует процесс генерации модели косимуляции. Модель примера, hdl_cosim_demo1, реализует простой алгоритм умножения и накопления (MAC). Откройте модель, введя имя в MATLAB® командная строка:

hdl_cosim_demo1

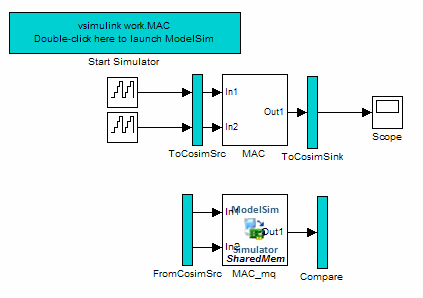

Следующий рисунок показывает модель верхнего уровня.

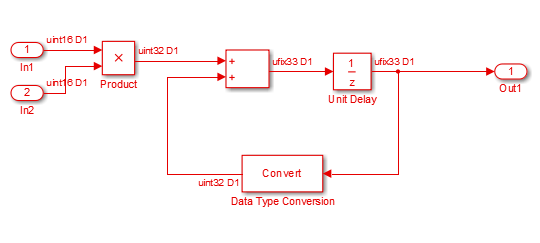

DUT является подсистемой MAC.

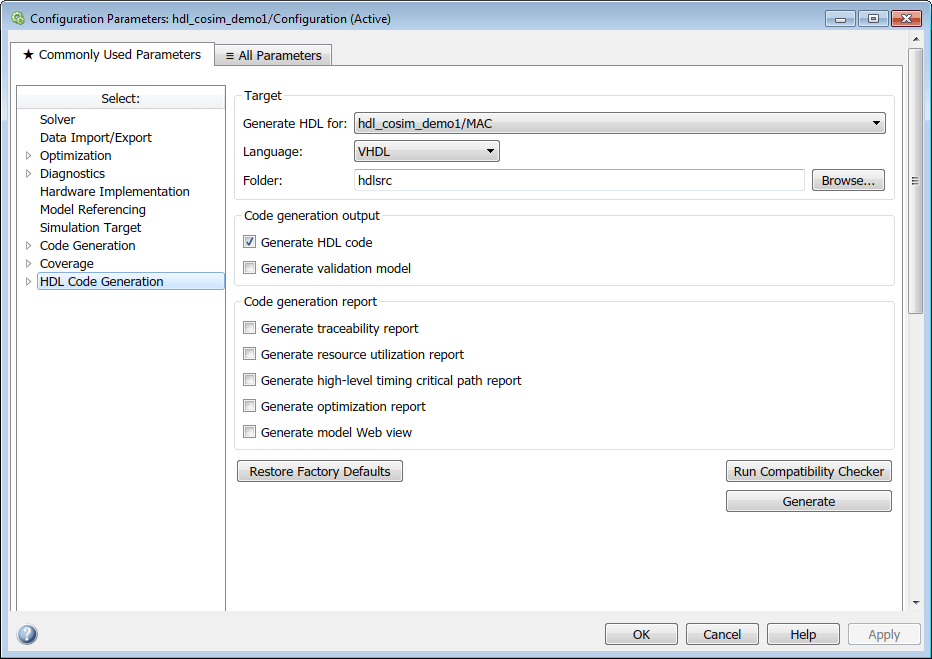

Генерация модели косимуляции происходит во время генерации испытательного стенда. В качестве наилучшей практики сгенерируйте HDL-код перед генерацией испытательного стенда следующим образом:

На панели HDL Code Generation диалогового окна Параметры конфигурации выберите DUT для генерации кода. В этом случае это hdl_cosim_demo1/MAC.

Нажмите Apply.

Нажмите Generate. HDL Coder отображает сообщения о прогрессе, как показано на следующем списке:

### Applying HDL Code Generation Control Statements ### Starting HDL Check. ### HDL Check Complete with 0 error, 0 warning and 0 message. ### Begin VHDL Code Generation ### Working on hdl_cosim_demo1/MAC as hdlsrc\MAC.vhd ### HDL Code Generation Complete.

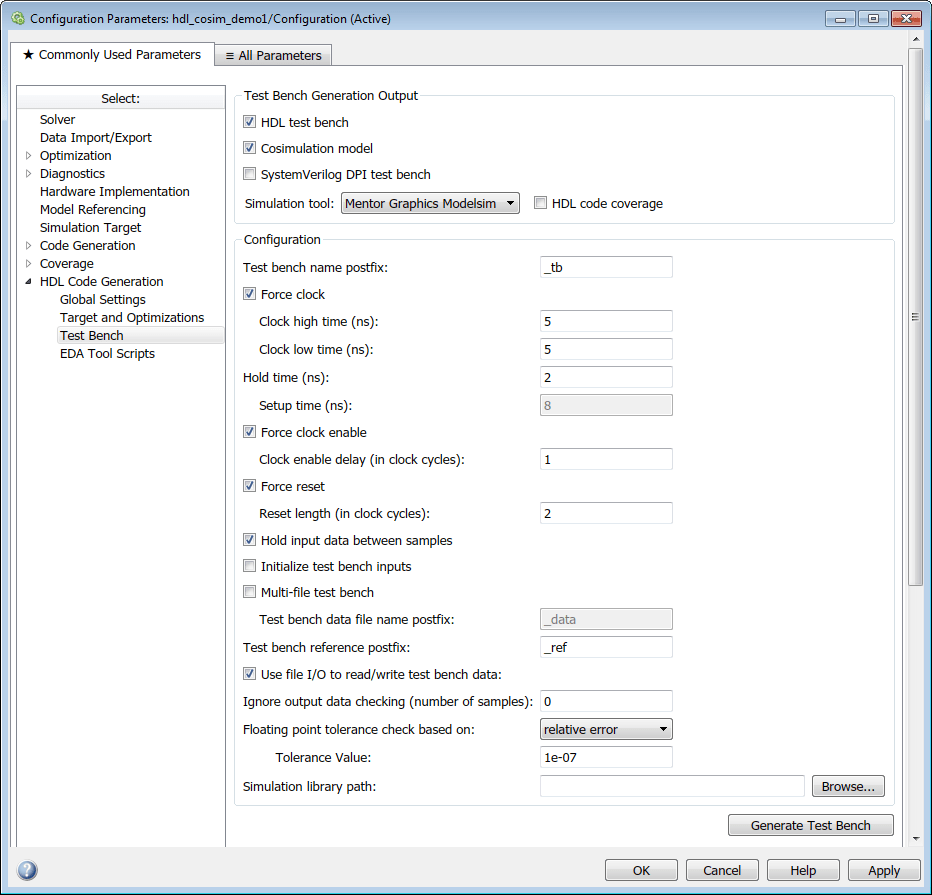

Затем сконфигурируйте опции испытательного стенда, чтобы включить генерацию модели косимуляции:

Выберите панель HDL Code Generation > Test Bench диалогового окна Параметры конфигурации.

Установите флажок Cosimulation model. Затем выберите Simulation tool в раскрывающемся меню.

Сконфигурируйте необходимые опции испытательного стенда. HDL Coder записывает опцию настройки в сгенерированный файл скрипта (см. Файл сценария косимуляции).

Нажмите Apply.

Затем сгенерируйте испытательный стенд и модель косимуляции:

В нижней части панели Test Bench нажмите Generate Test Bench. HDL Coder отображает сообщения о прогрессе, как показано на следующем списке:

### Begin TestBench Generation ### Generating new cosimulation model: gm_hdl_cosim_demo1_mq0.mdl ### Generating new cosimulation tcl script: hdlsrc/gm_hdl_cosim_demo1_mq0_tcl.m ### Cosimulation Model Generation Complete. ### Generating Test bench: hdlsrc\MAC_tb.vhd ### Please wait ... ### HDL TestBench Generation Complete.

Когда генерация испытательного стенда завершается, HDL Coder открывает сгенерированную косимулированную модель. Следующий рисунок показывает сгенерированную модель.

Сохраните сгенерированную модель. Сгенерированная модель существует только в памяти, если вы не сохраняете ее.

Как указано сообщениями генерации кода, HDL Coder генерирует следующие файлы в сложение с обычным HDL-файлом испытательного стенда:

Модель косимуляции (gm_hdl_cosim_demo1_mq)

Файл, который содержит TCL скрипт косимуляции и информацию о настройках модели косимуляции (gm_hdl_cosim_demo1_mq_tcl.m)

Сгенерированные имена файлов получают из имени модели, как описано в Соглашениях об именовании для сгенерированных моделей косимуляции и скриптов.

В следующем разделе «Структура сгенерированной модели» описываются функции модели. Прежде чем запускать косимуляцию, ознакомьтесь с этими функциями.

Можно настроить и запустить косимуляцию с помощью элементов управления, расположенных в сгенерированной модели. В этом разделе рассматривается модель, сгенерированная из примера MAC-подсистемы.

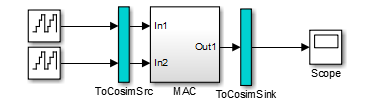

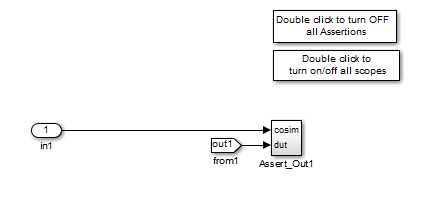

Модель содержит два параллельных пути сигнала. simulation path, расположенный в верхней половине окна модели, почти идентичен исходному DUT. Цель пути симуляции состоит в том, чтобы выполнить нормальное моделирование Simulink и предоставить опорный сигнал для сравнения с результатами косимуляции. Следующий рисунок показывает путь симуляции.

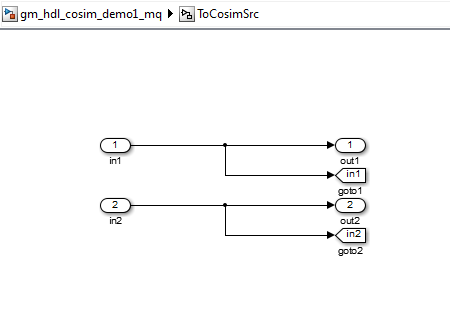

Две подсистемы отмечены ToCosimSrc и ToCosimSink не изменяйте эффективность пути симуляции. Их цель - захватить входные и ответные сигналы DUT и направить их к блоку HDL cosimulation (см. «Маршрутизация сигнала между путями симуляции и косимуляции»).

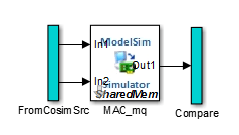

cosimulation path, расположенный в нижней половине окна модели, содержит сгенерированный блок HDL Cosimulation. Следующий рисунок показывает путь косимуляции.

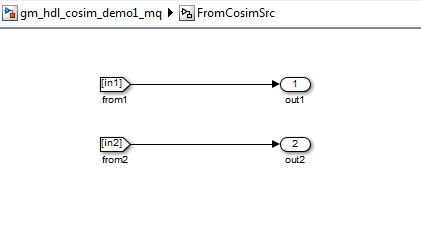

The FromCosimSrc подсистема получает те же входные сигналы, которые управляют DUT. В gm_hdl_cosim_demo1_mq0 модель, подсистема просто передает входы в блок HDL Cosimulation. Сигналы некоторых других типов данных требуют дальнейшей обработки на этом этапе (см. «Маршрутизация сигнала между путями симуляции и косимуляции»).

The Compare подсистема в конце пути косимуляции сравнивает выход косимуляции с выходом ссылки, полученным путем симуляции. Если сравнение обнаруживает расхождение, блок Assertion в Compare подсистема отображает предупреждающее сообщение. При желании можно отключить утверждения и управлять другими операциями Compare подсистема. Для получения дополнительной информации смотрите Утверждения контроллинга и Возможностей Отображений.

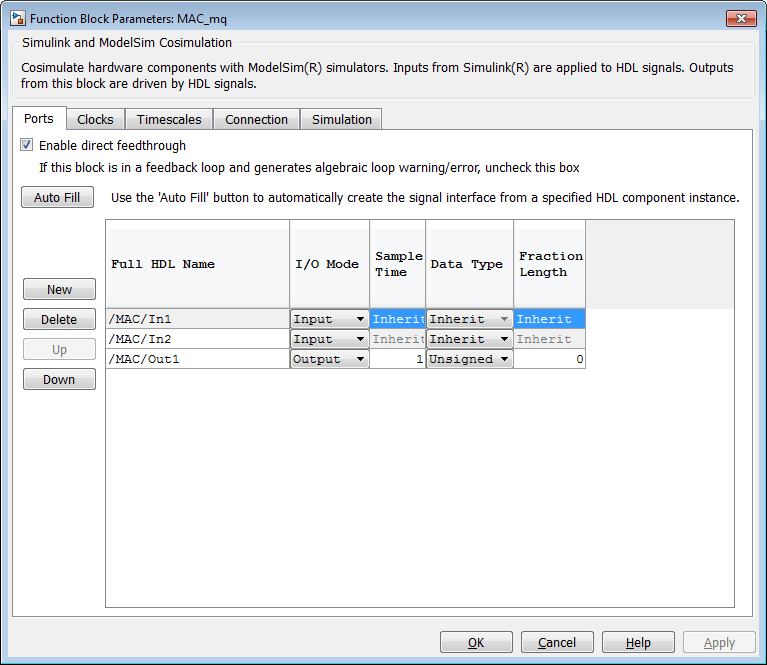

HDL Coder заполняет HDL Cosimulation блок скомпилированным интерфейсом ввода-вывода DUT. Следующий рисунок показывает Ports панель Mac_mq HDL Cosimulation блок.

HDL Coder устанавливает Full HDL Name, Sample Time, Data Type и другие поля в соответствии с требованиями модели. HDL Coder также настраивает другие параметры блоков HDL Cosimulation под панелями Timescales и Tcl.

Совет

HDL Coder конфигурирует сгенерированный HDL Cosimulation блок для Shared Memory метод соединения.

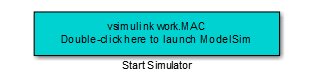

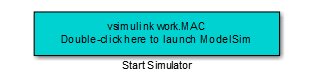

При двойном клике элемента управления Start Simulator запускается выбранный инструмент косимуляции и передается в команде запуска инструменту. Значок Start Simulator отображает команду запуска, как показано на следующем рисунке.

Команды, выполненные при двойном клике запуска значка Start Simulator и настройке инструмента косимуляции, но они не запускают фактическую косимуляцию. Запуск косимуляции описывает, как запустить косимуляцию с сгенерированной моделью.

Сгенерированная модель маршрутизирует сигналы между путями симуляции и косимуляции, используя блоки Goto и From. Для примера Goto блокирует в ToCosimSrc подсистема маршрутизирует каждый входной сигнал DUT к соответствующему блоку From в FromCosimSrc подсистема. Следующие рисунки показывают блоки Goto и From в каждой подсистеме.

Предыдущие рисунки показывают простые скалярные входы. Сигналы комплексного и векторного типов данных требуют дальнейшей обработки. Смотрите Комплексные и Векторные Сигналы в Сгенерированной Модели Косимуляции для получения дополнительной информации.

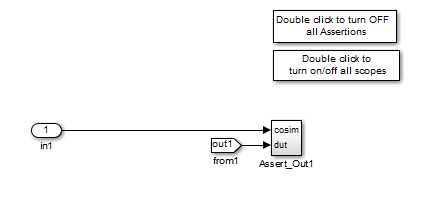

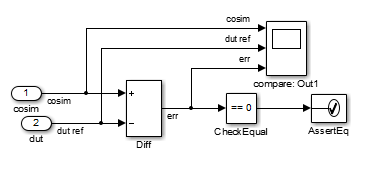

The Compare подсистема позволяет управлять отображением сигналов в возможностях и предупреждающих сообщений от утверждений. Следующий рисунок показывает Compare подсистема для gm_hdl_cosim_demo1_mq0 модель.

Для каждого выхода DUT HDL Coder генерирует подсистему проверки типа «assertion» (Assert_OutN ). Подсистема вычисляет различие (err) между исходным выходом DUT (dut ref) и соответствующий выход косимуляции (cosim). Подсистема маршрутизирует результат сравнения в блок Assertion. Если результат сравнения не равен нулю, блок Assertion сообщает о несоответствии.

Следующий рисунок показывает Assert_Out1 подсистема для gm_hdl_cosim_demo1_mq0 модель.

Эта подсистема также маршрутизирует dut ref, cosim, и err сигналы в возможности для отображения на верхнем уровне модели.

По умолчанию сгенерированная модель косимуляции включает все утверждения и отображает все Возможности. Используйте кнопки на Compare подсистема, чтобы отключить утверждения или скрыть Возможности.

Совет

Сообщения об утверждениях являются предупреждениями и не останавливают симуляцию.

Чтобы запустить косимуляцию с сгенерированной моделью:

Дважды кликните Compare подсистема для настройки возможностей и параметров проверки.

Если вы хотите отключить отображения Scope или предупреждения о потерях перед началом косимуляции, используйте кнопки на Compare подсистема (показана на следующем рисунке).

Дважды кликните элемент управления Start Simulator.

Управление Start Simulator запускает ваш Симулятор HDL (в этом случае HDL Verifier для использования с Mentor Graphics ModelSim).

Симулятор HDL в свою очередь выполняет скрипт запуска. В этом случае скрипт запуска состоит из команд TCL, расположенных в gm_hdl_cosim_demo1_mq0_tcl.m. Когда Симулятор HDL завершает выполнение скрипта запуска, оно отображает сообщение, подобное следующему.

# Ready for cosimulation...

В редакторе Simulink для сгенерированной модели запустите симуляцию.

Когда запуски косимуляция, Симулятор HDL отображает сообщения, такие как следующее.

# Running Simulink Cosimulation block. # Chip Name: --> hdl_cosim_demo1/MAC # Target language: --> vhdl # Target directory: --> hdlsrc # Fri Jun 05 4:26:34 PM Eastern Daylight Time 2009 # Simulation halt requested by foreign interface. # done

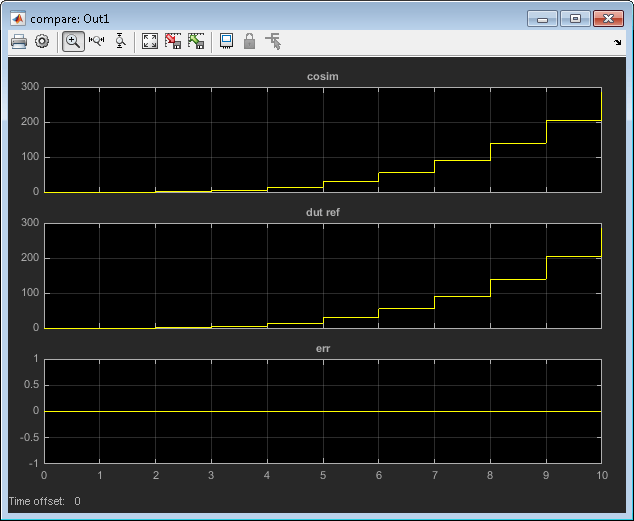

В конце косимуляции, если вы включили Возможности отображений, возможности сравнения отображают следующие сигналы:

cosim: Результирующий сигнал, выводимый блоком HDL Cosimulation.

dut ref: Ссылка выхода сигнал от DUT.

err: Различие (ошибка) между этими двумя выходами.

Следующий рисунок показывает эти сигналы.

Сгенерированный файл скрипта состоит из двух разделов:

Раздел комментария, в котором документируются параметры модели, релевантные для косимуляции.

Функция, которая хранит несколько строк кода TCL в переменную, tclCmds. Инструменты косимуляции выполняют эти команды, когда вы запускаете косимуляцию.

В следующем списке показан раздел комментариев файла скрипта, сгенерированного для hdl_cosim_demo1 модель:

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Auto generated cosimulation 'tclstart' script %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Source Model : hdl_cosim_demo1.mdl % Generated Model : gm_hdl_cosim_demo1.mdl % Cosimulation Model : gm_hdl_cosim_demo1_mq.mdl % % Source DUT : gm_hdl_cosim_demo1_mq/MAC % Cosimulation DUT : gm_hdl_cosim_demo1_mq/MAC_mq % % File Location : hdlsrc/gm_hdl_cosim_demo1_mq_tcl.m % Created : 2009-06-16 10:51:01 % % Generated by MATLAB 7.9 and HDL Coder 1.6 %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ClockName : clk % ResetName : reset % ClockEnableName : clk_enable % % ClockLowTime : 5ns % ClockHighTime : 5ns % ClockPeriod : 10ns % % ResetLength : 20ns % ClockEnableDelay : 10ns % HoldTime : 2ns %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ModelBaseSampleTime : 1 % OverClockFactor : 1 %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Mapping of DutBaseSampleTime to ClockPeriod % % N = (ClockPeriod / DutBaseSampleTime) * OverClockFactor % 1 sec in Simulink corresponds to 10ns in the HDL % Simulator(N = 10) % %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ResetHighAt : (ClockLowTime + ResetLength + HoldTime) % ResetRiseEdge : 27ns % ResetType : async % ResetAssertedLevel : 1 % % ClockEnableHighAt : (ClockLowTime + ResetLength + ClockEnableDelay + HoldTime) % ClockEnableRiseEdge : 37ns %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

Раздел комментариев включает следующие подразделы:

Комментарии к заголовку: В этом разделе описываются имена файлов для исходных и сгенерированных моделей, а также исходный и сгенерированный DUT.

Испытательные стенды: Этот раздел документирует makehdltb значения свойств, которые влияют на генерацию модели косимуляции. Сгенерированный TCL скрипт использует эти значения для инициализации инструмента косимуляции.

Шаг расчета: В следующих двух разделах документируется базовый шаг расчета и коэффициент избыточной дискретизации модели. HDL Coder использует ModelBaseSampleTime и OverClockFactor сопоставить тактовый период модели с периодом HDL-косимуляции.

Часы, активация и сброс формы волны: Этот раздел документирует расчеты коэффициента заполнения clk, clk_enable, и reset сигналы.

В следующем списке показан раздел команд файла скрипта, сгенерированного для hdl_cosim_demo1 модель:

function tclCmds = gm_hdl_cosim_demo1_mq_tcl

tclCmds = {

'do MAC_compile.do',...% Compile the generated code

'vsimulink work.MAC',...% Initiate cosimulation

'add wave /MAC/clk',...% Add wave commands for chip input signals

'add wave /MAC/reset',...

'add wave /MAC/clk_enable',...

'add wave /MAC/In1',...

'add wave /MAC/In2',...

'add wave /MAC/ce_out',...% Add wave commands for chip output signals

'add wave /MAC/Out1',...

'set UserTimeUnit ns',...% Set simulation time unit

'puts ""',...

'puts "Ready for cosimulation..."',...

};

endВходные сигналы комплексных или векторных типов данных требуют вставки дополнительных элементов в путь косимуляции. В этом разделе описываются эти элементы.

Сгенерированная модель косимуляции автоматически разбивает комплексные входы на вещественные и мнимые части. Следующий рисунок показывает FromCosimSrc подсистема, которая принимает два комплексных входных сигналов. Подсистема разбивает входы на действительные и мнимые части перед передачей их в выходы подсистемы.

Модель поддерживает разделение вещественных и мнимых компонентов на протяжении пути косимуляции. The Compare подсистема выполняет отдельные сравнения и отдельные отображения возможностей для вещественных и мнимых компонентов сигнала.

Сгенерированная модель косимуляции уплощает векторные входы. Следующий рисунок показывает FromCosimSrc подсистема, которая принимает два векторных входных сигналов размерности 2. Подсистема уплощает входы в скаляры, прежде чем передать их в выходы подсистемы.

Чтобы сгенерировать модель косимуляции из командной строки, передайте GenerateCosimModel свойство для makehdltb функция. GenerateCosimModel принимает одно из следующих значений свойств:

'ModelSim' : сгенерируйте модель косимуляции, сконфигурированную для HDL Verifier для использования с Mentor Graphics ModelSim.

'Incisive': сгенерируйте модель косимуляции, сконфигурированную для HDL Verifier для использования с Cadence Incisive.

По следующей команде, makehdltb генерирует модель косимуляции, сконфигурированную для HDL Verifier для использования с Mentor Graphics ModelSim.

makehdltb('hdl_cosim_demo1/MAC','GenerateCosimModel','ModelSim');

Соглашение об именовании для сгенерированных моделей косимуляции

prefix_ modelname_toolid_suffix, где:

prefix - строка gm.

modelname - имя генерирующей модели.

toolid - идентификатор, указывающий на Симулятор HDL, выбранную опцией Cosimulation model for use with:. Допустимые toolid строки 'mq' и 'in'.

suffix является целым числом, которое предоставляет каждой сгенерированной модели уникальное имя. Суффикс увеличивается с каждым последующим генерацией испытательного стенда для данной модели. Для примера, если исходное имя модели test, затем последовательность сгенерированных имен моделей косимуляции gm_test_toolid_0, gm_test_toolid_1и так далее.

Соглашение об именовании для сгенерированных скриптов косимуляции то же самое, что и для моделей, за исключением того, что расширение имени файла .m.

Когда вы конфигурируете модель для генерации модели косимуляции, наблюдайте следующие ограничения:

Явным образом задайте шаги расчета исходных блоков для DUT в пути симуляции. Использование шага расчета по умолчанию (-1) в исходных блоках могут вызвать проблемы распространения шага расчета в пути косимуляции сгенерированной модели.

Программное обеспечение HDL Coder не поддерживает непрерывные шаги расчета для генерации модели косимуляции. Не используйте шаги расчета 0 или Inf в исходных блоках в пути симуляции.

Если вы задаете Clock Inputs MultipleHDL Coder не поддерживает генерацию модели косимуляции.

Комбинаторные выходные пути (вызванные отсутствием регистров в сгенерированном коде) имеют задержку одного дополнительного цикла в косимуляции. Чтобы избежать расхождения в сравнении выходных выходов симуляции и косимуляции, автоматически выбирается опция Allow direct feedthrough на панели Ports блока HDL Cosimulation.

Кроме того, можно избежать задержки путем определения выходной конвейеризации (см. OutputPipeline). Это позволит полностью зарегистрировать выходы во время генерации кода.

Двойные типы данных не поддерживаются для блока HDL Cosimulation. Избегайте использования двойных типов данных в пути симуляции при генерации HDL-кода и модели косимуляции.