Настройте рабочую папку с возможностью записи вне MATLAB® папка установки для хранения файлов, которые будут сгенерированы по завершении учебной работы. Учебные инструкции предполагают, что вы создаете папку hdlfilter_tutorials на приводе C.

В этом руководстве приведены инструкции по разработке оптимизированного квантованного конечная импульсная характеристика в дискретном времени, генерации кода Verilog для фильтра и проверке кода Verilog с помощью сгенерированного испытательного стенда.

В этом разделе предполагается, что вы знакомы с пользовательским интерфейсом MATLAB и Filter Designer.

Запустите программное обеспечение MATLAB.

Установите текущую папку в папку, созданную в разделе Создать папку для файлов учебного пособия.

Запустите Filter Designer путем ввода filterDesigner команда в Командном Окне MATLAB. Откроется диалоговое окно Создания фильтра & Analysis Tool.

В диалоговом окне Создание фильтра & Анализ Инструмента установите следующие опции фильтра:

| Опция | Значение |

|---|---|

| Response Type | Lowpass |

| Design Method | FIR Equiripple |

| Filter Order | Minimum order |

| Options | Density Factor: 20 |

| Frequency Specifications | Units: Fs: Fpass: Fstop: 12000 |

| Magnitude Specifications | Units: Apass: Astop: |

Эти настройки предназначены для создания фильтра по умолчанию, который создает Filter Designer. Если вы не должны менять фильтр, и Design Filter серый, вы сделаны и можете пропустить, чтобы Квантовать конечную импульсную характеристику фильтр.

Нажмите Design Filter. Filter Designer создает фильтр для заданного проекта. Следующее сообщение появляется в строке состояния Filter Designer после выполнения задачи.

Designing Filter... Done

Для получения дополнительной информации о разработке фильтров с помощью Filter Designer, смотрите документацию DSP System Toolbox™.

Необходимо квантовать фильтры для генерации HDL-кода. Чтобы квантовать ваш фильтр,

Откройте конечную импульсную характеристику, создание фильтра вы создали в Design фильтр конечной импульсной характеристики в Filter Designer, если он еще не открыт.

Нажмите кнопку «Задать параметры квантования![]() » на левой панели инструментов. Filter Designer отображает меню Filter arithmetic в нижней половине своего диалогового окна.

» на левой панели инструментов. Filter Designer отображает меню Filter arithmetic в нижней половине своего диалогового окна.

Выберите Fixed-point из списка. Затем выберите Specify all из списка Filter precision. Filter Designer отображает первую из трех панелей с вкладками параметров квантования в нижней половине своего диалогового окна.

Используйте опции квантования, чтобы проверить эффекты различных настроек на эффективность и точность квантованного фильтра.

Установите параметры квантования следующим образом:

| Вкладка | Параметр | Настройка |

|---|---|---|

| Coefficients | Numerator word length | 16 |

| Best-precision fraction lengths | Selected | |

| Use unsigned representation | Cleared | |

| Scale the numerator coefficients to fully utilize the entire dynamic range | Cleared | |

| Input/Output | Input word length | 16 |

| Input fraction length | 15 | |

| Output word length | 16 | |

| Filter Internals | Rounding mode | Floor |

| Overflow mode | Saturate | |

| Accum. word length | 40 |

Нажмите Apply.

Для получения дополнительной информации о фильтрах квантования с помощью Filter Designer см. документацию DSP System Toolbox.

После квантования фильтра вы готовы сконфигурировать опции кодера и сгенерировать код Verilog для фильтра. В этом разделе приведены руководства по запуску пользовательского интерфейса, установке опций и генерации кода Verilog и испытательного стенда для конечной импульсной характеристики фильтра, который вы разработали и квантовали, в Проект конечной импульсной характеристики Filter in Filter Designer и Quantize the конечной импульсной характеристики Filter.

Запустите Filter Design HDL Coder™ пользовательский интерфейс, выбрав Targets > Generate HDL в диалоговом окне Filter Designer. В Filter Designer появится диалоговое окно «Генерация HDL».

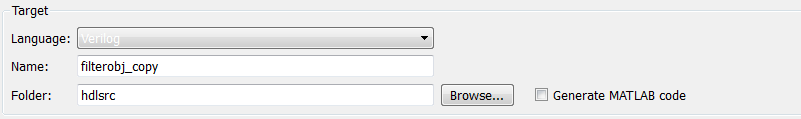

Выберите Verilog для опции Language, как показано на следующем рисунке.

В Name текстовом поле панели Target замените имя по умолчанию на optfir. Эта опция называет модуль Verilog и файл, который содержит код Verilog для фильтра.

На панели Filter architecture выберите опцию Optimize for HDL. Эта опция предназначена для генерации HDL-кода, оптимизированного для эффективности или пространству. Когда эта опция включена, кодер делает компромиссы относительно типов данных и может игнорировать ваши настройки квантования, чтобы достичь оптимизации. Когда вы используете опцию, имейте в виду, что вы делаете это за счет потенциальных числовых различий между результатами фильтра, полученными исходным объектом фильтра, и моделируемыми результатами для оптимизированного HDL-кода.

Выберите CSD для опции Coefficient multipliers. Эта опция оптимизирует операции коэффициентного умножения путем инструкции кодеру заменить их сложениями частичных продуктов, произведенных методом канонической цифры со знаком (CSD). Этот метод минимизирует количество операций сложения, необходимых для постоянного умножения, путем представления двоичных чисел с минимальным количеством ненулевых цифр.

Выберите опцию Add pipeline registers. Для конечная импульсная характеристика эта опция оптимизирует окончательное суммирование. Кодер создает конечный сумматор, который выполняет попарное сложение последовательных продуктов и включает в себя стадию регистров конвейера после каждого уровня дерева. При использовании для конечная импульсная характеристика эта опция может привести к числовым различиям между результатами, произведенными исходным объектом фильтра, и моделируемыми результатами для оптимизированного HDL-кода.

Теперь отобразится диалоговое окно Генерация HDL (Generate HDL), как показано на рисунке.

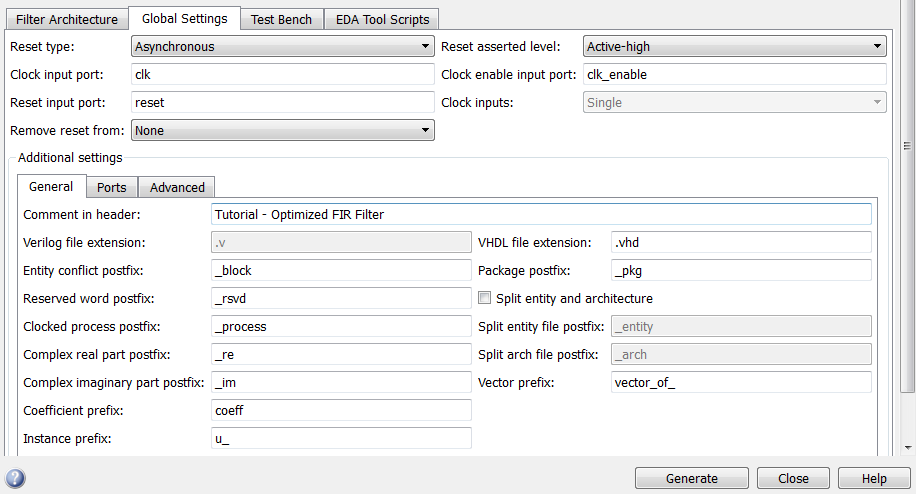

Выберите вкладку Global settings пользовательского интерфейса. Затем выберите вкладку General раздела Additional settings.

В Comment in header текстовом поле введите Tutorial - Optimized FIR Filter. Кодер добавляет комментарий в конец блока комментариев заголовка в каждом сгенерированном файле.

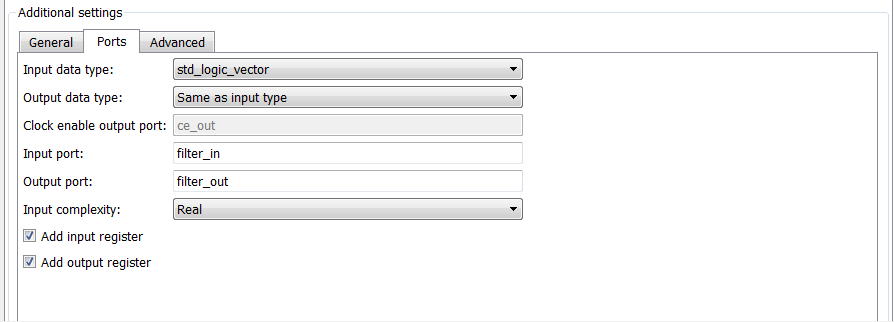

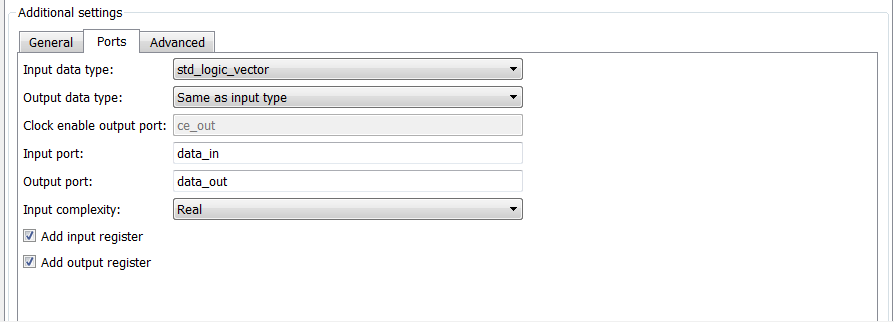

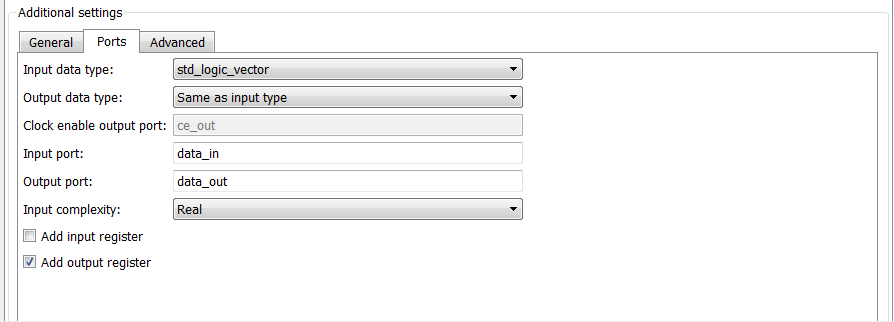

Выберите вкладку Ports раздела Additional settings пользовательского интерфейса.

Измените имена входного и выходного портов. В Input port текстовом поле замените filter_in с data_in. В Output port текстовом поле замените filter_out с data_out.

Снимите флажок для опции Add input register. Панель Ports теперь выглядит следующим образом.

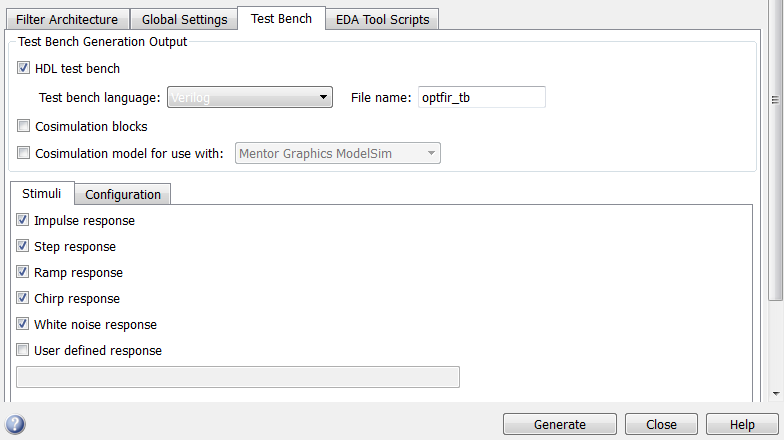

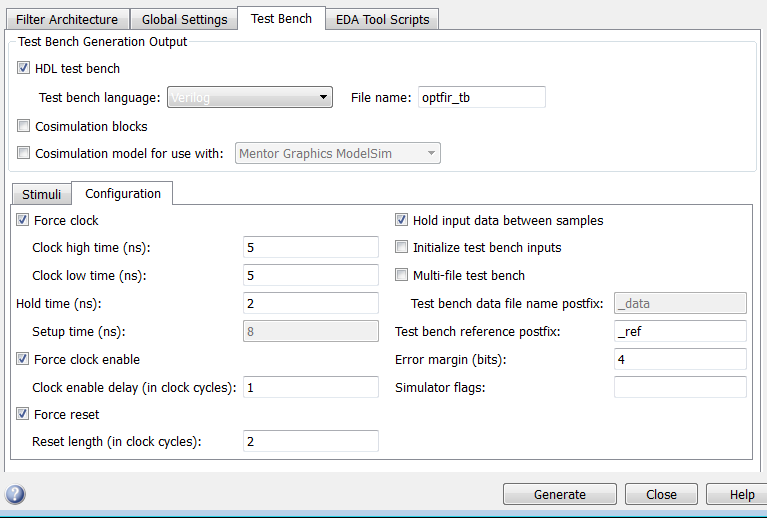

Перейдите на вкладку Test Bench в диалоговом окне Генерация HDL. В File name текстовом поле замените имя по умолчанию на optfir_tb. Эта опция называет сгенерированный испытательный стенд.

На панели Испытательный стенд перейдите на вкладку Configuration . Обратите внимание, что опция Error margin (bits) включена. Эта опция включена, потому что ранее выбранные опции оптимизации (такие как Add pipeline registers) могут потенциально привести к числовым результатам, которые отличаются от результатов, полученных исходным объектом фильтра. Можно использовать эту опцию, чтобы настроить количество наименее значимых битов, которые испытательный стенд игнорирует во время сравнений, прежде чем генерировать предупреждение.

В диалоговом окне «Генерация HDL» нажмите кнопку Generate, чтобы начать процесс генерации кода. Когда генерация кода завершится, нажмите Close, чтобы закрыть диалоговое окно.

Кодер отображает следующие сообщения в Командном Окне MATLAB, когда он генерирует файлы фильтра и испытательного стенда Verilog:

### Starting Verilog code generation process for filter: optfir ### Generating: C:\hdlfilter_tutorials\hdlsrc\optfir.v ### Starting generation of optfir Verilog module ### Starting generation of optfir Verilog module body ### HDL latency is 8 samples ### Successful completion of Verilog code generation process for filter: optfir ### Starting generation of VERILOG Test Bench ### Generating input stimulus ### Done generating input stimulus; length 3429 samples. ### Generating Test bench: C:\hdlfilter_tutorials\hdlsrc\optfir_tb.v ### Please wait ... ### Done generating VERILOG Test Bench

Как указывают сообщения, кодер создает папку hdlsrc в текущей рабочей папке и помещает файлы optfir.v и optfir_tb.v в этой папке.

Обратите внимание, что сообщения включают гиперссылки на сгенерированный код и файлы испытательного стенда. Нажимая на эти гиперссылки, можно открыть файлы кода непосредственно в РЕДАКТОРА MATLAB.

Сгенерированный код Verilog имеет следующие характеристики:

Модуль Verilog с именем optfir.

Регистры, которые используют асинхронные сбросы, когда сигнал сброса активен высокий (1).

Сгенерированный код, который оптимизирует использование им типов данных и устраняет избыточные операции.

Коэффициентные умножители, оптимизированные с помощью CSD метода.

Окончательные суммирования оптимизированы с использованием конвейерного метода.

Порты со следующими именами:

| Порт Верилога | Имя |

|---|---|

| Вход | data_in |

| Выход | data_out |

| Вход синхроимпульса | clk |

| Вход включения синхроимпульса | clk_enable |

| Сбросьте вход | reset |

Дополнительный регистр для обработки вывода фильтра.

Коэффициенты с именем coeff , где nn - число коэффициентов, начиная с 1.

Представление type-safe используется, когда нули объединены: '0' & '0'...

Постфикс- '_process' добавляется к последовательному (begin) имена блоков.

Сгенерированный испытательный стенд:

Является портативным файлом Verilog.

Заставляет синхроимпульсы, активировать синхроимпульсы и сбрасывать входные сигналы.

Приводит входной сигнал включения синхроимпульса к активному высокому значению.

Управляет входным сигналом синхроимпульса высокий (1) в течение 5 наносекунд и низкий (0) в течение 5 наносекунд.

Формирует сигнал сброса для двух циклов плюс время удержания 2 наносекунды.

Применяет время удержания 2 наносекунды к входным сигналам данных.

Применяет запас по ошибке 4 бита.

Для конечная импульсная характеристика применяются типы импульса, шага, пандуса, щебета и белого шума.

Познакомьтесь с оптимизированным сгенерированным кодом Verilog, открывая и просматривая файл optfir.v в редакторе ASCII или Симулятора HDL:

Откройте сгенерированный файл фильтра Verilog optcfir.v.

Поиск optfir. Эта линия определяет модуль Verilog, используя значение, заданное для опции Name на панели Target. См. шаг 3 в разделе «Настройка и генерация оптимизированного кода Verilog».

Поиск Tutorial. В этом разделе кода кодер помещает текст, введенный для опции Comment in header. См. шаг 9 в разделе «Настройка и генерация оптимизированного кода Verilog».

Поиск HDL Code. В этом разделе перечислены опции кодера, измененные в Настройте и Сгенерируйте оптимизированный код Verilog.

Поиск Filter Settings. В этом разделе кода VHDL описывается создание фильтра и параметры квантования, заданные в разделе Проектирование конечной импульсной характеристике в Filter Designer и Квантование конечной импульсной характеристики.

Поиск module. Эта линия называет модуль Verilog, используя значение, заданное для опции Name на панели Target. Эта линия также объявляет список портов, заданный опциями на панели Ports диалогового окна Генерация HDL. Порты для входа и выхода данных называются значениями, заданными для опций Input port и Output port на вкладке Ports диалогового окна Генерация HDL. См. шаги 3 и 11 в разделе Настройка и генерация оптимизированного кода Verilog.

Поиск input. Эта линия и следующие четыре линии объявляют режим направления каждого порта.

Поиск Constants. Этот код определяет коэффициенты. Они названы с помощью схемы именования по умолчанию coeff , где nn - число коэффициентов, начиная с 1.

Поиск Signals. Этот код определяет сигналы фильтра.

Поиск sumvector1. Эта область кода объявляет сигналы для реализации образца конвейерного последнего сумматора. Также включены объявления сигналов для четырех дополнительных конвейерных конечных сумматоров. Эти сигналы используются для реализации оптимизации стиля конвейерной конечной импульсной характеристики сумматора, заданной опцией Add pipeline registers. См. шаг 7 в разделе Настройка и генерация оптимизированного кода Verilog.

Поиск process. The block имя Delay_Pipeline_process включает в себя block по умолчанию постфикс- '_process'.

Поиск reset. Этот код утверждает сигнал сброса. Задано значение по умолчанию, активный высокий (1). Также обратите внимание, что process применяет стиль асинхронного сброса по умолчанию при генерации кода для регистров.

Поиск posedge. Этот код Verilog проверяет увеличение ребер, когда фильтр работает с регистрами.

Поиск sumdelay_pipeline_process1. Этот блок реализует стадию регистра трубопровода стиля конечной импульсной характеристики сумматора, указанный вами на шаге 7 в Configure and Generate Optimized Verilog Кода.

Поиск output_register. Этот код записывает выход фильтра в регистр выхода. Код для этого регистра генерируется по умолчанию. На шаге 12 в Настройте и Сгенерируйте оптимизированный код Verilog, вы очистили опцию Add input register, но оставили выбранное Add output register. Также обратите внимание, что имя процесса Output_Register_process включает в себя process по умолчанию постфикс- '_process'.

Поиск data_out. Этот код управляет выходом данными фильтра.

В этом разделе описывается, как проверить оптимизированный сгенерированный код Verilog для конечной импульсной характеристики фильтра с сгенерированным испытательным стендом Verilog. В этом руководстве используется Mentor Graphics® ModelSim® симулятор как инструмент для компиляции и симуляции кода Verilog. Можно использовать другие пакеты инструментов симуляции HDL.

Чтобы проверить код фильтра, выполните следующие шаги:

Запустите симулятор. Когда вы запускаете симулятор Mentor Graphics ModelSim, появляется экран, подобный следующему.

Установите текущую папку в папку, содержащую ваши сгенерированные файлы Verilog. Для примера:

cd hdlsrc

При необходимости создайте библиотеку проекта для хранения скомпилированных модулей Verilog. В симуляторе Mentor Graphics ModelSim можно создать библиотеку проекта с vlib команда.

vlib work

Скомпилируйте сгенерированный фильтр и испытательный стенд файлы Verilog. В симуляторе Mentor Graphics ModelSim вы компилируете код Verilog с vlog команда. Следующие команды компилируют фильтр и фильтр испытательного стенда кодом Verilog.

vlog optfir.v vlog optfir_tb.v

На следующем отображении экрана показана эта командная последовательность и информационные сообщения, отображаемые во время компиляции.

Загрузите испытательный стенд для симуляции. Процедура загрузки испытательного стенда варьируется в зависимости от используемого симулятора. В симуляторе Mentor Graphics ModelSim загрузите испытательный стенд для симуляции с vsim команда. Для примера:

vsim optfir_tb

На следующем отображении показаны результаты загрузки optfir_tb с vsim команда.

Откройте окно отображения для мониторинга симуляции при запуске испытательного стенда. В симуляторе Mentor Graphics ModelSim можно использовать следующую команду, чтобы открыть wave окно и просмотреть результаты симуляции как HDL-формы сигналов.

add wave *

Откроется следующее wave окно:

Чтобы начать запускать симуляцию, выполните команду start simulation для своего симулятора. Например, в симуляторе Mentor Graphics ModelSim можно начать симуляцию с run команда.

Следующее отображение показывает run -all команда используется для запуска симуляции.

Когда ваш испытательный стенд запускается, следите за сообщениями об ошибке. Если появляются сообщения об ошибках, интерпретируйте их так, как они относятся к созданию фильтра и выбранным опциям генерации HDL-кода. Определите, ожидаются ли результаты на основе индивидуальных настроек, заданных при генерации кода Verilog фильтра.

В следующем wave окне показаны результаты симуляции как HDL-формы волны.