Кодер предоставляет опции, которые расширяют ваш контроль над скоростью по сравнению с площадью компромиссов в реализации созданий фильтра. Для достижения желаемого компромисса можно либо задать полностью параллельную архитектуру для сгенерированных кодов HDL-фильтра, либо выбрать одну из нескольких последовательных архитектур. Эти архитектуры описаны в параллельных и последовательных архитектурах.

В следующей таблице приведены типы фильтров, доступные для параллельных и последовательных вариантов архитектуры.

| Архитектура | Доступно для типов фильтров... |

|---|---|

Fully parallel (по умолчанию) | Типы фильтров, поддерживаемые для генерации HDL-кода |

Fully serial |

|

Partly serial |

|

Cascade serial |

|

Кодер поддерживает полную область значений параллельной и последовательной архитектуры опций через свойства, переданные в generatehdl функция, как описано в разделе «Определение скорости по сравнению с площадью компромиссов при помощи generatehdl Properties».

Кроме того, можно использовать всплывающее меню Architecture в диалоговом окне Generate HDL, чтобы выбрать опции параллельной и последовательной архитектуры, как описано в разделе «Выбор архитектуры» Диалогового окна генерации HDL.

Примечание

Кодер также поддерживает распределенную арифметику (DA), другую высокоэффективную архитектуру для реализации фильтров. Смотрите Распределенную арифметику для конечной импульсной характеристики фильтров.

Эта опция является выбором по умолчанию. A fully parallel architecture использует выделенный множитель и сумматор для каждого отвода фильтра; ответвления выполняются параллельно. Этот тип архитектуры оптимален для скорости. Однако он требует больше умножителей и сумматоров, чем последовательная архитектура, и поэтому потребляет больше площади чипа.

Serial architectures повторно используете аппаратные ресурсы во времени, сохраняя область микросхем. Кодер обеспечивает область значений опций последовательной архитектуры. Эти архитектуры имеют задержку в один тактовый период (см. Задержка в последовательной архитектуре).

Можно выбрать из следующих опций последовательной архитектуры:

Fully serial: Полностью последовательная архитектура сохраняет область путем повторного использования ресурсов умножения и суммирования последовательно. Для примера в создание фильтра с четырьмя отводами используется один умножитель и сумматор, выполняющий операцию умножения/накопления один раз для каждого отвода. Раздел умножения/накопления проекта запускается с четырехкратной частотой выборки вход/выход. Этот тип архитектуры экономит площадь за счет некоторых потерь скорости и более высокого потребления степени.

В полностью последовательной архитектуре системных часов запусков с гораздо большей частотой, чем частота дискретизации фильтра. Таким образом, для заданного создания фильтра максимальная скорость, достижимая полностью последовательной архитектурой, меньше, чем максимальная скорость параллельной архитектуры.

Partly serial: Частично последовательная архитектура охватывает всюсь область значений компромиссов скорости и площади, которые находятся между полностью параллельной и полностью последовательной архитектурами.

В частичной последовательной архитектуре ответвления фильтра сгруппированы в последовательные разделы. Ответвления внутри каждого раздела выполняются последовательно, но разделы выполняются вместе параллельно. Выходные выходы секций суммируются на конечном выходе.

При выборе частично последовательной архитектуры для фильтра можно задать последовательное разделение следующими способами:

Задайте последовательные разбиения непосредственно, как вектор целых чисел. Каждый элемент вектора задает длину соответствующего раздела.

Задайте желаемый аппаратный коэффициент складывания ff, целое число, больше 1. Учитывая коэффициент складывания, кодер вычисляет последовательный раздел и количество умножителей.

Задайте желаемое количество умножителей nmults, целое число, больше 1. Учитывая количество умножителей, кодер вычисляет последовательный раздел и коэффициент складывания.

Диалоговое окно Генерация HDL позволяет вам задать частично последовательную архитектуру с точки зрения этих трех параметров. Затем можно просмотреть, как изменение одного параметра взаимодействует с двумя другими. Кодер также обеспечивает hdlfilterserialinfo, информационная функция, которая помогает вам задать оптимальный последовательный раздел для фильтра.

Cascade-serial: Каскадно-серийная архитектура тесно напоминает частично последовательную архитектуру. Как и в частично последовательной архитектуре, ответвления фильтра сгруппированы в несколько последовательных разделов, которые выполняются вместе параллельно. Однако накопленный выход каждой перегородки каскадируется к аккумулятору предыдущей перегородки. Поэтому выходы перегородок вычисляются в аккумуляторе первой перегородки. Этот метод называется повторным использованием аккумулятора. Вам не требуется конечный сумматор, который сохраняет область.

Для каскадно-последовательной архитектуры требуется дополнительный цикл системных часов, чтобы завершить окончательное суммирование к выходу. Поэтому частота системных часов должна быть несколько увеличена по сравнению с тактовой частотой, используемой в некаскадной частично последовательной архитектуре.

Чтобы сгенерировать каскадно-последовательную архитектуру, вы задаете частично последовательную архитектуру с включенным повторным использованием аккумулятора. Если вы не задаете последовательные разделы, кодер автоматически выбирает оптимальное разбиение.

Сериализация фильтра увеличивает общую задержку проекта на один такт. Последовательные архитектуры используют аккумулятор (сумматор с регистром), чтобы добавить последовательные продукты. Дополнительный конечный регистр используется для хранения суммированного результата каждого из последовательных разделов. Операция требует дополнительного тактового цикла.

В последовательной архитектуре реализована внутренняя тактовая частота, превышающая частоту входа. В таких реализациях фильтра существуют N циклы (N >= 2) базового синхроимпульса для каждой входной выборки. Можно задать, сколько тактовых циклов испытательный стенд содержит значения входных данных в допустимом состоянии.

При выборе Hold input data between samples (по умолчанию) испытательный стенд содержит значения входных данных в допустимом состоянии для N тактовые импульсы.

Когда вы снимаете Hold input data between samples, испытательный стенд содержит значения в допустимом состоянии только для одного такта. Для следующего N-1 циклы, испытательный стенд приводит данные в неизвестное состояние (выраженное как 'X') пока следующая входная выборка не будет синхронизирована. Принудительное преобразование входных данных в неизвестное состояние проверяет, что сгенерированный код фильтра регистрирует входные данные только в первом цикле.

Рисунок показывает панель Test Bench диалогового окна Генерация HDL с Hold input data between samples установкой по умолчанию.

Используйте эквивалентную HoldInputDataBetweenSamples свойство при вызове generatehdl функция.

generatehdl СвойстваПо умолчанию, generatehdl генерирует код фильтра с помощью полностью параллельной архитектуры. Если вы хотите сгенерировать код фильтра с полностью параллельной архитектурой, вы не должны указывать эту архитектуру явно.

Два свойства задают опции последовательной архитектуры для generatehdl функция:

SerialPartition: Это свойство задает последовательное разбиение фильтра на разделы.

ReuseAccum: Это свойство включает или отключает повторное использование аккумулятора.

Таблица результирует, как задать эти свойства, чтобы сгенерировать необходимую архитектуру.

| Чтобы сгенерировать это Архитектура... | Установите значение SerialPartition на... | Установите значение ReuseAccum на... |

|---|---|---|

| Полностью параллельный | Опустить это свойство | Опустить это свойство |

| Полностью последовательный | N, где N - длина фильтра | Не задан, или 'off' |

| Частично последовательный |

Можно также задать последовательную архитектуру с точки зрения желаемого аппаратного коэффициента складывания, или с точки зрения оптимального количества умножителей. Посмотрите | 'off' |

| Каскадно-последовательный с явно заданным разбиением | [p1 p2 p3...pN]: вектор из целых чисел, имеющих N элементы, где N количество последовательных разделов. Каждый элемент вектора задает длину соответствующего раздела. Сумма векторных элементов должна равняться длине фильтра. Значения векторных элементов должны находиться в порядке убывания, за исключением того, что последние два элемента должны быть равными. Например, для фильтра длины 9, такие разделы, как [5 4] или [4 3 2] было бы законно, но разделы [3 3 3] или [3 2 4] вызвать ошибку во время генерации кода. | 'on' |

| Каскадно-последовательный с автоматически оптимизированным разбиением | Опустить это свойство | 'on' |

Вы можете использовать функцию helper hdlfilterserialinfo чтобы исследовать возможные разделы для вашего фильтра.

Для получения примера смотрите Сгенерировать последовательные разделы для конечной импульсной характеристики фильтра.

Чтобы задать частично или полностью последовательную архитектуру для структуры фильтра IIR SOS (df1sos или dsp.BiquadFilter), задайте один из следующих параметров:

'FoldingFactor',ff: Укажите требуемый коэффициент складывания оборудования ff, целое число, больше 1. Учитывая коэффициент складывания, кодер вычисляет количество умножителей.

'NumMultipliers',nmults: Укажите желаемое количество умножителей nmults, целое число, больше 1. Учитывая количество умножителей, кодер вычисляет коэффициент складывания.

Чтобы получить информацию об опциях коэффициента складывания и соответствующем количестве умножителей для фильтра, вызовите hdlfilterserialinfo функция.

Для получения примера см. раздел «Генерация последовательной архитектуры для БИХ фильтра».

Всплывающее меню Architecture, в диалоговом окне Generate HDL, позволяет выбрать параллельную и последовательную архитектуру. В следующих разделах описываются опции пользовательского интерфейса, которые необходимо задать для каждого варианта Architecture.

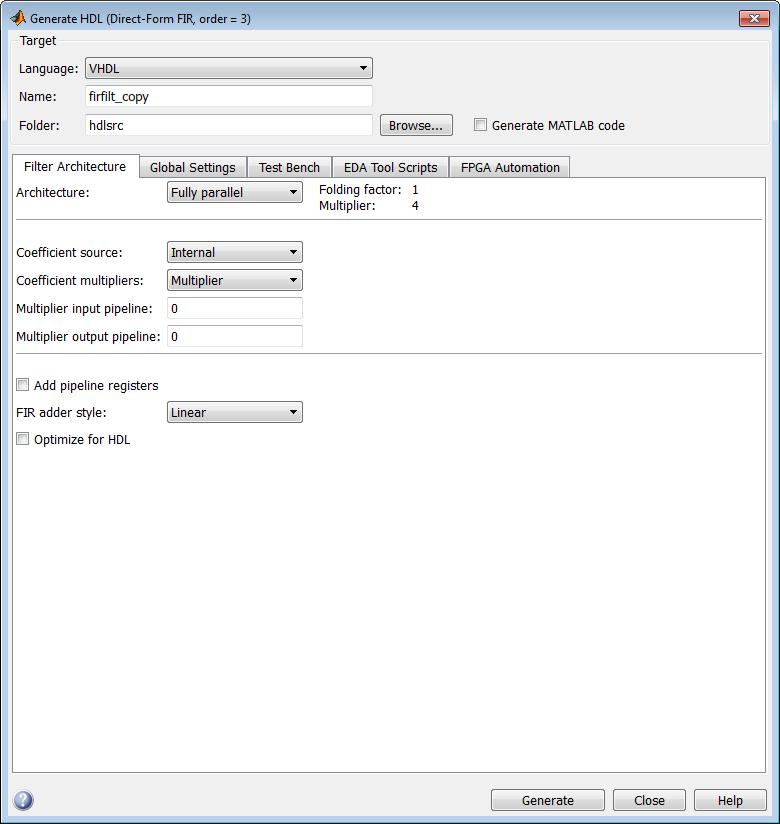

Настройкой Architecture по умолчанию является Fully parallel, как показано.

Когда вы выбираете Fully serialArchitecture опции диалоговое окно Генерация HDL отображает дополнительную информацию о коэффициенте складывания, количестве умножителей и последовательном разбиении. Поскольку эти параметры зависят от длины фильтра, они отображаются в формате, доступном только для чтения, как показано на следующем рисунке.

Диалоговое окно Генерация HDL также отображает View details ссылку. При нажатии этой ссылки кодер отображает HTML в отдельном окне. Отчет отображает исчерпывающую таблицу настроек коэффициента складывания, множителя и последовательного раздела для текущего фильтра. Вы можете использовать таблицу, чтобы помочь вам выбрать оптимальные настройки для вашего проекта.

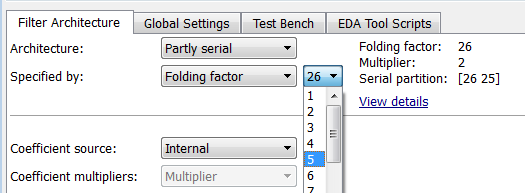

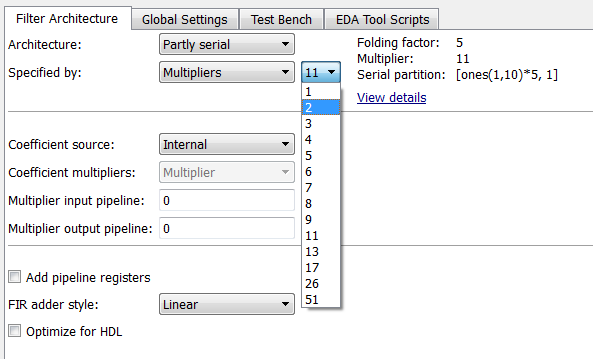

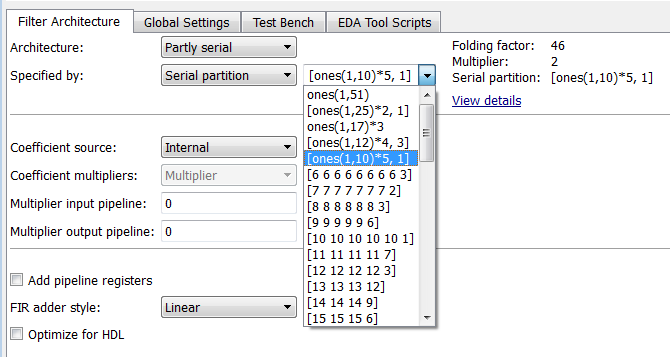

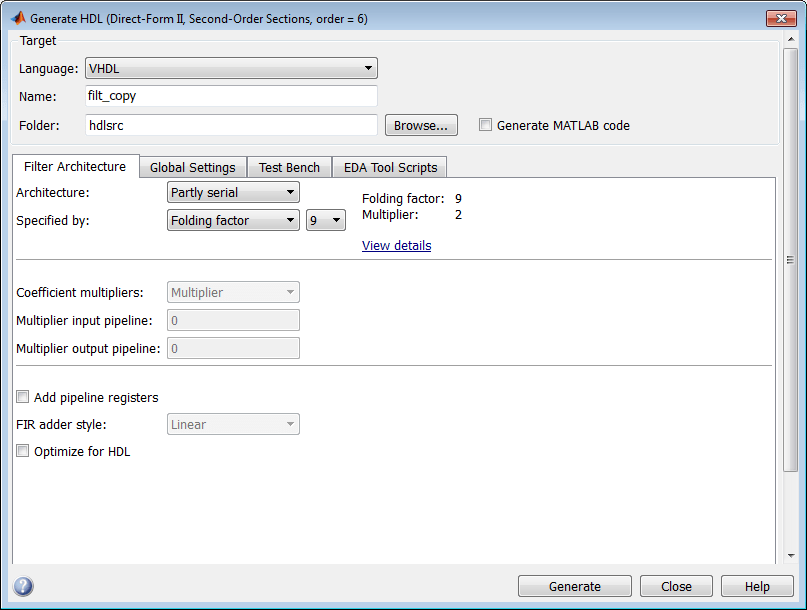

Когда вы выбираете Partly serial

Architecture опция, диалоговое окно Генерация HDL отображает дополнительную информацию и поля ввода данных, связанные с последовательным разбиением. (См. следующий рисунок.)

Диалоговое окно Генерация HDL также отображает View details ссылку. При нажатии этой ссылки кодер отображает HTML в отдельном окне. Отчет отображает исчерпывающую таблицу настроек коэффициента складывания, множителя и последовательного раздела для текущего фильтра. Вы можете использовать таблицу, чтобы помочь вам выбрать оптимальные настройки для вашего проекта.

Раскрывающееся меню Specified by позволяет вам решить, как вы определяете частично последовательную архитектуру. Выберите один из следующих опций:

Folding factor: Раскрывающееся меню справа от Folding factor содержит исчерпывающий список коэффициентов складывания для фильтра. При выборе значения обновляется отображение текущего коэффициента складывания, умножителя и настроек последовательного раздела.

Multipliers: Раскрывающееся меню справа от Multipliers содержит исчерпывающий список опций значения для количества умножителей для фильтра. При выборе значения обновляется отображение текущего коэффициента складывания, умножителя и настроек последовательного раздела.

Serial partition: Раскрывающееся меню справа от Serial partition содержит исчерпывающий список последовательных опций разделов для фильтра. При выборе значения обновляется отображение текущего коэффициента складывания, умножителя и настроек последовательного раздела.

Когда вы выбираете Cascade serial

Architecture опции диалоговое окно Генерация HDL отображает поле Serial partition, как показано на следующем рисунке.

Меню Specified by позволяет вам задать количество и размер последовательных разделов в соответствии с различными критериями, как описано в разделе «Определение скорости и компромиссов по площади через generatehdl Properties».

Чтобы задать частично или полностью последовательную архитектуру для структуры фильтра IIR SOS в пользовательском интерфейсе, установите следующие опции:

Architecture: Выбор Fully parallel (по умолчанию), Fully serial, или Partly serial. Если вы выбираете Partly serialВ пользовательском интерфейсе отображается раскрывающееся меню Specified by.

Specified by: Выберите один из следующих вариантов:

Folding factor: Задайте желаемый коэффициент оборудования складывания, ff, целое число, больше 1. Учитывая коэффициент складывания, кодер вычисляет количество умножителей.

Multipliers: Укажите желаемое количество умножителей, nmults, целое число, больше 1. Учитывая количество умножителей, кодер вычисляет коэффициент складывания.

Пример: Фильтр SOS прямой формы I. В следующем примере создается прямая форма I SOS (df1sos) фильтровать дизайн и открывает пользовательский интерфейс. Рисунок, следующий за примером кода, показывает опции кодера, настроенные для частично последовательной архитектуры, заданной в Folding factor из 18.

Fs = 48e3 % Sampling frequency Fc = 10.8e3 % Cut-off frequency N = 5 % Filter Order f_lp = fdesign.lowpass('n,f3db',N,Fc,Fs) filt = design(f_lp,'butter','FilterStructure','df1sos','SystemObject',true) fdhdltool(filt,numerictype(1,16,15))

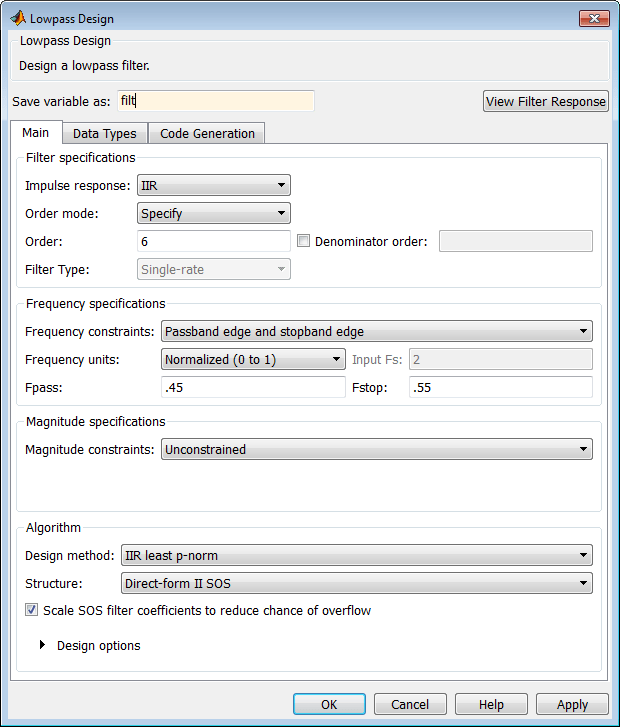

Пример: Фильтр SOS прямой формы II. В следующем примере создается прямая форма II SOS (df2sos) создание фильтра с помощью Filter Builder.

Фильтр является lowpass df2sos фильтр с порядком фильтра 6. Арифметика фильтра установлена в Fixed-point.

На вкладке Code Generation кнопка Generate HDL активирует Filter Design HDL Coder™ UI. Следующий рисунок показывает опции HDL-кодера, настроенные для этого фильтра, используя частично последовательную архитектуру с Folding factor из 9.

Всплывающее меню Architecture также включает в себя Distributed arithmetic (DA) опция. Информацию об этой архитектуре см. в разделе Распределенная арифметика для конечной импульсной характеристики Filters).

Выбор некоторых опций меню Architecture может изменить или отключить другие опции.

Когда Fully serial опция выбрана, следующие опции установлены на их значения по умолчанию и отключены:

Coefficient multipliers

Add pipeline registers

FIR adder style

Когда Partly serial выбрана опция:

Опция Coefficient multipliers имеет значение по умолчанию и отключена.

Если фильтр многоразовый, опция Clock inputs устанавливается на Single и отключен.

Когда Cascade serial опция выбрана, следующие опции установлены на их значения по умолчанию и отключены:

Coefficient multipliers

Add pipeline registers

FIR adder style