Подсистема, выполнение которой разрешено внешним входом

Simulink/Порты и подсистемы

HDL-кодер/порты и подсистемы

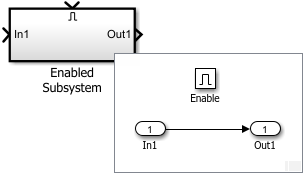

Блок Enabled Subsystem является Subsystem блоком, предварительно сконфигурированным как начальная точка для создания подсистемы, которая выполняется, когда сигнал управления имеет положительное значение.

Используйте Enabled Subsystem блоки для моделирования:

Неоднородности

Дополнительные функциональные возможности

Альтернативная функциональность

In - Вход сигнала в блок SubsystemВходной вход Subsystem блока, заданный как скаляр, вектор или матрица. Размещение блока Inport в блоке Subsystem добавляет к блоку внешний входной порт. Метка порта совпадает с именем блока Inport.

Используйте Inport блоки для приема сигналов от локального окружения.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Enable - Вход сигнала управления в блок SubsystemБлок Enable в блоке Subsystem добавляет внешний входной порт в блок и делает блок Enabled Subsystem блоком.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Out - Сигнал, выводимый из блока SubsystemСигнал, выводимый из блока Subsystem, возвращается в виде скаляра, вектора или матрицы. Размещение блока Outport в блоке Subsystem добавляет к блоку внешний выходной порт. Метка порта совпадает с именем блока Outport.

Используйте Outport блоки для отправки сигналов в локальное окружение.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Типы данных |

|

Прямое сквозное соединение |

|

Многомерные сигналы |

|

Сигналы переменного размера |

|

Обнаружение пересечения нулем |

|

[a] Фактический тип данных или поддержка возможностей зависит от реализации блоков. | |

Фактическая поддержка генерации кода зависит от реализации блока.

HDL Coder™ предоставляет дополнительные опции строения, которые влияют на реализацию HDL и синтезированную логику.

При использовании включенных подсистем в моделях, предназначенных для генерации HDL-кода, рекомендуется учитывать следующее:

Для результатов синтеза, чтобы соответствовать Simulink® результаты порт Enable должен управляться зарегистрированной логикой (с синхронным синхроимпульсом) на FPGA.

Поместите задержки модуля на выходные сигналы Enabled Subsystem. Это препятствует вставке генератором кода дополнительных регистров обхода в HDL-код.

Активированные подсистемы могут влиять на результаты синтеза следующими способами:

В некоторых случаях скорость системных часов может снизиться на небольшой процент.

Сгенерированный код использует больше ресурсов, масштабируя с количеством включенных подсистем образцами и количеством выхода портов на подсистему.

| Архитектура | Описание |

|---|---|

Module (по умолчанию) | Сгенерируйте код для подсистемы и блоков в подсистеме. |

BlackBox | Сгенерируйте интерфейс черного ящика. Сгенерированный HDL-код включает только определения входного/выходного порта для подсистемы. Поэтому можно использовать подсистему в модели, чтобы сгенерировать интерфейс к существующему, вручную написанному HDL-коду. Генерация интерфейса черного ящика для подсистем подобна генерации интерфейса блока Model без синхроимпульсов. |

| Удалите подсистему из сгенерированного кода. Можно использовать подсистему в симуляции, однако относиться к ней как к «no-op» в HDL-коде. |

| Общая информация | |

|---|---|

| AdaptivePipelining | Автоматическая вставка конвейера на основе инструмента синтеза, целевой частоты и длин размеров слова умножителей. Значение по умолчанию является |

| BalanceDelays | Обнаруживает введение новых задержек вдоль одного пути и вставляет соответствующие задержки на другие пути. Значение по умолчанию является |

| ClockRatePipelining | Вставьте регистры конвейера с более высокой тактовой частотой вместо более медленной скорости передачи данных. Значение по умолчанию является |

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| DistributedPipelining | Распределение регистров трубопроводов или синхронизация регистров. Значение по умолчанию является |

| DSPStyle | Атрибуты синтеза для отображения множителей. Значение по умолчанию является |

| FlattenHierarchy | Удалите иерархию подсистем из сгенерированного HDL-кода. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| SharingFactor | Количество функционально эквивалентных ресурсов для сопоставления с одним общим ресурсом. Значение по умолчанию 0. См. также раздел «Совместное использование ресурсов» (HDL Coder). |

| StreamingFactor | Количество параллельных путей данных, или векторов, которые мультиплексированы во времени для преобразования в последовательные, скалярные пути данных. Значение по умолчанию 0, которое реализует полностью параллельные пути данных. См. также раздел Потоковая передача (HDL Coder). |

Целевые спецификации

Этот блок не может быть DUT, поэтому настройки свойств блоков на вкладке Target Specification игнорируются.

HDL Coder поддерживает генерацию HDL-кода для подсистем с поддержкой, которые отвечают следующим условиям:

Включенная подсистема не является DUT.

Подсистема не инициируется и не активируется.

Разрешающий сигнал является скаляром.

Выходы включенной подсистемы имеют начальное значение 0.

Все входы и выходы включенной подсистемы (включая сигнал включения) выполняются с одной скоростью.

Параметр Show output port блока Enable установлен в Off.

Параметр States when enabling блока Enable установлен в held (т.е. блок Enable не сбрасывает состояния при включении).

Параметр Output when disabled для выходных портов включенной подсистемы установлен в held (т.е. включенная подсистема не сбрасывает выходные значения при отключении).

Если DUT содержит следующие блоки, RAMArchitecture установлено в WithClockEnable:

Dual Port RAM

Simple Dual Port RAM

Single Port RAM

Включенная подсистема не содержит следующих блоков:

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL FIFO

HDL Cosimulation блоки (HDL- Verifier™)

Переход скорости

NR Polar Encoder и NR Polar Decoder (Wireless HDL Toolbox™)

В примере Automatic Gain Controller показано, как можно использовать включенные подсистемы при генерации HDL-кода. Чтобы открыть пример, введите:

hdlcoder_agc

Фактическая поддержка типа данных зависит от реализации блоков.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.