Первая фаза симуляции происходит, когда модель системы открыта, и вы симулируете модель. В Simulink® Редактор, нажмите Run. Выполнение симуляции заставляет механизм Simulink вызвать компилятор модели. Компилятор модели преобразует модель в исполняемую форму, процесс, называемый компиляцией. В частности, компилятор:

Оценивает выражения параметров блоков модели, чтобы определить их значения.

Определяет атрибуты сигнала, например, имя, тип данных, числовой тип и размерность, не заданные явно моделью, и проверяет, что каждый блок может принимать сигналы, соединенные с его входами.

Распространяет атрибуты исходного сигнала на входы блоков, которые он управляет в порядок для вычисления ранее не определенных атрибутов в блоках.

Выполняет оптимизацию сокращения блоков.

Выравнивает иерархию модели путем замены виртуальных подсистем на блоки, которые они содержат (см. «Сравнение решателей»).

Определяет порядок выполнения блока путем основанной на задаче сортировки.

Определяет шаги расчета всех блоков в модели, шагов расчета которых вы явным образом не задали (см. «Как Распространение Влияний Наследование Шагов расчета»).

Эти события по существу совпадают с тем, что происходит при обновлении схемы (Update Diagna и Run Simulation). Различие, что программное обеспечение Simulink начинает компиляцию модели как часть симуляции модели, где компиляция ведет непосредственно к фазе связывания, как описано в Ссылку Phase. Напротив, вы начинаете явное обновление модели как автономная работа на модели.

Когда вы компилируете иерархию модели или модели, можно отменить компиляцию модели, нажав кнопку Cancel рядом со строкой прогресса.

В этой фазе механизм Simulink выделяет память, необходимую для рабочих областей (сигналов, состояний и параметров времени выполнения), для выполнения блока. Он также выделяет и инициализирует память для структур данных, которые хранят информацию во время выполнения для каждого блока. Для встроенных блоков основная структура данных во время выполнения для блока называется SimBlock. Он хранит указатели на входные и выходные буферы блока и векторы состояния и работы.

В фазе Link механизм Simulink также создает списки выполнения метода. Эти списки перечисляют наиболее эффективный порядок, в котором можно вызвать методы блоков модели для вычисления ее выходов. Списки порядка выполнения блока, сгенерированные во время фазы компиляции модели, используются, чтобы создать списки выполнения метода.

Блокам можно присвоить приоритеты обновления. Методы выхода блоков с более высоким приоритетом выполняются перед способами блоков с более низким приоритетом. Эти приоритеты выполняются только в том случае, если они соответствуют порядку выполнения блока.

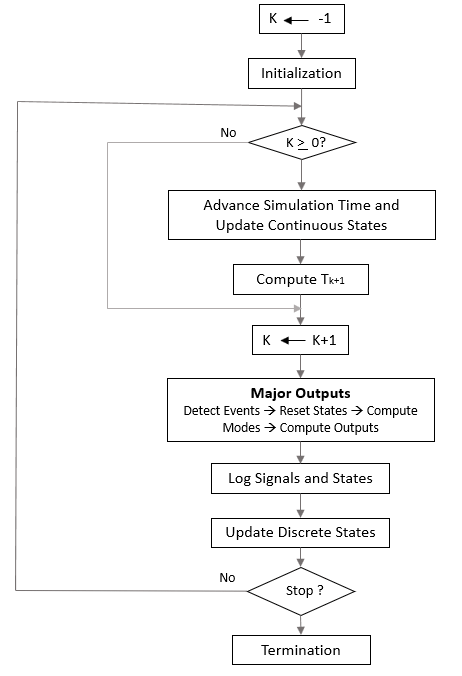

Когда Фаза Ссылки завершается, симуляция входит в фазу цикла симуляции. На этой фазе двигатель Simulink последовательно вычисляет состояния и выходы системы с интервалами от времени начала симуляции до времени конца, используя информацию, предоставленную моделью. Последующие временные точки, в которых вычисляются состояния и выходы, называются временными шагами. Интервал времени между шагами называется размером шага. Размер шага зависит от типа решателя (см. «Сравнение Решателей»), используемого для вычисления непрерывных состояний системы, основного шага расчета системы (см. Шаги расчета в Системах), и от того, имеют ли непрерывные состояния системы разрывы (см. «Обнаружение Пересечения нулем»).

Фаза Цикла Симуляции состоит из двух подфаз: Фаза Инициализации Цикла и Фаза Итерации Цикла. Фаза инициализации происходит один раз, в начале цикла. Фаза итерации повторяется один раз в временной шаг от времени начала симуляции до времени остановки симуляции.

В начале симуляции модель задает начальные состояния и выходы системы, которая будет моделироваться. На каждом шаге вычисляются новые значения для входов, состояний и выходов системы, и модель обновляется, чтобы отразить вычисленные значения. В конце симуляции модель отражает окончательные значения входов, состояний и выходов системы. Программное обеспечение Simulink предоставляет блоки отображения и регистрации данных. Можно отображать и/или регистрировать промежуточные результаты путем включения этих блоков в модель.

Следующая блок-схема объясняет, как работает цикл симуляции где k обозначает основной счетчик шагов:

На каждом временном шаге механизм Simulink:

Вычисляет выходы модели.

Механизм Simulink инициирует этот шаг, вызывая метод Simulink Model Outputs. Метод model Outputs в свою очередь вызывает метод model system Outputs, который вызывает методы Outputs блоков, которые содержатся в модели, в порядке, заданном списками выполнения метода Outputs, сгенерированными в фазе Link симуляции (см. «Сравнение решателей»).

Системный метод Outputs передает следующие аргументы каждому блочному методу Outputs: указатель на структуру данных блока и на его структуру SimBlock. Структуры данных SimBlock указывают на информацию о том, что метод Outputs должен вычислять выходы блока, включая расположение его входных буферов и выходных буферов.

Вычисляет состояния модели.

Механизм Simulink вычисляет состояния модели путем вызова решателя. Какой решатель он вызывает, зависит от того, имеет ли модель состояния, только дискретные состояния, только непрерывные состояния или как непрерывные, так и дискретные состояния.

Если модель имеет только дискретные состояния, механизм Simulink вызывает дискретный решатель, выбранный пользователем. Решатель вычисляет размер временного шага, необходимого, чтобы поразить шаги расчета модели. Затем он вызывает метод Update модели. Метод model Update вызывает метод Update своей системы, который вызывает методы Update каждого из блоков, содержащихся в системе, в порядке, заданном списками методов Update, сгенерированными в фазе Link.

Если модель имеет только непрерывные состояния, механизм Simulink вызывает непрерывный решатель, заданный моделью. В зависимости от решателя, решатель либо в свою очередь вызывает метод Производных модели один раз, либо входит в подцикл незначительных временных шагов, где решатель неоднократно вызывает методы Выходов модели и методы Производных, чтобы вычислить выходные и производные модели через последовательные интервалы в течение основного временного шага. Это делается для повышения точности расчета состояния. Метод model Outputs и методы Derivatives в свою очередь вызывают свои соответствующие системные методы, которые вызывают Выходные и Производные блоки в порядке, заданном списками выполнения Выходов и методов Derivatives, сгенерированными в фазе Link.

Опционально проверяет разрывы в непрерывных состояниях блоков.

Метод, называемый обнаружением пересечения нулем, используется для обнаружения разрывов в непрерывных состояниях. Для получения дополнительной информации см. раздел «Обнаружение пересечения нулем».

Вычисляет время для следующего временного шага.

Шаги с 1 по 4 повторяются до тех пор, пока не будет достигнуто время остановки симуляции.