Simulink® Design Verifier™ помогает вам выполнить систематическую верификацию модели, чтобы идентифицировать скрытые ошибки проектирования, доказать свойства и сгенерировать тесты для функционального тестирования. Simulink Design Verifier использует формальные методы, чтобы проверить правильность проекта, которая повышает доверие в вашей модели проекта, которую использует генерация производственного кода.

Можно выполнить систематическую верификацию модели для таких сценариев, как:

Приложения, которые разрабатываются с помощью модельно-ориентированного проектирования, где вы выполняете верификацию проекта, чтобы продемонстрировать, что модель удовлетворяет функциональным требованиям и не содержит непредусмотренной функциональности.

Анализ подмножества модели проекта, которое предназначено для программного обеспечения управления. Для анализа разомкнутого контура контроля формальная проверка широко используется для строгой проверки моделей проекта.

Итеративная проверка модели на соответствие требованиям, проверка на ошибки проектирования и выполнение функционального тестирования в начале рабочего цикла и в течение процесса проектирования.

Систематическая верификация и единичная проверка небольших компонентов в изоляции или для уровня системы проверки интегрированной модели проекта.

Рассмотрите инженера по системам управления, который участвует в разработке системы управления. Во время рабочего цикла инженер по системным требованиям создает модель проекта. На протяжении всего процесса разработки инженер:

Определяет и устраняет скрытые ошибки проектирования

Экспериментальная модель против требований

Выполняет анализ модели и покрытия кода, чтобы подтвердить тщательность тестирования

Устраняет недостающее покрытие с помощью генерации тестов и обнаружения мертвой логики

Выполняет базовую и эквивалентную проверку

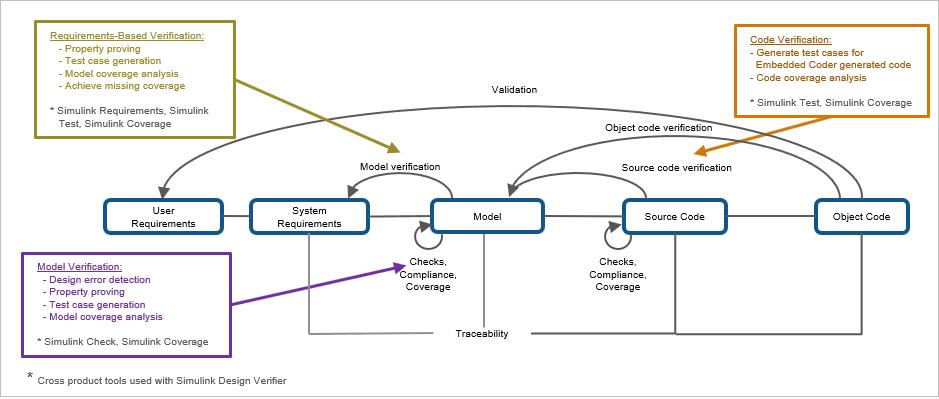

Simulink Design Verifier поддерживает эти процессы верификации модели и кода. Он интегрируется с Simulink Requirements™, Simulink Coverage™, Simulink Check™ и Simulink Test™, чтобы достичь верификации модели и кода.

Верификация модели включает проверку на соответствие стандартам, проверку на ошибки проектирования, проверку свойств и генерацию тестов для анализа покрытия.

С помощью Simulink Design Verifier можно:

Идентифицируйте скрытые ошибки проектирования, такие как целочисленные переполнения или деление на нули и генерируйте контрпримеры для отладки непредусмотренной функциональности. Можно также обосновать или исключить объекты модели из анализа.

Проверьте модель с учетом требований при помощи Simulink Requirements.

Достичь покрытия модели ( Simulink Coverage) путем генерации тестов, которая удовлетворяет целям покрытия модели.

Выполните анализ покрытия кода (Embedded Coder), сгенерировав тесты для кода, сгенерированного Embedded Coder®.

Расширение существующих тестовых случаев и достижение недостающего покрытия.

Интегрируйте тесты с Simulink Test, чтобы выполнить базовую и эквивалентную проверку.

Поддержка отраслевых стандартов с помощью IEC Certification Kit (для IEC 61508 и ISO 26262) и DO Qualification Kit (for DO-178).

Эта схема рабочего процесса демонстрирует возможности Simulink Design Verifier на различных этапах рабочего процесса верификации и валидации. Для получения дополнительной информации см. раздел «Верификация и валидация».

Для быстрого введения в поиск ошибок проектирования и генерации тестов смотрите Обнаружение ошибок проектирования в моделях контроллеров и Генерация тестовых случаев для упрощенной модели круиз-контроля.

Дополнительные сведения об анализе Simulink Design Verifier см. в разделах Поиска ошибок проектирования, Теста Генерации, Докажи Свойства в Модель и Интерпретация и использование результатов.

Можно также создавать отчеты и просматривать результаты анализа. Существует несколько способов просмотреть результаты анализа:

Просмотрите результаты анализа с первого взгляда, подсвечивая результаты на модели.

Создайте модель тестовой обвязки, чтобы симулировать тесты или отладку контрпримеры.

Сгенерируйте отчет о покрытии модели.

Просмотрите сгенерированные тесты в Данные моделирования Inspector.

Сгенерируйте HTML или PDF отчет, содержащий подробную информацию о результатах анализа.