Общие шаблоны моделирования, которые приводят к мертвой логике в модели, включают:

Когда вы выполняете поиск ошибок проектирования анализ, Simulink® Design Verifier™ сообщает об общих причинах мертвой логики в окне Results.

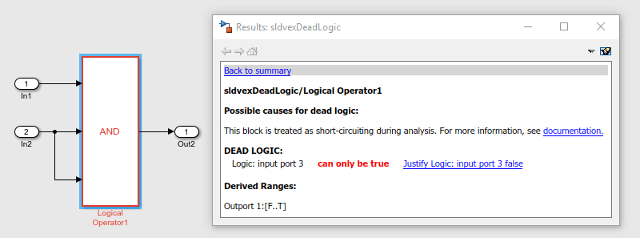

Simulink Design Verifier обрабатывает логические блоки так, как если бы они были короткозамкнутыми при анализе на мертвую логику.

Для примера в этой модели, если In2 false, программное обеспечение игнорирует третий вход из-за короткого замыкания. В окне Results этот порт отображается как мертвая логика. Смотрите Логические операции Короткое замыкание.

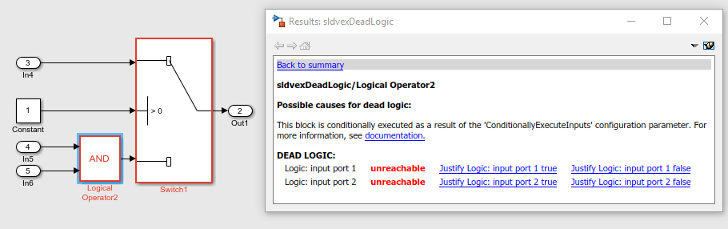

Если ваша модель состоит из Switch или Multiport Switch блоков, и параметр Conditional input branch execution установлен в Onусловное выполнение часто может вызвать неожиданную мертвую логику.

Рассмотрим эту модель примера, где параметр Conditional input branch execution установлен в On. Блок Logical Operator AND выполняется по условию, что вызывает мертвую логику для блока. Для получения дополнительной информации смотрите Выполнение условной входной ветви.

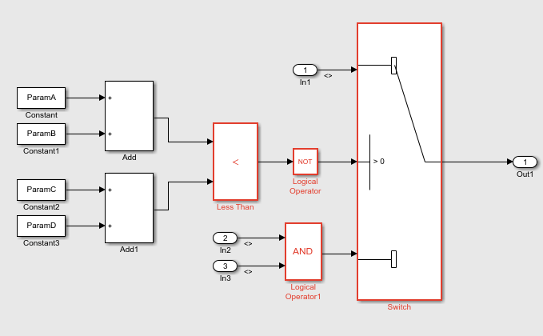

Если ваша модель содержит параметры, Simulink Design Verifier по умолчанию рассматривает значения как константы. Это может вызвать мертвую логику в модели. В этих случаях рассмотрите настройку этих параметров для настройки во время анализа. Для получения дополнительной информации смотрите Inlined Parameters.

Например, рассмотрим эту модель, где все параметры установлены в нуль. Эти настройки вызывают мертвую логику для блока Less Than.

Когда конкретный блок имеет мертвую логику, это часто приводит к каскадному эффекту, который заставляет нисходящие блоки иметь мертвую логику.

Рассмотрим приведенную выше модель примера. Мертвая логика в блоке Less Than вызывает мертвую логику в соответствующих нисходящих блоках. Поэтому часто полезно просмотреть вышестоящую мертвую логику, прежде чем рассматривать любую нисходящую мертвую логику.

Библиотечные блоки могут быть записаны с защитными условиями, которые являются избыточными в некоторых местах, где они используются. В некоторых случаях это может вызвать мертвую логику. Поиски ошибок проектирования см. в разделе «Исключение и обоснование целей».

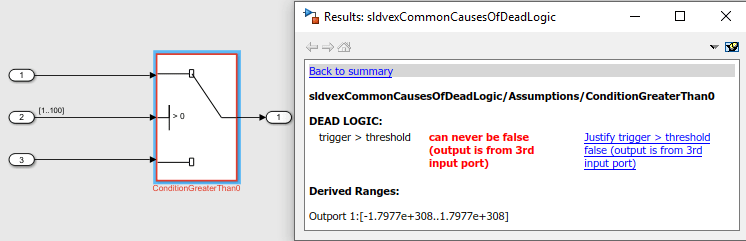

Блоки Inport корневого уровня с минимальными и максимальными значениями в качестве ограничений и блоки Test Condition в генерации тестов могут вызвать мертвую логику. Например, рассмотрите блок Switch ConditionGreaterThan0 где второй блок Inport имеет минимальную и максимальную область значений значений 1 и 100, соответственно. Это заставляет блок Switch в этой подсистеме иметь мертвую логику.