Подобно графикам эффективности памяти, сгенерированным в симуляции, можно собрать информацию о взаимосвязанном трафике памяти из проекта, выполняемого на FPGA. Затем можно сгенерировать аналогичные графики эффективности. Можно также захватить информацию о транзакции памяти для просмотра в инструменте Logic Analyzer, подобном пакетным транзакциям от контроллера памяти в симуляции. Используйте эти графики для мониторинга реальной эффективности памяти, отлаживания и улучшения проекта и сравнения их с эффективностью памяти, полученными в симуляции.

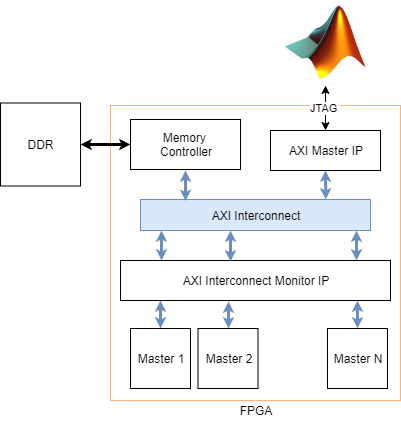

Чтобы включить AXI interconnect monitor (AIM) IP в проект, в параметры конфигурации модели, выберите опцию Include AXI interconnect monitor в разделе Hardware Implementation > Target hardware resources > FPGA design (debug). IP-адрес AXI interconnect monitor собирает информацию из проекта во время работы на FPGA. Вы можете запросить эту информацию из MATLAB® при помощи соединения JTAG. Все мастера памяти в вашем FPGA подключены к IP-адресу AXI interconnect monitor. Эти мастера могут включать Memory Channel и Memory Traffic Generator блоки, для которых вы сгенерированными HDL-кодами, или любые другие мастера в вашем проекте.

Инструмент SoC Builder генерирует скрипт испытательного стенда JTAG для вашего проекта. Скрипт собирает метрики эффективности из AXI interconnect monitor и запускает приложение построения графика эффективности, которое строит графики эффективности памяти для пропускной способности, количества пакетов и задержек транзакций. Эти графики аналогичны графикам эффективности памяти в симуляции. Можно также изменить скрипт, чтобы собрать и отобразить форму транзакции памяти, подобную формам пакетных сигналов контроллера памяти в симуляции. Для получения информации о производительности симуляционной памяти смотрите Графики эффективности симуляции и Буферные и Пакетные формы волны.

Для получения примера смотрите Анализ полосы пропускания памяти с помощью генераторов трафика, который показывает, как контролировать эффективность памяти как в симуляции, так и при запуске на FPGA. Скрипт, сгенерированный инструментом SoC Builder, использует соединение JTAG, чтобы включить любые генераторы трафика в вашем проекте, а затем производит выборку информации о эффективности памяти из IP-адреса AXI interconnect monitor так быстро, как это возможно. Интервал дискретизации зависит от задержки JTAG, которая обычно составляет от 10 мс до 20 мс. Затем скрипт отображает графики, подобные графикам эффективности из блока Memory Controller в вашей симуляции. График отображает пропускную способность, количество пакетов и задержку транзакций для каждого ведущего устройства.

Примечание

Сам мастер AXI не соединяется с AXI interconnect monitor. Поэтому аппаратная диагностика не включает в себя графики использования памяти для мастеров только для тестирования, которые инициализируют память с заранее заданными данными.

Скрипт собирает метрики эффективности из AXI interconnect monitor и запускает приложение построения графика эффективности.

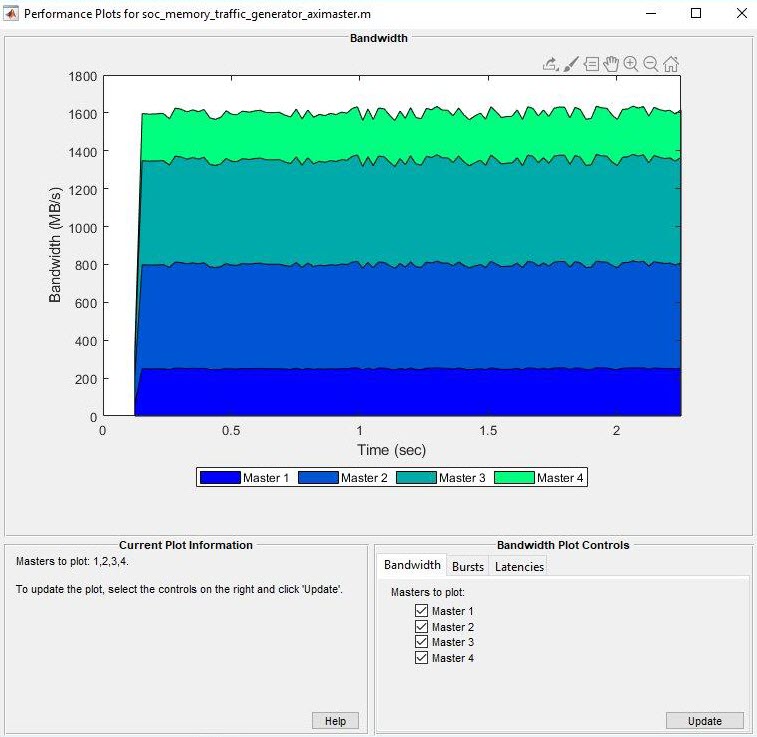

На вкладке Bandwidth выберите шаблоны, для которых необходимо построить график полосы пропускания. Щелкните Create Plot, чтобы увидеть пропускную способность в мегабайтах в секунду для выбранных мастеров за время запуска. Этот рисунок показывает пропускную способность для примера анализа полосы пропускания памяти с использованием генераторов трафика.

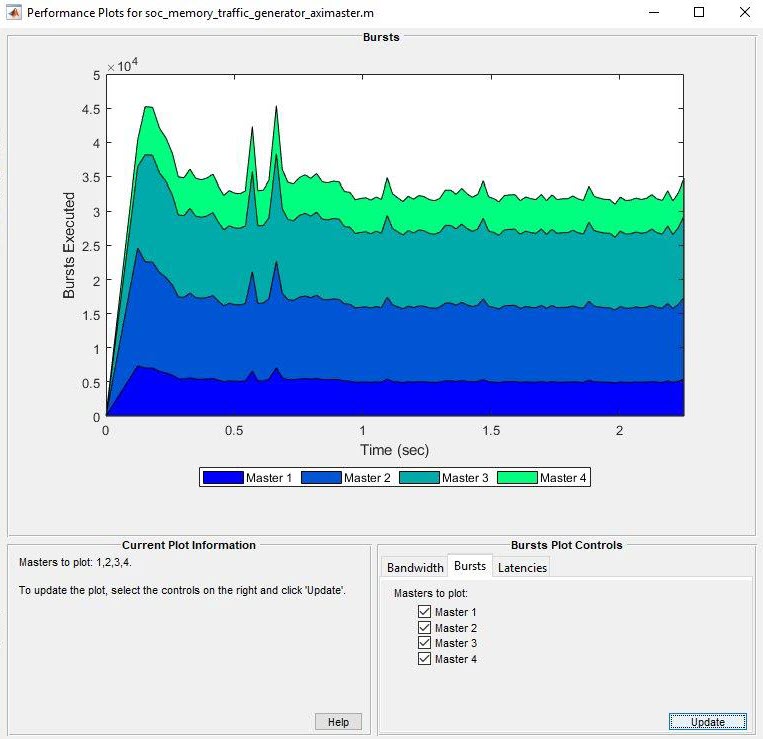

На вкладке Bursts выберите шаблоны, для которых необходимо выполнить граф пакетов. Щелкните Create Plot, чтобы увидеть количество пакетов, выполненных для выбранного ведущего за время запуска. Этот рисунок показывает количество пакетов для примера Analyze Memory Bandwidth Using Traffic Generators.

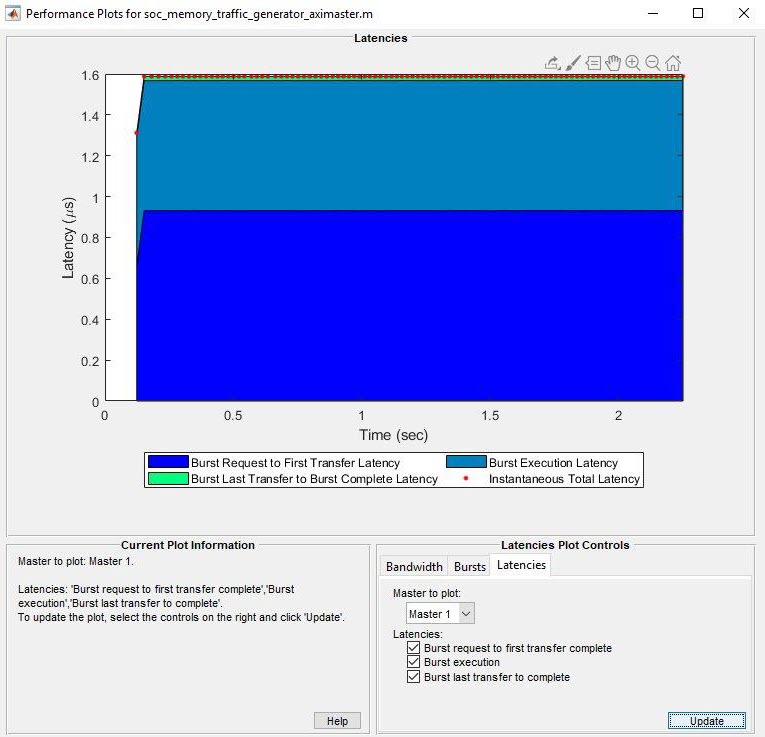

На вкладке Latencies выберите мастер, для которого необходимо построить график задержек. Щелкните Create Plot, чтобы увидеть задержки для выбранных мастеров в течение длительности запуска. На этом изображении показана общая задержка для Master 1 в примере Analyze Memory Bandwidth Using Traffic Generators. Затем можно масштабировать, чтобы проанализировать пиковую мгновенную задержку.

Вы можете выбрать один из следующих опций:

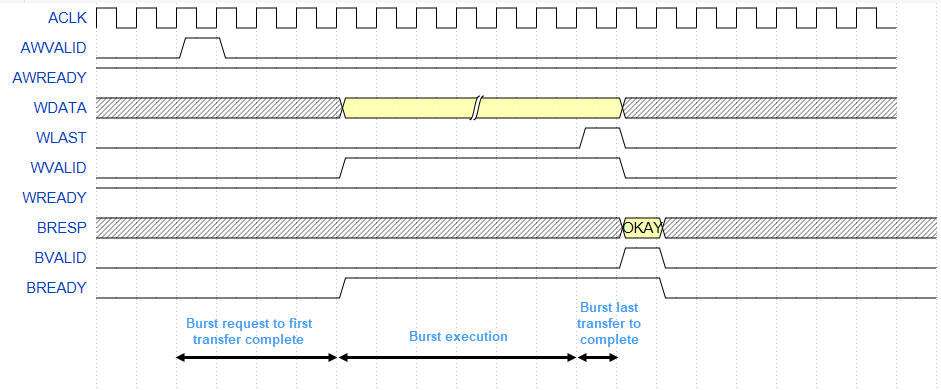

Burst request to first transfer complete - эта опция показывает время, затраченное с момента выдачи мастером запроса на транзакцию до первой передачи данных. Эта задержка учитывает арбитражные или межсоединительные задержки.

Burst execution - эта опция показывает время, которое требуется от первой передачи данных до последней передачи пакета.

Burst last transfer to complete - эта опция показывает время, которое требуется от последнего переноса до завершения транзакции. В случае считывания транзакции значение 0.

Instantaneous Total Latency - Эта опция показывает дискретные измерения общей задержки на пакет.

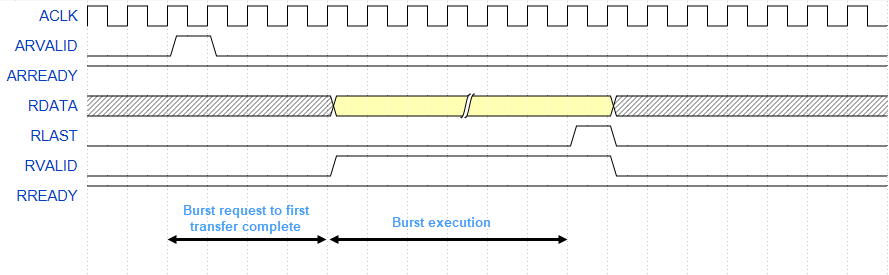

Каждое нанесенное значение задержки является средним значением соответствующей задержки, измеренной из транзакций памяти в течение интервала дискретизации. Следующий рисунок показывает транзакцию записи и чтения протокола AXI4 Master на оборудовании, показывающую каждую из этих задержек.

Write Transaction

Read Transaction

В транзакции read Burst last transfer to complete latency равен нулю.

В Profile режим, collectMemoryStatistics выборки функций памяти метрики: полоса пропускания, пакет и задержки, значения из оборудования после каждой выборки. После этого функция сбрасывает счетчики метрики и затем снова запускает счетчики для следующей выборки. Если какой-либо из счетчиков метрики превышает предел 232 - 1 в пределах интервала дискретизации счетчик переполнен и соответствующая выборка обозначена * на графике.

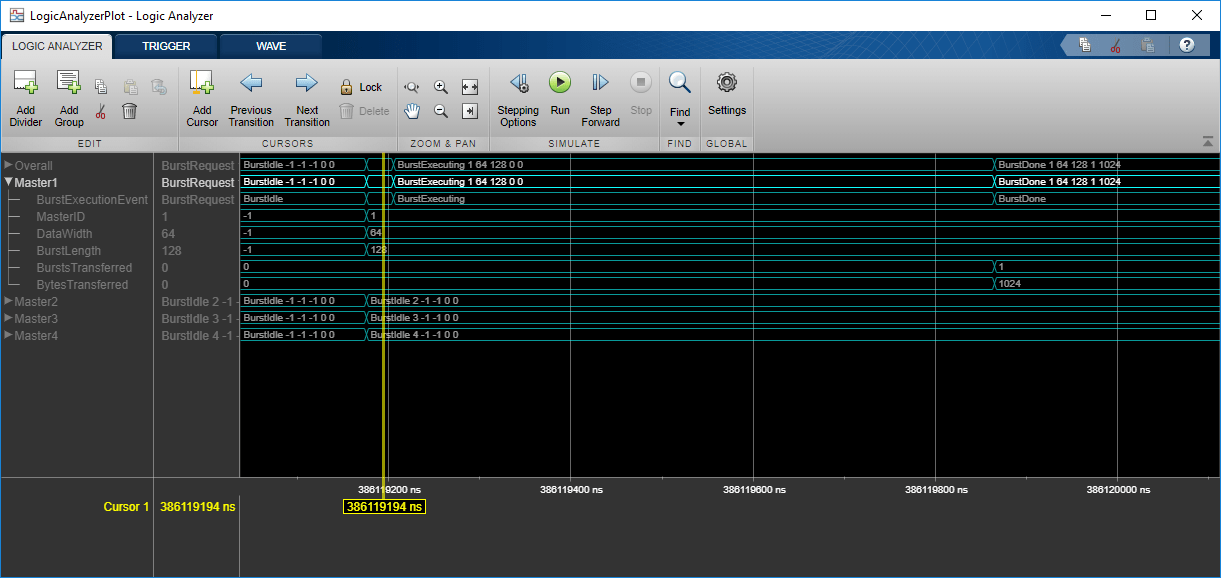

Можно также изменить сгенерированный скрипт, чтобы сконфигурировать AXI interconnect monitor для сбора данных о событиях для каждой пакетной транзакции. Можно просмотреть эти события в программе средства просмотра Logic Analyzer сигналов, чтобы изучить поведение арбитража. Укажите количество транзакций для захвата, Trace capture depth, в параметрах конфигурации модели, под Hardware Implementation > Target hardware resources > FPGA design (debug).

Формы волны показывают тип события (BurstIdle, BurstRequest, BurstExecuting, или BurstDone) и эти параметры пакетной транзакции:

MasterID - идентификационный номер хозяина памяти, который сделал запрос

DataWidth -- Ширина данных в битах

BurstLength -- Количество слов данных в пакетном запросе

BurstsTransferred -- Количество пакетов в этом запросе (допустимо только с BurstDone событие)

BytesTransferred -- Количество байтов в этом запросе (допустимо только с BurstDone событие)

Можно сравнить эти формы волны с формами сигналов, захваченными из блока Memory Controller в симуляции.

AXI interconnect monitor (AIM) является IP-ядром, которое собирает показатели эффективности для проекта FPGA на основе AXI. Создайте socIPCore объект для настройки и конфигурирования IP AIM и использования socMemoryProfiler объект для извлечения и отображения данных.

Пример конфигурирования и запроса IP AIM в проекте с использованием MATLAB в качестве AXI Master см. в разделе Анализ полосы пропускания памяти с помощью генераторов трафика. В частности, проверьте soc_memory_traffic_generator_axi_master.m скрипт, который конфигурирует и контролирует проект устройства.

Этот AXI interconnect monitor может собирать два типа данных. Выберите Profile режим для сбора средней задержки транзакции и счетчиков байтов и пакетов. В этом режиме можно открыть графический инструмент эффективности, а затем сконфигурировать инструмент для построения графика полосы пропускания, счетчика пакетов и задержки транзакций. Выберите Trace режим для сбора подробных данных о событиях транзакции памяти и просмотра данных как осциллограмм.

perfMonMode = 'Profile'; % or 'Trace'

Чтобы получить диагностические показатели эффективности из вашего сгенерированного проекта FPGA, необходимо настроить подключение JTAG к устройству из MATLAB. Загрузка .mat файл, содержащий структуры, выведенные из параметров конфигурации платы. Этот файл был сгенерирован инструментом SoC Builder. Эти структуры описывают взаимосвязи между памятью и главами строения такие как размеры буфера и адреса. Используйте socHardwareBoard объект для настройки соединения JTAG.

load('soc_memory_traffic_generator_zc706_aximaster.mat'); hwObj = socHardwareBoard('Xilinx Zynq ZC706 evaluation kit','Connect',false); AXIMasterObj = socAXIMaster(hwObj);

socIPCore объект предоставляет функцию, которая выполняет эту инициализацию. Затем настройте socMemoryProfiler объект, чтобы собрать метрики.apmCoreObj = socIPCore(AXIMasterObj,perf_mon,'PerformanceMonitor','Mode',perfMonMode); initialize(apmCoreObj); profilerObj = socMemoryProfiler(hwObj,apmCoreObj);

Чтобы извлечь метрики эффективности или данные о сигнале из проекта, выполняемого на FPGA, используйте socMemoryProfiler функции объекта.

Для Profile mode, вызовите collectMemoryStatistics функция в цикле.

NumRuns = 100; for n = 1:NumRuns collectMemoryStatistics(profilerObj); end

Для Trace mode, вызовите collectMemoryStatistics функция один раз. Эта функция препятствует записи транзакций IP в FIFO в AXI interconnect monitor IP, хотя транзакции продолжаются в соединении. Установите размер транзакции FIFO, Trace capture depth, в параметрах конфигурации модели, под Hardware Implementation > Target hardware resources > FPGA design (debug).

collectMemoryStatistics(profilerObj);

Визуализируйте данные о эффективности, используя plotMemoryStatistics функция. В Profile mode, эта функция открывает графический инструмент эффективности, и можно настроить инструмент для построения графика полосы пропускания, счетчика пакетов и средней задержки транзакций. В Trace эта функция открывает инструмент Logic Analyzer для просмотра данных о событиях пакетной транзакции.

plotMemoryStatistics(profilerObj);

collectMemoryStatistics | Memory Controller | plotMemoryStatistics | socMemoryProfiler