Буферизуйте входной поток, чтобы создать линии изображения, которые имеют смежные допустимые пиксели

Vision HDL Toolbox/Утилиты

Блок Pixel Stream FIFO сохраняет входящие действительные пиксели и сопутствующие сигналы управления и возвращает тот же поток пикселей без зазоров между допустимыми пикселями каждой линии. Блок сохраняет общий размер линии и общий формат кадра видеопотока, включая недопустимые циклы.

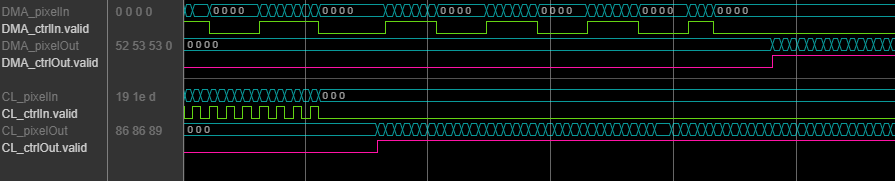

Используйте блок Pixel Stream FIFO для буферизации источников видео. Форма волны показывает источник видео прямого доступа к памяти (DMA), где пиксели считываются пакетно, и Ссылка® источник видео, где пиксели действительны каждый второй тактовый цикл. Чтобы создать смежные линии видео, блок Pixel Stream FIFO буферизует пиксели входа и управляет сигналами каждого источника.

Этот блок использует интерфейс потокового пикселя с шиной для сигналов управления системой координат. Этот интерфейс позволяет блоку работать независимо от размера и формата изображения. Порты pixel на этом блоке поддерживают потоковую передачу с одним пикселем или многопиксельную потоковую передачу. Потоковая передача с одним пикселем принимает и возвращает одно значение пикселя каждый такт. Мультипиксельная потоковая передача принимает и возвращает 4 или 8 пикселей за тактовый цикл для поддержки форматов с высокой частотой кадров или с высоким разрешением. Вместе с пикселем блок принимает и возвращает pixelcontrol шина, которая содержит пять управляющих сигналов. Сигналы управления указывают валидность каждого пикселя и их местоположение в системе координат. Для многопиксельной потоковой передачи один набор управляющих сигналов применяется ко всем четырем или восьми пикселям в векторе. Чтобы преобразовать систему координат (пиксельную матрицу) в последовательный поток пикселей и сигналы управления, используйте блок Frame To Pixels. Полное описание интерфейса см. в разделе Потоковый пиксельный интерфейс.

Этот блок также поддерживает мультипиксельные многокомпонентные потоки, где пиксельный вход является матрицей значений M-на-N, где M - количество пикселей, а N - количество компонентов. Эти значения соответствуют Number of pixels и Number of components параметрам блока Frame To Pixels.

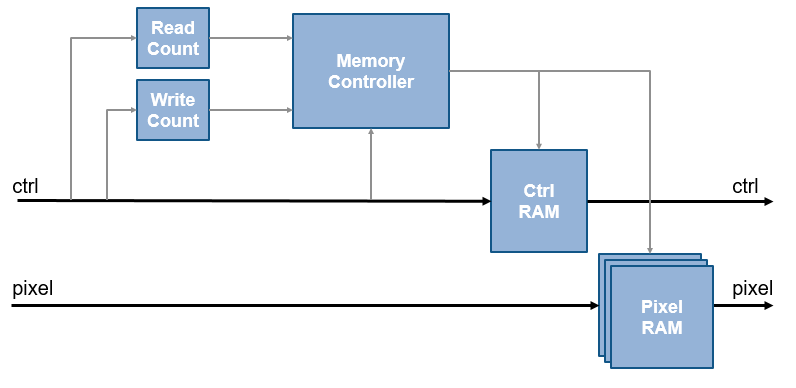

Блок Pixel Stream FIFO содержит контроллер памяти, счетчики чтения и записи и две ОЗУ. Одна ОЗУ сохраняет входные сигналы управления, а другая сохраняет входящий поток пикселей. Блок хранит действительные пиксели и сопровождающие их сигналы управления для каждой строки, как определяется входным ctrl hStart. и ctrl. hEnd сигналы. Буферизация удаляет любое групповое поведение входа потока. Когда сохранена полная линия действительных пикселей, блок возвращает новую непрерывную версию линии.

Когда вход pixel является вектором или матрицей, блок наследует Pixel RAM для каждого элемента. Схема показывает три Pixel RAM, чтобы представлять трехкомпонентный поток пикселей. Для многопиксельной потоковой передачи блок настраивает линейный buffer size, чтобы хранить 1/ Number of pixels пикселей. Например, с входным потоком 4 на 3, каждый буфер хранит ¼ из пикселей для линии, поэтому существует 12 пиксельных ОЗУ, каждый с 2m-2 местоположения.