Вычисляет быстрое-фурье-преобразование (FFT) для стандартной полосы пропускания LTE на 15 МГц

Беспроводной HDL Toolbox/модуляция

Блок FFT 1536 предназначен для поддержки LTE стандартной полосы пропускания 15 МГц. Этот блок используется в LTE OFDM Demodulator операции блока. Блок принимает входные данные вместе с действительным сигналом управления и выводит потоковые данные с samplecontrol шина.

Блок обеспечивает архитектуру, подходящую для генерации HDL-кода и аппаратного развертывания.

data - Входные данныеВходные данные, заданные как скаляр вещественных или комплексных чисел.

double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Чем больше дробных бит вы предоставляете в вход размера слова, тем лучше точность, которую вы получаете в выходе.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

valid - Указывает на действительные входные данныеУказывает, действительны ли входные данные. Когда входной valid 1 (true), блок захватывает значение на входном data порте. Когда входной valid 0 (false), блок игнорирует входные data выборки.

Типы данных: Boolean

reset - Сброс управляющего сигналаКогда это значение 1 (true), блок останавливает текущее вычисление и очищает все внутренние состояния.

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data - Выходные данные частотного каналаВыходные данные частотного канала, возвращенные как скаляр действительных или комплексных чисел.

Когда вход fixed point тип данных, тип выходных данных совпадает с типом входных данных. Когда вход имеет целый тип, тип выходных данных fixed point тип.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

ctrl - Сигналы управления, сопровождающие поток выборокsamplecontrol автобусУправляющие сигналы, сопровождающие поток дискретизации, возвращаются как samplecontrol bus. Шина включает в себя start, end, и valid управляющие сигналы, которые указывают контуры системы координат и валидность выборок.

start - Указывает начало выходной системы координат

end - Указывает конец выходной системы координат

valid - Указывает, что данные выходного data порта действительны

Для получения дополнительной информации см. Выборку шины управления.

Типы данных: bus

Complex multiplication - Реализация HDLUse 3 multipliers and 5 adders (по умолчанию) | Use 4 multipliers and 2 addersЗадает тип комплексного множителя для реализации HDL. Каждое умножение реализуется либо с помощью Use 3 multipliers and 5 adders или с Use 4 multipliers and 2 adders. Скорость реализации зависит от инструмента синтеза и целевого устройства, которое вы используете.

Rounding method - Режим округления для внутренних вычислений фиксированной точкиFloor (по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroЗадает тип метода округления для внутренних вычислений с фиксированной точкой. Для получения дополнительной информации о методах округления см. Раздел «Режимы округления» (DSP System Toolbox). Когда вход является любым целым числом или типом данных с фиксированной точкой, этот блок использует арифметику с фиксированной точкой для внутренних вычислений. Этот параметр не применяется, когда входные данные single или double.

Normalize butterfly output - Выходoff (по умолчанию) | onКогда вы выбираете этот параметр, блок делит выход на 1536. Эта опция полезна, когда вы хотите, чтобы выход блока оставался в той же амплитуде, область значений и его вход. Вы требуете эту опцию, когда вход fixed point тип.

Когда вы выбираете этот параметр, длина выходного слова увеличивается на 2 бита, и когда вы очищаете этот параметр, длина выходного слова увеличивается на 11 бит.

Enable reset input port - Дополнительный сигнал сбросаoff (по умолчанию) | onВыберите этот параметр, чтобы включить reset порт.

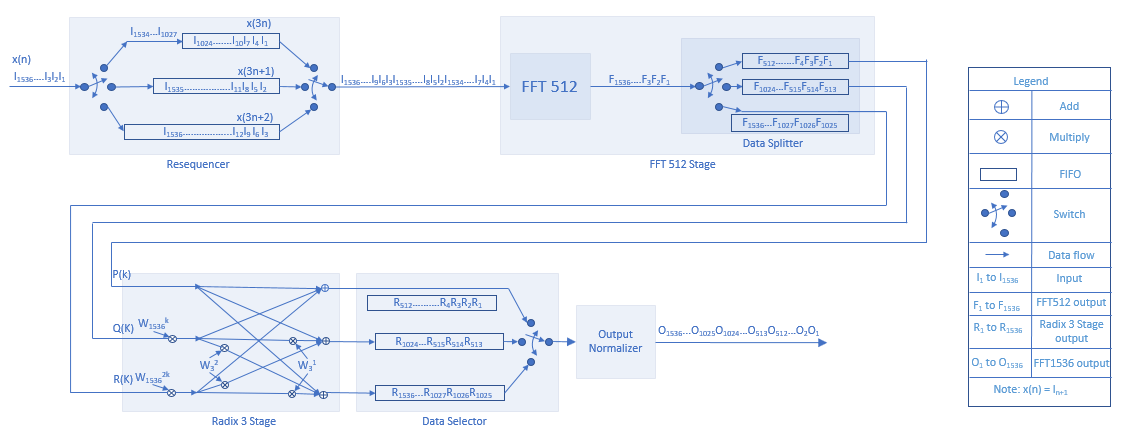

Для разработки блока FFT 1536 реализован алгоритм децимации radix-3 в времени (DIT). Последовательность входа x (n) для всех n = {0,1,2.... 1535} разделена на три последовательности DIT, x (3n), x (3n + 1), x (3n + 2) для всех n = {0,1,2.... 511}.

Это уравнение задает расчет БПФ 1536 заданной последовательности x (n).

Уравнение может быть реализовано путем деления его на три части, где P (k), Q (k), R (k) являются N/3 (БПФ 512) точечным БПФ x (3n), x (3n + 1) и x (3n + 2), соответственно. Здесь N = 1536, и k = 0,1,2,....., 511.

Эта схема показывает внутреннюю архитектуру блока и то, как входная последовательность течет через компоненты блока.

Последовательность входа x (n) демультиплексируется в три последовательности DIT, x (3n), x (3n + 1), x (3n + 2), каждая из 512 длины. Три памяти первого ввода (FIFO) сохраняют эти последовательности. Эти последовательности DIT сериализуются и транслируются через блок FFT 512.

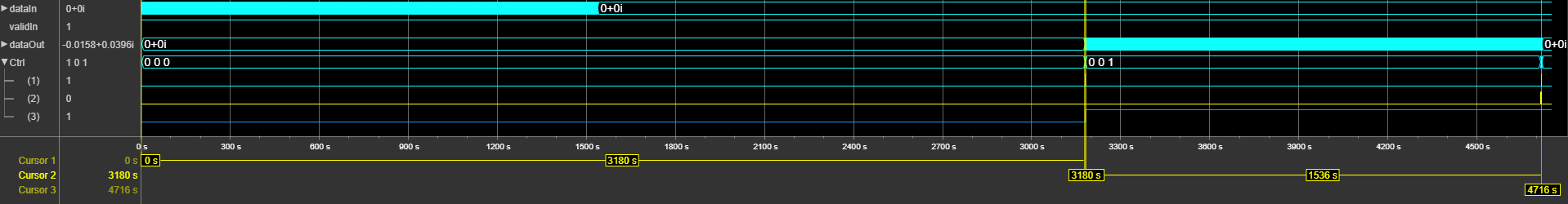

Это изображение показывает выход сигнала блока при работе с параметрами конфигурации по умолчанию. Блок обеспечивает выходные данные после задержки 3180 тактов. Длина выходных данных между start (Ctrl.(1)) и end (Ctrl.(2)) выходные сигналы управления составляют 1536 тактов.

Эффективность синтезированного HDL-кода варьируется с вашей целью и опциями синтеза. В этой таблице показаны результаты синтеза ресурсов и данных о эффективности блока с параметрами конфигурации по умолчанию, наряду с включенной функцией нормализации и входными данными в fixdt(1,17,15) формат. Сгенерированный HDL нацелен на Xilinx® Zynq® XC7Z045-FFG900-2 плату FPGA. Проект достигает тактовой частоты 355 МГц.

| Ресурс | Используемое число |

|---|---|

| LUTs | 7330 |

| Регистры | 9325 |

| Блокируйте ОЗУ | 18 |

| DSPs | 36 |

Этот блок поддерживает генерацию кода C/C + + для Simulink® режимы Accelerator и Rapid Accelerator и для генерации компонентов DPI.

HDL Coder™ предоставляет дополнительные опции строения, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет одну архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

Вы не можете сгенерировать HDL для этого блока внутри Resettable Synchronous Subsystem (HDL Coder).

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.