Сгенерируйте биты кода CRC и добавьте их к входным данным

Беспроводной HDL Toolbox/Обнаружение и коррекция ошибок

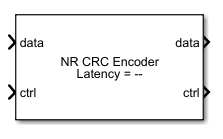

Блок NR CRC Encoder вычисляет и генерирует короткую двоичную последовательность фиксированной длины, известную как контрольная сумма циклического контроля избыточности (CRC), добавляет ее к каждой системе координат потоковых выборок данных и выводит данные с кодированием CRC. Блок принимает и возвращает поток выборки данных с сопутствующими сигналами управления. Сигналы управления указывают на валидность выборок и контуров системы координат.

Блок поддерживает скаляр и векторные входы и выводит данные как скаляр или вектор на основе входных данных. Чтобы достичь более высокой пропускной способности, блок принимает двоичный вектор или беззнаковый целочисленный скалярный вход и реализует параллельную архитектуру. Ширина входных данных должна быть меньше или равной длине полинома CRC, а длина полинома CRC должна быть делена на ширину входных данных. Блок поддерживает все полиномы CRC, заданные в соответствии со стандартом 5G new radio (NR) 3GPP TS 38.212 [1]. Когда вы выбираете полином CRC24C, блок поддерживает динамическую маску CRC.

Блок обеспечивает интерфейс и аппаратно оптимизированную архитектуру, подходящую для генерации HDL-кода и оборудования развертывания.

[1] 3GPP TS 38.212. "NR; Мультиплексирование и канальное кодирование ". 3-ья Генерация проект Партнерства; Группа технических спецификаций Радиосеть доступ.

[2] Кампобелло, Г., Г. Патане и М. Руссо. «Параллельная реализация CRC». Транзакции IEEE на компьютерах 52, № 10 (октябрь 2003 года): 1312-19. https://doi.org/10.1109/TC.2003.1234528.