Цикл (FIL) позволяет вам запустить Simulink® симуляция, которая синхронизируется с проектом, работающим на Intel® или Xilinx® Плата FPGA. Эта ссылка между симулятором и платой позволяет вам проверить реализации HDL непосредственно против Simulink или MATLAB® алгоритмы. Можно применить реальные данные и сценарии тестирования из этих алгоритмов к проекту на FPGA.

При симуляции блоков Wireless HDL Toolbox™ необходимо использовать потоковый пример интерфейса. Потоковая передача выборочных данных, хотя и требуется для аппаратных реализаций коммуникационных систем, занимает много времени в интерфейсе цикл с Simulink.

Можно преобразовать из систем координат в выборки и выборки в системы координат либо в Simulink, либо в MATLAB. В зависимости от вашего рабочего процесса, можно оптимизировать симуляцию цикл одним из двух способов.

Одним из рабочих процессов является модель Simulink, которая импортирует данные с рамками из MATLAB. Этот тип модели затем использует блоки Frame To Samples и Samples To Frame для преобразования формата данных. Для цикл замените эти блоки преобразования на блоки FIL Frame To Samples и FIL Samples To Frame.

Другой рабочий процесс является моделью Simulink, которая импортирует потоковые данные из MATLAB. Этот тип модели идет со скриптом MATLAB, который использует ltehdlFrameToSamples и ltehdlSamplesToFrames функций. Для цикл измените свой скрипт и модель Simulink так, чтобы они передали векторы данных в интерфейс цикл.

Когда вы генерируете файл программирования для цели FIL в Simulink, инструмент создает модель, чтобы сравнить симуляцию FIL с вашими проектами Simulink. Для проектов Wireless HDL Toolbox, блок FIL в этой модели наследует потоковый интерфейс сэмплирования и отправляет по одной выборке за раз в FPGA. Обе эти модификации создают векторы, которые более эффективно используют интерфейс между моделью Simulink и платой FPGA.

Инструкции, которые следуют ниже, показывают, как изменить модели цикл для верификации Turbo Decoder с потоковыми данными из MATLAB и Verify Turbo Decoder с обрамленными данными из примеров рабочего процесса MATLAB.

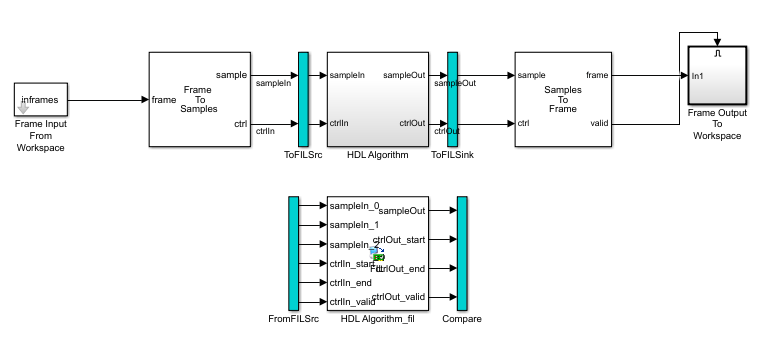

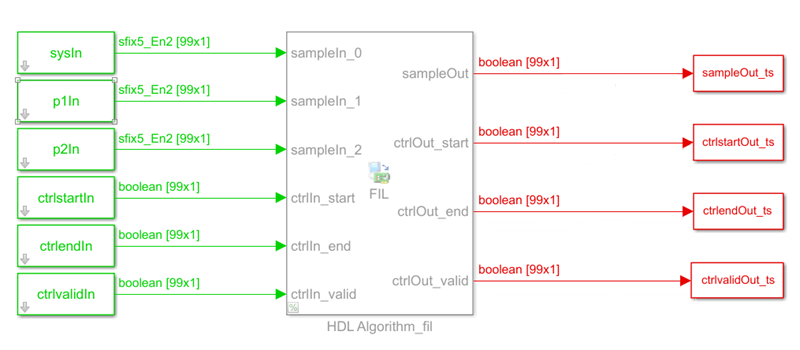

Сгенерированная модель, включая блок FIL, который взаимодействует с платой FPGA, показана для модели, которая преобразуется в потоковые выборки в Simulink. Если каждая выборка представлена несколькими значениями, значения выравниваются в отдельные порты для FIL.

Подсистема синего ToFILSrc ветвляет вход потока дискретизации блока HDL Algorithm к подсистеме FromFILSrc. Подсистема синего ToFILSink ветвляет поток сэмплирования выхода блока HDL Algorithm в подсистему Compare, где сравнивается с выходом блока HDL Algorithm_fil. Эта настройка является медленной, потому что модель отправляет только одну выборку и связанные с ней сигналы управления в каждом пакете на плату FPGA и от нее.

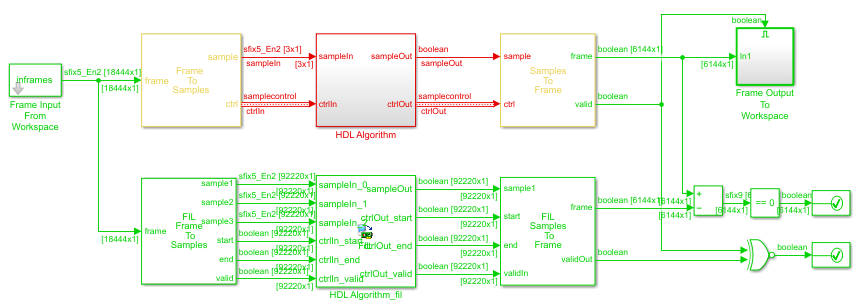

Чтобы улучшить пропускную способность связи с платой FPGA, измените автогенерированную модель. Измененная модель использует блоки FIL Frame To Samples и FIL Samples To Frame, чтобы отправлять по одной системе координат за раз.

Чтобы создать эту измененную модель FIL:

Удалите синие подсистемы и создайте ветвь у frame входного порта блока Frame To Samples.

Вставьте FIL Frame To Samples блок перед блоком HDL Algorithm_fil. Вставьте FIL Samples To Frame блок после блока HDL Algorithm_fil.

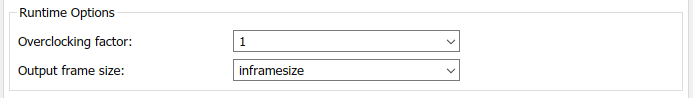

Установите размер Output frame size на блоке FIL входного кадра.

В блоках FIL Frame To Samples и FIL Samples To Frame установите параметры, соответствующие настройкам блоков Frame To Samples и Samples To Frame.

Ветвь системы координат выхода блока Samples To Frame для сравнения. Можно сравнить всюсь систему координат сразу с блоком Diff. Сравните validOut сигналы, использующие блок XOR.

Размер входа в блоке FIL является форматом кадра из систем координат входных данных. Размер вектора портов блоков FIL не изменяет сгенерированный HDL-код. Это влияет только на размер пакета связи между симулятором и платой FPGA. Эта измененная модель отправляет целую систему координат на плату FPGA в каждом пакете, значительно улучшая эффективность ссылки связи.

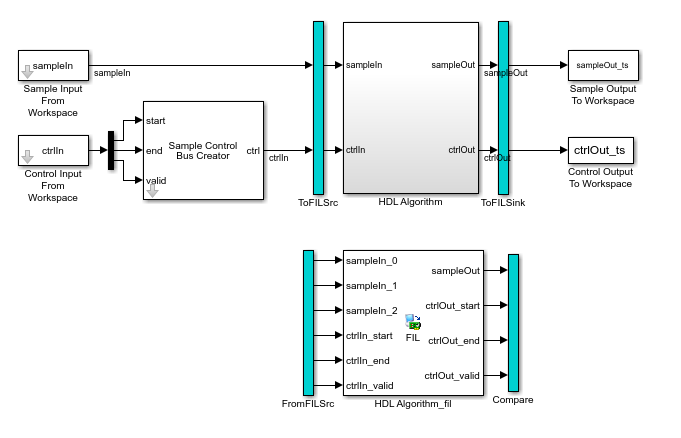

Сгенерированная модель, включая блок FIL, который взаимодействует с платой FPGA, показана для модели, которая преобразуется в потоковые выборки в MATLAB. Если каждая выборка представлена несколькими значениями, значения выравниваются в отдельные порты для FIL.

Подсистема синего ToFILSrc ветвляет вход потока дискретизации блока HDL Algorithm к подсистеме FromFILSrc. Подсистема синего ToFILSink ветвляет поток сэмплирования выхода блока HDL Algorithm в подсистему Compare, где сравнивается с выходом блока HDL Algorithm_fil. Эта настройка является медленной, потому что модель отправляет только одну выборку и связанные с ней сигналы управления в каждом пакете на плату FPGA и от нее.

Чтобы улучшить пропускную способность связи с платой FPGA, используйте сгенерированный блок FIL в другой модели. Альтернативная модель импортирует и экспортирует векторы уплощенных данных. Сопроводительный скрипт MATLAB изменяет форму входных и выходных данных и проверяет выход FIL на соответствие поведенческой модели. Изменение формы данных в MATLAB легче, и симуляция происходит быстрее, чем изменение формы в Simulink.

Сначала измените сопутствующий скрипт MATLAB:

Выберите формат кадра для симуляции FIL. Этот размер не должен совпадать с фактическими форматами кадра в сгенерированных данных. Он может содержать весь ваш набор данных. Блок FIL разделяет данные на пакеты максимального размера для связи с платой FPGA.

filframesize = 99;

Объедините массив ячеек входных кадров в одну матрицу.

allframes = [inframes{:}];

Выровняйте выборки и сигналы управления так, чтобы на блоке FIL был один вектор для каждого входного порта. Эта модель включает блок LTE Turbo Decoder, поэтому входные выборки состоят из трех значений.

sysIn = allframes(1:3:end); p1In = allframes(2:3:end); p2In = allframes(3:3:end); ctrlstartIn = ctrlIn(1:3:end); ctrlendIn = ctrlIn(2:3:end); ctrlvalidIn = ctrlIn(3:3:end);

Вызовите модель FIL.

simTime = size(allframes,1);

modelname = 'TurboDecoderStreamingFILVectortoSL';

open_system(modelname);

sim(modelname);

Измените форму выходных переменных для входа на whdlSamplesToFrames функция. Воссоздайте N -by-3 матрицу управляющего сигнала и вектор выборочных данных. В этом примере выборка выхода является одним значением. Если выходная выборка является несколькими значениями, создайте N -by SampleSize матрицу выборки.

sampleOut = squeeze(sampleOut_ts.Data); ctrlOut = [squeeze(ctrlstartOut_ts.Data) ... squeeze(ctrlendOut_ts.Data) ... squeeze(ctrlvalidOut_ts.Data)];

Затем создайте модель Simulink:

Скопируйте сгенерированный блок FIL в новую модель.

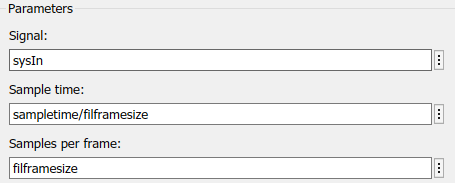

Сконфигурируйте и соедините блок Signal From Workspace для каждого входного порта на блоке FIL. Используйте переменные из скрипта MATLAB в качестве значений параметров.

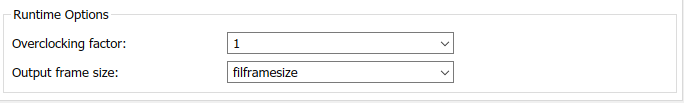

Установите Output frame size на блоке FIL в требуемый формат кадра FIL.

Сконфигурируйте и соедините блок To Workspace для каждого выходного порта блока FIL.

Размер входа в блоке FIL является форматом кадра, заданным на блоках Signal To Workspace. Размер вектора портов блоков FIL не изменяет сгенерированный HDL-код. Это влияет только на размер пакета связи между симулятором и платой FPGA. Эта измененная модель отправляет целую систему координат на плату FPGA в каждом пакете, значительно улучшая эффективность ссылки связи.