Многофазный набор фильтров и быстрое преобразование Фурье — оптимизированный для генерации HDL-кода

Поддержка HDL DSP System Toolbox / фильтрация

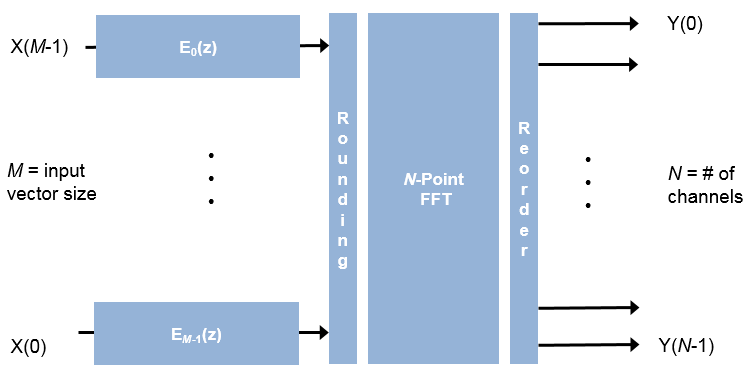

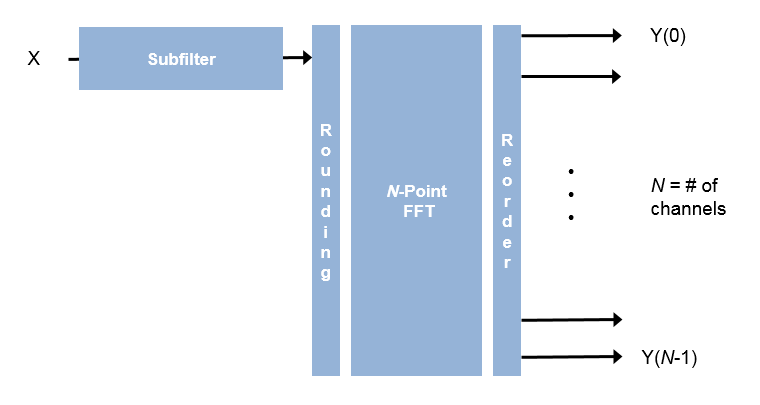

Блок Channelizer HDL Optimized разделяет широкополосный входной сигнал на несколько узкополосных выходных сигналов. Это обеспечивает аппаратную скорость и оптимизацию области для потоковой передачи применений данных. Блок принимает скалярный или векторный вход действительных или комплексных данных, обеспечивает благоприятные для оборудования управляющие сигналы и имеет дополнительные выходные сигналы управления кадром. Можно достигнуть пропускной способности выборки гига сэмплов в секунду (GSPS) с помощью векторного входа. Блок реализует многофазный фильтр с одним подфильтром на элемент входного вектора. Аппаратная реализация чередует подфильтры, который приводит к совместному использованию каждого множителя фильтра (FFT Length / Input Size) времена. Реализация БПФ использует то же конвейерное Основание 2^2 Алгоритм бпф как блок FFT HDL Optimized.

data — Входные данныеРазмер вектора должен быть степенью 2, который является от 1 до 64 и не больше количества каналов (длина БПФ).

double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Блок не принимает uint64 данные.

Типы данных: fixed point | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | single | double

Поддержка комплексного числа: Да

valid — Указывает на допустимые входные данныеКогда портом входа valid является true, блок получает значение на порте входа data.

Типы данных: Boolean

reset — Сбросьте (дополнительный) управляющий сигналКогда reset является true, блок останавливает текущее вычисление и очищает внутреннее состояние.

Чтобы включить этот порт, выберите Enable reset input port.

Типы данных: Boolean

data — Выходные данные канала частотыЕсли вы устанавливаете Output vector size на Same as number of frequency bands (значение по умолчанию), выходные данные являются 1 M вектором, где M является длиной БПФ.

Если вы устанавливаете Output vector size на Same as input size, выходными данными является M-by-1 вектор, где M является размером входного вектора.

Выходной порядок является битом, естественным для любого выходного размера. Тип выходных данных является результатом Filter output data type и роста разрядности в БПФ, необходимом, чтобы избежать переполнения.

valid — Указывает на допустимые выходные данныеБлок устанавливает порт выхода valid на true с каждой допустимой выборкой на порте выхода data.

Типы данных: Boolean

start — Указывает на первый допустимый цикл (дополнительных) выходных данныхБлок устанавливает start на true во время первой допустимой выборки на порте выхода data.

Чтобы включить этот порт, выберите Enable start output port.

Типы данных: Boolean

end — Указывает на последний допустимый цикл (дополнительных) выходных данныхБлок устанавливает end на true во время последней допустимой выборки на порте выхода data.

Чтобы включить этот порт, выберите Enable end output port.

Типы данных: Boolean

Number of frequency bands (FFT length) — Длина БПФДля генерации HDL-кода длина БПФ должна быть степенью 2 от 23 к 216.

Filter coefficients — Многофазные коэффициенты фильтраЕсли количество коэффициентов не является кратным Number of frequency bands (FFT length), блок заполняет этот вектор нулями. Спецификацией фильтра по умолчанию является КИХ-фильтр повышенного косинуса, rcosdesign(0.25,2,4,'sqrt'). Можно задать вектор из коэффициентов или вызова функции создания фильтра, которая возвращает содействующие значения. Комплексные коэффициенты не поддерживаются. По умолчанию блок приводит коэффициенты к совпадающему типу данных как вход.

Complex multiplication — Реализация HDL комплексных множителейUse 4 multipliers and 2 adders (значение по умолчанию) | Use 3 multipliers and 5 addersРеализация HDL комплексных множителей в виде любого 'Use 4 multipliers and 2 adders' или 'Use 3 multipliers and 5 adders'. В зависимости от вашего инструмента синтеза и целевого устройства, одна опция может быть быстрее или меньшей.

Эта опция применяется, только если вы используете Основание 2^2 архитектура.

Output vector size — Размер выходных данныхSame as number of frequency bands (значение по умолчанию) | Same as input sizeВыходные данные являются вектором-строкой из M-by-1 каналы. Выходной порядок является битом, естественным для любого выходного размера.

Same as number of frequency bands — Выходные данные являются 1 M вектором, где M является длиной БПФ.

Same as input size — Выходными данными является M-by-1 вектор, где M является размером входного вектора.

Divide butterfly outputs by two — Масштабирование БПФКогда вы выбираете этот параметр, БПФ реализует полный 1/N масштабный коэффициент путем масштабирования результата каждой настройки канала связи 2. Эта корректировка сохраняет выход БПФ в той же амплитудной области значений как ее вход. Если масштабирование отключено, БПФ избегает переполнения путем увеличения размера слова на 1 бит на каждом этапе.

Rounding mode — Округление метода используется для внутренних вычислений фиксированной точкиFloor (значение по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroСмотрите Округление Режимов. Блок использует вычисления с фиксированной точкой для внутренних вычислений, когда вход является любым целым числом или типом данных с фиксированной точкой. Эта опция не применяется, когда входом является single или double. Каждый этап БПФ раунды после вертеть факторного умножения, но перед бабочками. Округление может также произойти при приведении коэффициентов и выхода многофазного фильтра к типам данных, которые вы задаете.

Saturate on integer overflow — Обработка переполнения для внутренних вычислений фиксированной точкиСмотрите, что Переполнение Обрабатывает. Блок использует вычисления с фиксированной точкой для внутренних вычислений, когда вход является любым целым числом или типом данных с фиксированной точкой. Эта опция не применяется, когда входом является single или double. Эта опция применяется к приведению коэффициентов и выхода многофазного фильтра к типам данных, которые вы задаете.

Алгоритм бпф избегает переполнения любым масштабированием выхода каждого этапа (Normalize включенный), или путем увеличения размера слова 1 битом на каждом этапе (Normalize отключенный).

Coefficient data type — Тип данных коэффициентов фильтраInherit: Same word length as input (значение по умолчанию) | выражение типа данныхБлок приводит многофазные коэффициенты фильтра к этому типу данных, с помощью округления и настроек переполнения, которые вы задаете. Когда вы выбираете Inherit: Same word length as input (значение по умолчанию), блок выбирает двоичную точку с помощью fi() правила лучшей точности.

Filter output data type — Тип данных выхода многофазного фильтраInherit: Same word length as input (значение по умолчанию) | Inherit: via internal rule | выражение типа данныхБлок бросает выход многофазного фильтра (вход к БПФ) к этому типу данных, с помощью округления и настроек переполнения, которые вы задаете. Когда вы выбираете Inherit: Same word length as input (значение по умолчанию), блок выбирает двоичную точку лучшей точности путем рассмотрения значений коэффициентов фильтра и области значений типа входных данных.

По умолчанию логика БПФ не изменяет тип данных. Когда вы отключаете Divide butterfly outputs by two, БПФ увеличивает размер слова на 1 бит на каждом этапе, чтобы избежать переполнения.

Enable reset input port — Дополнительный сигнал сбросаКогда вы выбираете этот параметр, порт reset показывает на значке блока. Когда входом reset является true, блок останавливает вычисление и очищает все внутреннее состояние.

Enable start output port — Дополнительный управляющий сигнал, указывающий, запускается данныхКогда вы выбираете этот параметр, порт start показывает на значке блока. Сигнал start верен для первого цикла выходных данных в системе координат.

Enable end output port — Дополнительный конец указания управляющего сигнала данныхКогда вы выбираете этот параметр, порт end показывает на значке блока. Сигнал end верен для последнего цикла выходных данных в системе координат.

Многофазный алгоритм фильтра требует подфильтра для каждого канала БПФ. Для большего количества детали о многофазной архитектуре фильтра обратитесь к [1], и к странице с описанием блока Channelizer.

Примечание

Выход блока Channelizer HDL Optimized не совпадает с выходом от выборки для выборки блока Channelizer. Это несоответствие - то, потому что блоки применяют входные выборки к подфильтрам в различных порядках. Блок Channelizer HDL Optimized применяет вход X (0), чтобы подотфильтровать EM-1 (z), X (1), чтобы подотфильтровать EM-2 (z)..., X (M-1), чтобы подотфильтровать E0 (z). Каналы обнаруживаются обоими соответствиями блоков, когда анализируется по нескольким системам координат.

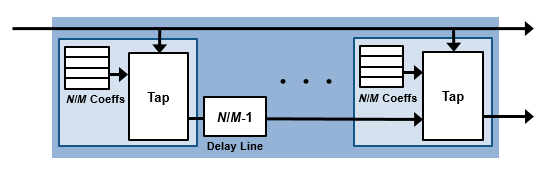

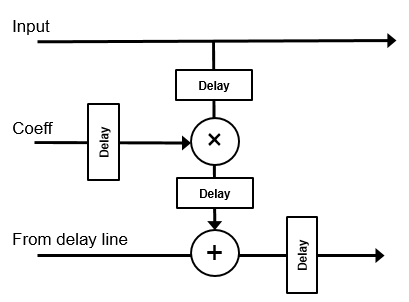

Если размер входного вектора, M, совпадает с длиной БПФ, N, то блок реализует N, подпросачивается оборудование. Каждый подфильтр является транспонированным КИХ-фильтром прямой формы с NumCoeffs/N касания.

Если размер вектора меньше N, блок реализует один подфильтр для каждого элемента входного вектора. Множители подфильтра совместно используются по мере необходимости, чтобы реализовать фильтры канала N. Разделяемые касания множителя имеют интерполяционную таблицу для N/M коэффициенты фильтра. Каждое касание сопровождается линией задержки N циклы/M–1.

Выход подфильтров брошен к заданному Filter output data type, с помощью округления и настроек переполнения, которые вы выбрали. Каждое касание фильтра в подфильтре является конвейерным, чтобы предназначаться для разделов DSP FPGA.

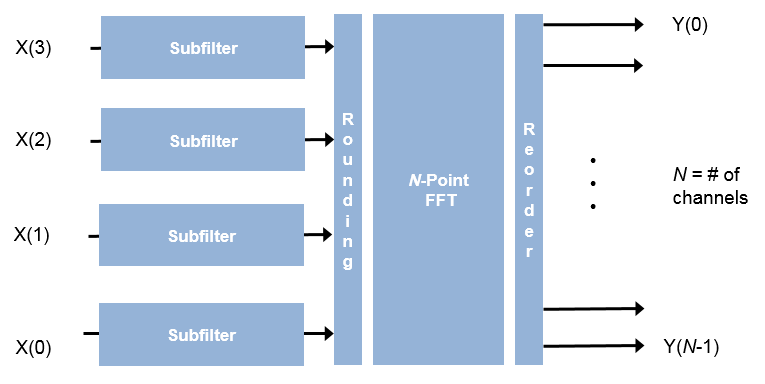

Например, для длины БПФ 8 и размера входного вектора 4, блок реализует четыре фильтра. Каждым множителем является совместно использованный N/M времена, или дважды. Каждое касание применяет два коэффициента, и линией задержки является N циклы/M–1.

Для скалярного входа блок реализует один фильтр. Каждый множитель является совместно использованными временами N. Каждое касание применяет коэффициенты N, и линией задержки является N –1 цикл.

Задержка меняется в зависимости от длины БПФ и размера вектора. После того, как вы обновите модель, задержка отображена на значке блока. Отображенная задержка является количеством циклов между первым допустимым входом и первым допустимым выходом, принимая, что вход непрерывен. Коэффициенты фильтра не влияют на задержку. Установка выходного размера, равного входному размеру, уменьшает задержку, потому что выборки не сохранены и переупорядочены.

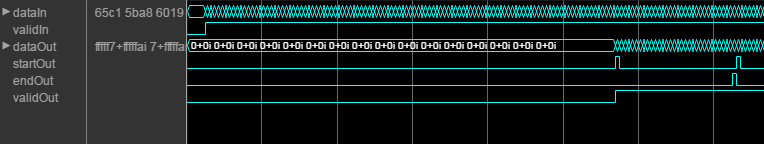

Эта схема показывает validIn и validOut сигналы для непрерывных входных данных с размером вектора 16 и длиной БПФ 512.

Схема также показывает дополнительный startOut и endOut сигналы, которые указывают на контуры системы координат. Когда включено, startOut импульсы для одного цикла с первым validOut из системы координат и endOut импульсы для одного цикла с последним validOut из системы координат.

Если вы применяете непрерывные входные кадры (никакой разрыв в validIn между системами координат), выход также будет непрерывен после начальной задержки.

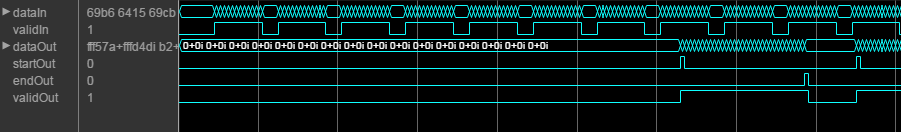

validIn сигнал может быть, состоящим из нескольких несмежных участков. Данные сопровождаются validIn сигнал хранится, пока система координат не заполнена. Затем данные выводятся в непрерывной системе координат N (длина БПФ) циклы. Эта схема показывает вход, состоящий из нескольких несмежных участков, и непрерывный выход для длины БПФ 512 и размера вектора 16 выборок.

Эти данные ресурсов и данные о производительности являются местом-и-маршрутом, следует из сгенерированного HDL, предназначенного к Xilinx® Virtex® 6 FPGA (XC6VLX240-1ff784). Эти три примера в таблицах используют эту настройку:

Длина БПФ (значение по умолчанию) — 8

Отфильтруйте длину — 96 коэффициентов

16-битные комплексные входные данные

Коэффициент и типы выходных данных фильтра (значение по умолчанию) — То же самое как количество диапазонов частот

Комплексное умножение (значение по умолчанию) — 4 множителя, 2 сумматора

Выведите масштабирование — Enabled

Минимизируйте часы, включает (параметр HDL Coder™)

Эффективность синтезируемого HDL-кода меняется в зависимости от вашей цели и опций синтеза.

Для скалярного входа проект достигает тактовой частоты 346 МГц. Задержка является 53 циклами. Подфильтры совместно используют каждый множитель восемь (N) времена. Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 1591 |

| FFS | 2681 |

Xilinx LogiCORE® DSP48 | 16 |

Для векторного входа с четырьмя выборками проект достигает тактовой частоты 333 МГц. Задержка является 31 циклом. Подфильтры совместно используют каждый множитель дважды (N/M). Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 1912 |

| FFS | 3986 |

Xilinx LogiCORE DSP48 | 56 |

Для векторного входа с восемью выборками проект достигает тактовой частоты 292 МГц. Задержка является 20 циклами. Когда входной размер совпадает с длиной БПФ, подфильтры не совместно используют множителей. Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 1388 |

| FFS | 2302 |

Xilinx LogiCORE DSP48 | 110 |

[1] Харрис, F. J. К. Дик и М. Райс. “Цифровые приемники и передатчики Используя многофазные наборы фильтров для радиосвязей”. Транзакции IEEE на микроволновой теории и методах. Издание 51, № 4, апрель 2003.

Этот блок поддерживает генерацию кода C/C++ для Simulink® акселератор и быстрые режимы Accelerator и для генерации компонента DPI.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.