Можно следовать этой инструкции как общей практике для моделирования проекта с различными блоками в Simulink® Браузер библиотеки.

Каждая инструкция имеет уровень серьезности, который указывает на уровень требований податливости. Чтобы узнать больше, смотрите Уровни серьезности Руководств по моделированию HDL.

1.1.8

Информативный

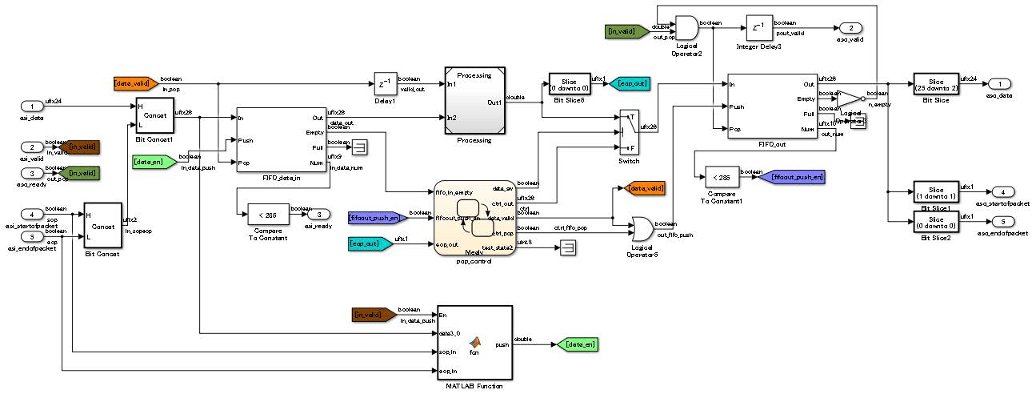

Когда вы создадите модель Simulink для генерации HDL-кода, используйте блоки Simulink, блоки MATLAB Function и Stateflow® блоки на основе приложения. Этот рисунок показывает пример того, как можно использовать различные блоки в DUT.

Используйте блоки Simulink, чтобы моделировать арифметические алгоритмы, которые выполняют числовую обработку, или содержит обратную связь.

Используйте блоки MATLAB Function, чтобы смоделировать управляющую логику, условные переходы такой как будто еще операторы и простая машина состояний. Можно также использовать блоки MATLAB Function, чтобы смоделировать IP, который записан с помощью MATLAB® код.

Используйте эти блоки Stateflow, чтобы смоделировать ваш алгоритм:

State Transition Table (Stateflow): Используйте эти блоки, чтобы смоделировать машину состояний, которая управляет выходом с помощью знания прошлого и настоящего.

Chart (Stateflow): Используйте эти блоки для блок-схем модели с помощью условного выражения, если еще ветви и машина состояний, которая управляет выходом с помощью знания прошлого и настоящего.

Truth Table (Stateflow): Используйте эти блоки для условного выражения модели если еще ветви.

Можно смоделировать комбинационную логику с помощью блоков Stateflow. Для более комплексных операций и операций, которые изменяют синхронизацию, такую как вставка трубопровода и обработка, используйте блоки Simulink. Можно затем использовать логику Stateflow, чтобы обработать результат, вычисленный от блоков Simulink

Для значительно больших алгоритмов, которые имеют комплексные расчеты, можно разделить проект в иерархию меньших проектов. Используйте это разделение для повторного использования, модульной разработки и ускоренной симуляции. Можно снова использовать модели включением их как блоки Model в топ-модели. Модель, которая снова использует этот блок, называется топ-моделью и блоком, который снова использован или включен в топ-модель, называется моделью, на которую ссылаются.

Примечание

Когда вы генерируете HDL-код для Subsystem, который не является в верхнем уровне модели, HDL Coder™ преобразует Subsystem в модель - ссылку.

Модель, на которую ссылаются, обработана похожая на Atomic Subsystem. В некоторых случаях алгебраический цикл может потенциально произойти и может предотвратить генерацию HDL-кода. Чтобы сгенерировать код, или удалить алгебраический цикл в вашем проекте, или, в диалоговом окне Configuration Parameters, задают установку Minimize algebraic loop occurrences.

Для подсистем, которые вы хотите симулировать в своем проекте и включать HDL-код, который вы создали, используйте подсистемы BlackBox. Чтобы создать Подсистему BlackBox, установите Архитектуру HDL Subsystem или Модели - ссылки к BlackBox. Можно использовать эту архитектуру, чтобы включить рукописный HDL-код в модель Simulink. Для получения дополнительной информации смотрите, Проверяют Комбинацию Рукописного и Сгенерированного HDL-кода (HDL Verifier).

Если вы генерируете модель Simulink с помощью HDL-кода, который вы создали, используйте импорт HDL. Чтобы узнать больше, смотрите Импорт Код Verilog и Сгенерируйте Модель Simulink.

Если у вас есть симулятор HDL, такой как Mentor Graphics® ModelSim® или острый тактовый сигнал®, можно использовать HDL Cosimulation (HDL Verifier) блоки, чтобы симулировать HDL-код для DUT и инстанцировать этого HDL-кода в сгенерированном коде.