Эти инструкции иллюстрируют рекомендуемые настройки при использовании Divide и блоков Product в вашей модели для улучшенной области и синхронизирующий на целевом FPGA. Каждая инструкция имеет уровень серьезности, который указывает на уровень требований податливости. Чтобы узнать больше, смотрите Уровни серьезности Руководств по моделированию HDL.

ID инструкции

2.7.1

Серьезность

Строго рекомендуемый

Описание

Алгоритмы цифровой обработки сигналов (DSP) используют несколько множителей и аккумуляторов. Устройства FPGA, обеспеченные поставщиками, такими как Xilinx® и Intel®, содержат выделенные срезы DSP. Они небольшой размер, высокая скорость, срезы DSP содержат несколько множителей и аккумуляторов, которые делают устройства FPGA подходящими лучше всего для приложений DSP.

Архитектура срезов DSP значительно различается через различных поставщиков FPGA и через различные семейства устройств, обеспеченных тем же поставщиком. Чтобы сопоставить вашу модель Simulink®, содержащую сумматоры, множители и задержки со срезами DSP, адаптируют вашу модель к секционной архитектуре DSP путем учета:

Расположение триггеров, сумматоров и множителей в срезе DSP.

Округление и настройки насыщения.

Битные ширины сумматоров и множителей. Для эффективного отображения используйте битные ширины в своей модели, которые меньше чем или равны битным ширинам модуля DSP.

Когда битные ширины в вашей модели становятся больше, чем битные ширины DSP, ваш проект не соответствует на один DSP. В этом случае несколько DSPS или дополнительная логика требуются.

Можно сопоставить эти блоки в модели с блоками DSP на FPGA:

Добавьте и суммируйте

Задержка

Продукт

Умножьтесь - Добавляют

Умножьтесь - Накапливаются

Этот рисунок иллюстрирует архитектуру DSP Xilinx. Серии FPGAs Xilinx 7 выделили срезы DSP, которые используют эту архитектуру. Архитектура DSP состоит из входных регистров, предварительного сумматора, 25x18 множитель, промежуточные регистры, постсумматор и выходной регистр.

Для получения дополнительной информации см. Обзор Среза DSP48E1 в документации Xilinx.

Этот рисунок иллюстрирует архитектуру DSP Intel. Эта архитектура DSP для устройств Stratix® V является переменной архитектурой DSP точности. Блоки DSP могут иметь битные ширины 9, 18, 27, и 36 битов, и 18x25 комплексное умножение для БПФ.

Для получения дополнительной информации смотрите Архитектуру Блока DSP в документации Intel.

Чтобы изучить, как можно спроектировать алгоритм, чтобы сопоставить с этим модулем DSP, откройте модель hdlcoder_multiplier_adder_dsp.slx

open_system('hdlcoder_multiplier_adder_dsp') set_param('hdlcoder_multiplier_adder_dsp', 'SimulationCommand', 'Update')

Модель состоит из двух подсистем dsp_subsys1 и dsp_subsys2, которые реализуют операцию C + (A+D) *B. Можно также реализовать эту операцию при помощи, Умножаются - Добавляют или Умножаются - Накапливают блоки, как проиллюстрировано подсистемами DSP_MultAdd и DSP_MultAcc.

dsp_subsys1 реализует операцию C + (A+D) *B при помощи битных ширин, которые равняются DSP на серии FPGA Xilinx 7. Если вы открываете HDL Workflow Advisor и развертываете эту Подсистему на Virtex® 7 FPGA Xilinx, целый проект соответствует точно на один срез DSP.

dsp_subsys2 реализует ту же операцию при помощи битных ширин, которые больше, чем DSP на FPGA Xilinx. Если вы развертываете эту Подсистему на FPGA Xilinx Virtex 7, вы видите, что целые подгонки проекта на один срез DSP и используют дополнительную логику среза.

auto для блока Gain2.7.2

Строго рекомендуемый

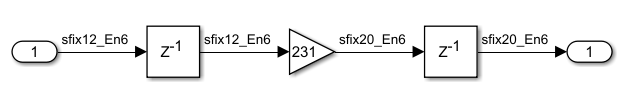

Когда вы будете использовать блок Gain в своем проекте, чтобы достигнуть большей части эффективного внедрения области, установите свойство блока ConstMultiplierOptimization HDL на auto. Генератор кода выбирает между CSD и FCSD реализации, который дает к самому маленькому размеру схемы и генерирует HDL-код, не используя умножение (*) оператор.

Можно использовать эту установку, чтобы не предназначаться для ресурсов DSP и сокращать количество логических схем на Intel® Куарт® Главный при синтезировании проекта на целевом FPGA. Например, эта таблица показывает сгенерированный HDL-код для блока Gain в зависимости от настроек свойства блока HDL для блока ConstMultiplierOptimization.

Настройки ConstMultiplierOptimization и удар на сгенерированный HDL-код

ConstMultiplierOptimization Установка | Операции | Сгенерированный HDL-код |

|---|---|---|

CSD | Входные данные бросков параллельно и добавляют, или вычтите результаты.

| Этот код показывает сгенерированный код VHDL. -- CSD Encoding(231): 1001'01001'; Cost (Adders) = 3 DOUT_mul_temp <= ((resize(DIN & '0' & '0' & '0' & '0' & '0' & '0' & '0' & '0', 21) - resize(DIN & '0' & '0' & '0' & '0' & '0', 21)) + resize(DIN & '0' & '0' & '0', 21)) - resize(DIN, 21); DOUT <= DOUT_mul_temp(19 DOWNTO 0); Этот код показывает сгенерированный код Verilog.

// CSD Encoding (231) : 1001'01001'; Cost (Adders) = 3

assign Gain_1 = {DIN[11], {DIN, 8'b00000000}};

assign Gain_2 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_3 = {{6{DIN[11]}}, {DIN, 3'b000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign DOUT_mul_temp = ((Gain_1 - Gain_2) + Gain_3) - Gain_4;

assign DOUT = DOUT_mul_temp[19:0];

|

FCSD | Добавляют входные данные и его данные броска в каждом расположении каскадом.

| Этот код показывает сгенерированный код VHDL. -- FCSD for 231 = 33 X 7; Total Cost = 2 -- CSD Encoding (33) : 0100001; Cost (Adders) = 1 Gain_factor <= resize(DIN & '0' & '0' & '0' & '0' & '0', 21) + resize(DIN, 21); -- CSD Encoding (7) : 1001'; Cost (Adders) = 1 DOUT_mul_temp <= resize(Gain_factor & '0' & '0' & '0', 21) - Gain_factor; DOUT <= DOUT_mul_temp(19 DOWNTO 0); Этот код показывает сгенерированный код Verilog.

// FCSD for 231 = 33 X 7; Total Cost = 2

// CSD Encoding (33) : 0100001; Cost (Adders) = 1

assign Gain_3 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign Gain_factor = Gain_3 + Gain_4;

// CSD Encoding (7) : 1001'; Cost (Adders) = 1

assign Gain_1 = {Gain_factor, 3'b000};

assign Gain_2 = Gain_1[20:0];

assign DOUT_mul_temp = Gain_2 - Gain_factor;

assign DOUT = DOUT_mul_temp[19:0];

|

auto | Выбирает CSD или реализацию FCSD, которая использует меньше сумматоров. | Сгенерированный HDL-код - то же самое как CSD или реализация FCSD. |

none | Оператор умножения использования (*). | Этот код показывает сгенерированный код VHDL. DOUT_mul_temp <= to_signed(2#011100111#, 9) * DIN; DOUT <= DOUT_mul_temp(19 DOWNTO 0); Этот код показывает сгенерированный код Verilog. assign DOUT_mul_temp = 231 * DIN; assign DOUT = DOUT_mul_temp[19:0]; |

ShiftAdd Архитектура блока Divide для фиксированных точек2.7.3

Рекомендуемый

Когда вы используете типы данных с фиксированной точкой в качестве входных параметров с блоком Divide, задаете Архитектуру HDL блока как ShiftAdd и затем набор свойство UsePipelines блока HDL к on. В этой архитектуре блок вычисляет результат при помощи нескольких, переключают и добавляют операции. Операции являются конвейерными, чтобы достигнуть более высоких тактовых частот на целевом устройстве FPGA.

Когда вы используете типы данных с плавающей точкой в качестве входных параметров с блоком Divide, оставляете Архитектуру HDL значению по умолчанию Linear и набор Библиотека IP С плавающей точкой к Native Floating Point.