Сгенерируйте контрольную сумму и добавьте, чтобы ввести демонстрационный поток

Wireless HDL Toolbox / Выявление ошибок и Коррекция

Блок LTE CRC Encoder вычисляет и добавляет контрольную сумму контроля циклическим избыточным кодом (CRC) для каждой системы координат потоковой передачи выборок данных. Можно выбрать из полиномов, заданных TS 36.212 [1] стандарта LTE. Блок обеспечивает аппаратную оптимизированную архитектуру и интерфейс.

Этот блок использует демонстрационный интерфейс потоковой передачи с шиной для связанных управляющих сигналов. Этот интерфейс позволяет блоку действовать независимо от формата кадра и соединиться легко с другими блоками Wireless HDL Toolbox™. Блок принимает и возвращает значение, представляющее одну выборку и шину, содержащую три управляющих сигнала. Эти сигналы указывают на валидность каждой выборки и контуры системы координат. Чтобы преобразовать матрицу в демонстрационный поток и эти управляющие сигналы, используйте блок Frame To Samples или whdlFramesToSamples функция. Для полного описания интерфейса смотрите Демонстрационный Интерфейс Потоковой передачи.

Вы не должны применять другую систему координат, прежде чем предыдущая система координат завершилась. Благоприятный для оборудования алгоритм добавляет (CRCLength + 3)/InputSize циклы задержки. С учетом дополнительных циклов добавленных выборок контрольной суммы и задержки, необходимо применить минимальный интервал (2*CRCLength + 3)/InputSize между входными кадрами. В качестве альтернативы можно использовать выходной сигнал ctrl.end определить, когда блок готов к новому входу. Если вы применяете следующую систему координат слишком рано, ctrl.start предупредите сбрасывает вычисление контрольной суммы и обрезает предыдущую систему координат.

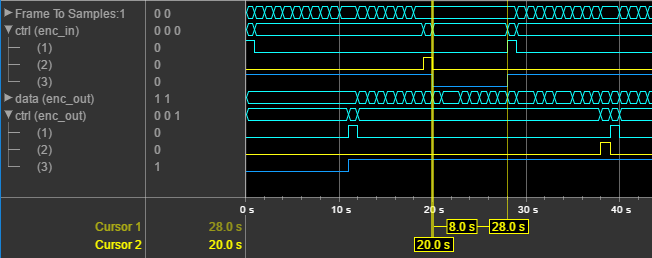

Эта форма волны показывает систему координат с 40 выборками, введите две выборки за один раз к энкодеру CRC16. Разрыв между входными кадрами является поэтому 8 циклами. Из-за вставки контрольной суммы, выход ctrl.valid сигнал остается постоянно высоким без разрывов между системами координат. Ввод и вывод шины ctrl расширен, чтобы показать управляющие сигналы. start и end покажите контуры системы координат и valid квалифицирует выборки данных.

[1] 3GPP TS 36.212. "Мультиплексирование и кодирование канала". Проект Партнерства третьего поколения; Сеть радиодоступа Technical Specification Group; Развитый Универсальный Наземный Радио-доступ (к E-UTRA). URL: https://www.3gpp.org.

[2] Кампобелло, Джузеппе, Джузеппе Патане и Марко Руссо. "Параллельная Реализация CRC". Транзакции IEEE на Компьютерах. Издание 52, № 10, октябрь 2003, стр 1312–1319.