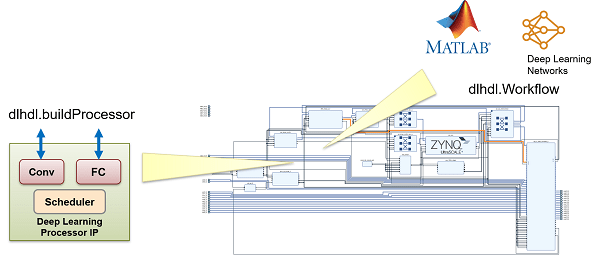

Можно интегрировать ядро процессора IP глубокого обучения в систему:

Генерация и интеграция Ядра IP Процессора DL — Генерируют типовое ядро процессора IP глубокого обучения при помощи Deep Learning HDL Toolbox. Сгенерированное ядро процессора IP глубокого обучения является типовым ядром IP HDL Coder со стандартными интерфейсами AXI4. Можно интегрировать сгенерированное типовое ядро IP DL в вас Vivado® или Куарт® проект.

Ускорьте интегрирование сгенерированного ядра IP процессора DL в вашу разработку системы:

Чтение AXI4 указывает карты в сгенерированном отчете ядра IP. Регистры AXI4 позволяют MATLAB® или другие Ведущие устройства AXI4, чтобы управлять и программировать ядро IP процессора DL.

Используя компилятор сгенерировал распределение буферов внешней памяти.

Форматирование данных о внешней памяти ввода и вывода.

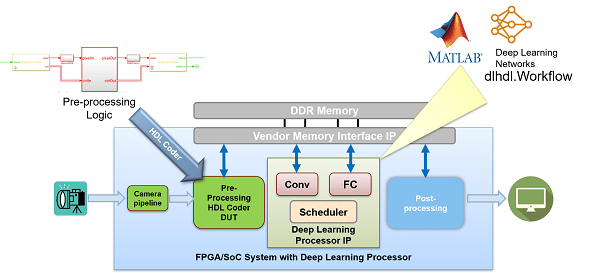

Исходный проект базирующееся интегрирование ядра IP Процессора DL — Генерирует типовое ядро процессора IP глубокого обучения при помощи Deep Learning HDL Toolbox. Интегрируйте сгенерированное ядро процессора IP глубокого обучения в свой пользовательский исходный проект при помощи HDL Coder. Смотрите Пользовательский Исходный проект (HDL Coder). Можно спроектировать предварительную обработку и сообщение, обрабатывающее логику DUT в Simulink® или MATLAB и использование рабочий процесс генерации ядра IP HDL Coder, чтобы интегрировать логику предварительной обработки и последующей обработки с процессором глубокого обучения.

Используйте MATLAB, чтобы запуститься, ваша пользовательская нейронная сеть для глубокого обучения на ядре процессора IP глубокого обучения и получать предсказание нейронной сети для глубокого обучения следует из вас проект интегрированной системы.

Ядро IP процессора глубокого обучения

Узнайте о сгенерированном ядре процессора IP глубокого обучения.

Используйте выход компилятора для системной интеграции

Используйте выходы компилятора, чтобы интегрировать сгенерированное ядро процессора IP глубокого обучения в вас проект.

Задайте формат данных внешней памяти ввода и вывода.

Карта регистра процессора глубокого обучения

Используйте MATLAB или другие ведущие устройства AXI4, чтобы управлять и программировать ядро процессора IP глубокого обучения.

Интерфейс с ядром IP процессора глубокого обучения

Примите решение между режимом пакетной обработки данных и потоковым режимом обработать несколько кадров данных.

В этом примере показано, как задать и указать пользовательскую плату и исходный проект для рабочего процесса ядра процессора IP глубокого обучения.