SoC Blockset™ включает симуляцию и оценку транзакций памяти в Simulink® без потребности развернуть модель в устройство SoC. Используйте эту диагностическую информацию, чтобы анализировать эффективность ваших моделей и настроить по мере необходимости, чтобы удовлетворить желаемые требования производительности системы. Симуляция генерирует два типа визуализации трафика памяти:

Графики Эффективности симуляции – Обеспечивают диагностику эффективности высокого уровня системы памяти модели. Полоса пропускания памяти, пакетные количества и задержки транзакции вычисляются от симуляции вашей модели. Можно просмотреть эту информацию для каждого ведущего устройства памяти в модели или полное представление от контроллера памяти.

Буферизуйте и Пакетные Формы волны – Обеспечивает пакетную отладочную информацию транзакции от симуляции, включая использование буферных областей.

Можно также получить фактическую полосу пропускания, количество пакетов и измерения задержки из проекта, работающего на FPGA, и просмотреть информацию об отдельных пакетных транзакциях. Эта информация получена включением IP AXI interconnect monitor в проекте FPGA и запроса данных по ведущей связи JTAG AXI от хоста. Смотрите информацию об Эффективности Памяти от Выполнения FPGA.

SoC Blockset позволяет регистрировать сигналы симуляции и визуализировать регистрируемые сигналы с помощью Logic Analyzer. Включить логгирование сигнала, Набор Memory diagnostics level к Basic diagnostic signals в параметрах конфигурации модели, под Hardware Implementation> Target hardware resources> FPGA design (debug).

После симуляции вашей модели найдите Logic Analyzer наверху своего окна Simulink.

Инструмент Logic Analyzer обеспечивает визуализацию форм волны сигнала, чтобы показать синхронизацию различных событий модели памяти.

Logic Analyzer отображает сигналы от Memory Controller и от блоков Memory Channel.

Разорвите формы волны

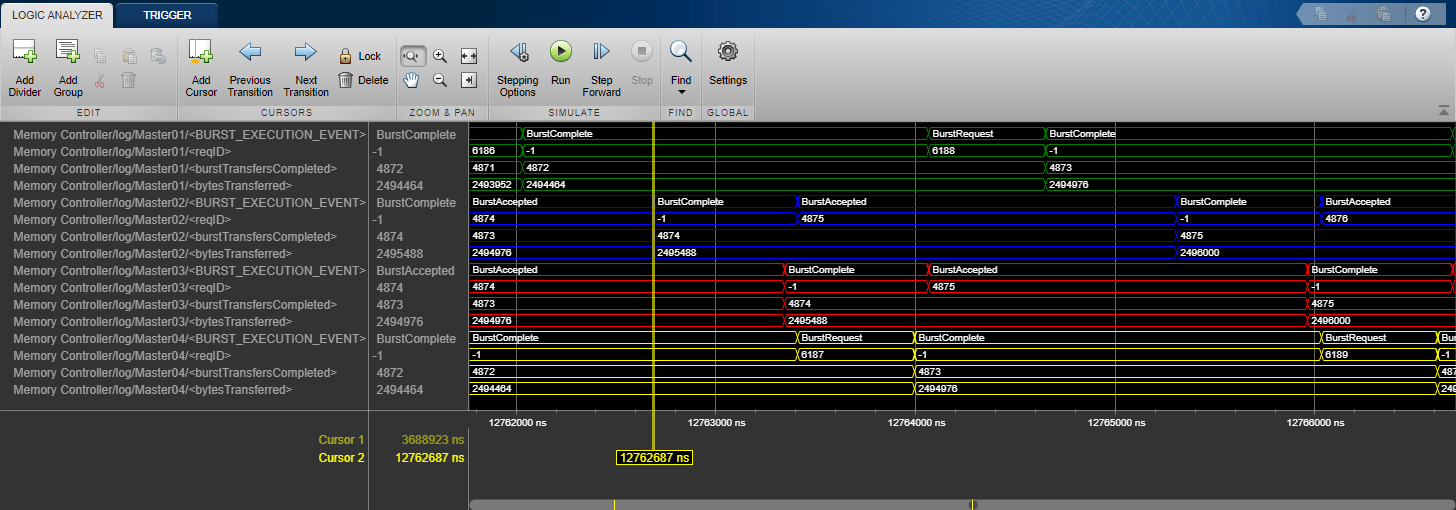

Формы волны от контроллера памяти включают информацию для пакетов от ведущих устройств в системе. Формы волны являются цветом, закодированным, чтобы дифференцировать различные ведущие устройства. Эти формы волны дают понимание секвенирования каждого из ведущих устройств через общую память. Для каждого ведущего устройства просмотрите следующие сигналы:

BURST_EXECUTION_EVENT: Состояние текущего пакетного запроса. Допустимые состояния: ни одно (неактивное), запрос, выполнение, сделанное. Для получения дополнительной информации о состоянии контроллера памяти, смотрите Memory Controller.

ReqID: Идентификатор текущего пакетного запроса. Постепенно увеличивающийся номер, который уникален в течение симуляции.

burstTransfersCompleted: Рабочее количество переданных пакетов. Если никакие пакеты не уронены в канале памяти, количество переданных пакетов совпадает с ReqID. Если пакеты уронены, ReqID становится больше, чем это количество.

BytesTransferred: Рабочее количество переданных байтов.

Следующий рисунок показывает сигналы после того, как симуляция Будет Анализировать Полосу пропускания Памяти Используя Генераторы Трафика.

Формы волны включают информацию о пакете для этих четырех ведущих устройств, отображенных в различных цветах. Эта информация коррелирует к Графикам Задержки Контроллера памяти.

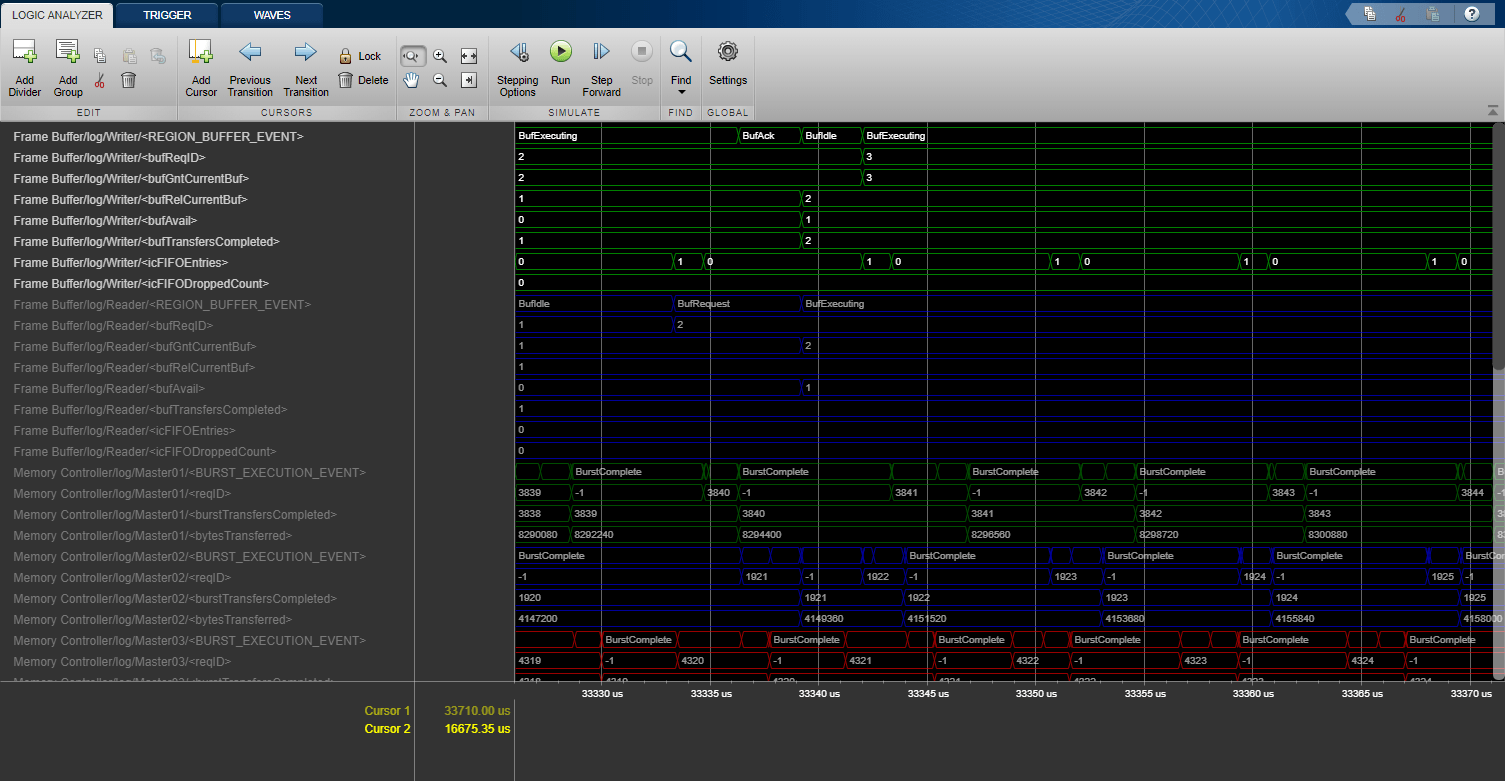

Буферные формы волны

Формы волны от канала памяти включают информацию для буферного чтения и транзакций записи в канале. Каждая область памяти разделена на несколько буферов, заданных параметром Number of buffers блока Memory Channel. Средство записи заполняет буферы, и читатель опорожняет их. Эти формы волны дают понимание секвенирования средства записи и читателя для данной области. Буферные формы волны включают следующие сигналы:

REGION_BUFFER_EVENT: Состояние текущего буферного запроса. Допустимые состояния: ни одно (неактивное), запрос, выполнение, сделанное. Для получения дополнительной информации о состоянии канала памяти, смотрите Memory Channel.

BufReqID: Идентификатор текущего буферного запроса. Постепенно увеличивающийся номер, который уникален в течение симуляции.

BufferAddress: Смещение начального адреса текущего буфера. Буферный адрес повторяется как циклы симуляции через буферы, отражая контуры адреса буферов.

BufGntCurrentBuf: В настоящее время активный буфер, заданный от 1 до количества буферов в канале. BufGntCurrentBuf точки к буферу, записанному в (на стороне средства записи) или буферу, считанному из (на стороне читателя).

BufRelCurrentBuf: Буфер в настоящее время выпущен читателем или средством записи, заданным от 1 до количества буферов в канале. На стороне читателя, когда буфер выпущен, это доступно для средства записи для записи. На стороне средства записи, когда буфер выпущен, это доступно для читателя для чтения.

BufAvail: Количество буферов, в настоящее время доступных для читателя для чтения. Это значение идентично на читателе и стороне средства записи.

BufTransfersCompleted: Рабочее количество переданных буферов. Если никакие буферы не пропущены в области памяти, количество переданных буферов совпадает с BufReqID. Если буферы пропущены, BufReqID больше, чем это количество.

icFIFOEntries: Количество пакетов записано во взаимосвязанный FIFO.

icFIFODroppedCount: Количество пакетов исключено из взаимосвязанного FIFO.

Следующий рисунок показывает буферные сигналы после симуляции Эквализации Гистограммы Используя Буфер Видеокадра.

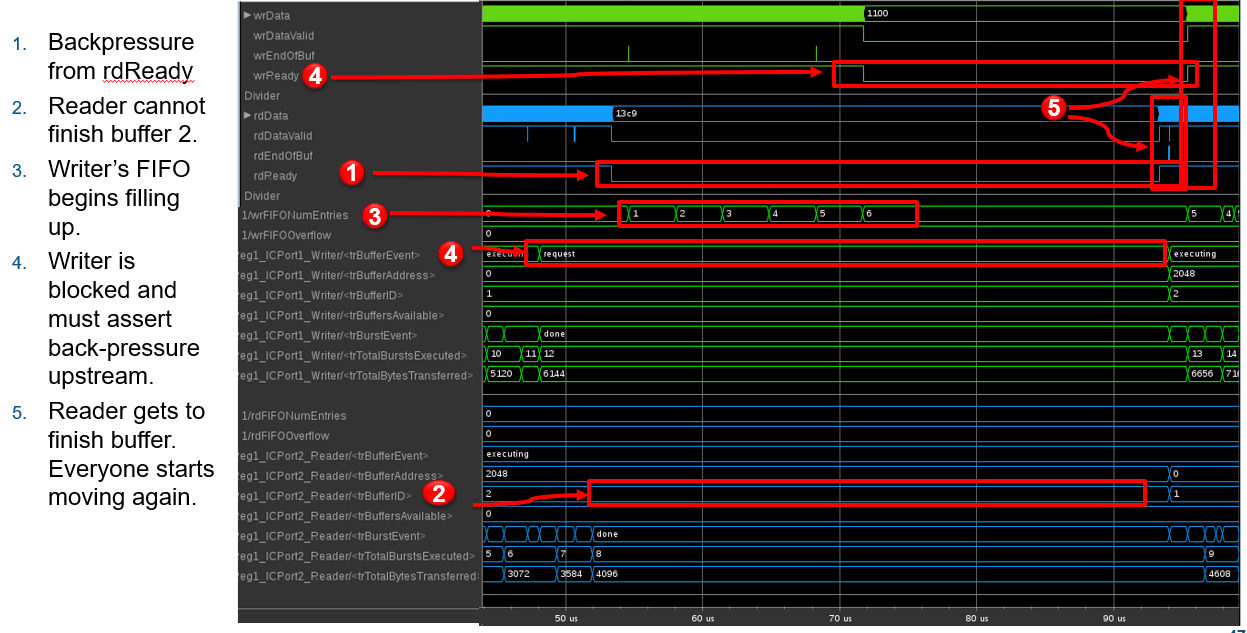

Можно связать операцию модели памяти с интерфейсом протокола, чтобы изучить эффективность модели. Следующий рисунок показывает, как связать операцию модели памяти с интерфейсом протокола.

Logic Analyzer | Memory Channel | Memory Controller