Декодируйте convolutionally закодированные данные с помощью алгоритма Viterbi

Wireless HDL Toolbox / Выявление ошибок и Коррекция

Блок Viterbi Decoder декодирует convolutionally закодированные данные с помощью основанной на RAM traceback реализации. Декодирование Viterbi широко используется в TS 36.212 [1] стандарта LTE и других приложениях прямого исправления ошибок (FEC), таких как беспроводные сети (802.11a/b/g/n/ac), цифровая спутниковая связь, цифровое видео широковещательно передается (DVB), IEEE 802.16 и HiperLAN. Чтобы поддержать любой из этих стандартов, блок принимает коды свертки с продолжительностями ограничения 3 - 9, скорости кода 1/2 к 1/7, и обеспечивает непрерывные, отключенные, и усеченные режимы. Блок обеспечивает архитектуру и интерфейс, подходящий для генерации HDL-кода.

Декодирование поддержек блока проколотых кодов путем обеспечения дополнительного входного порта erasure. Можно использовать блок Depuncturer, чтобы вставить нейтральные значения в проколотый демонстрационный поток и сгенерировать сигнал erasure.

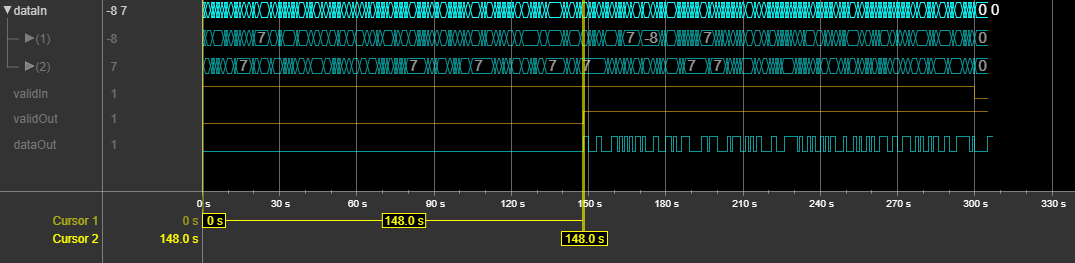

Блок Viterbi Decoder принимает входные выборки как двоичные значения трудного решения или логарифмические отношения правдоподобия (LLR) мягкого решения. Каждая выборка является вектор-столбцом, длина которого зависит от схемы кодирования. Первая форма волны показывает непрерывный режим работы с входными выборками 4-битных данных со знаком, с помощью параметров блоков по умолчанию. Traceback depth является 32. Блок возвращает первую декодируемую выборку выходных данных после 148 тактов. Задержка декодирования 4×Traceback depth + Constraint length + 13 допустимых входных циклов.

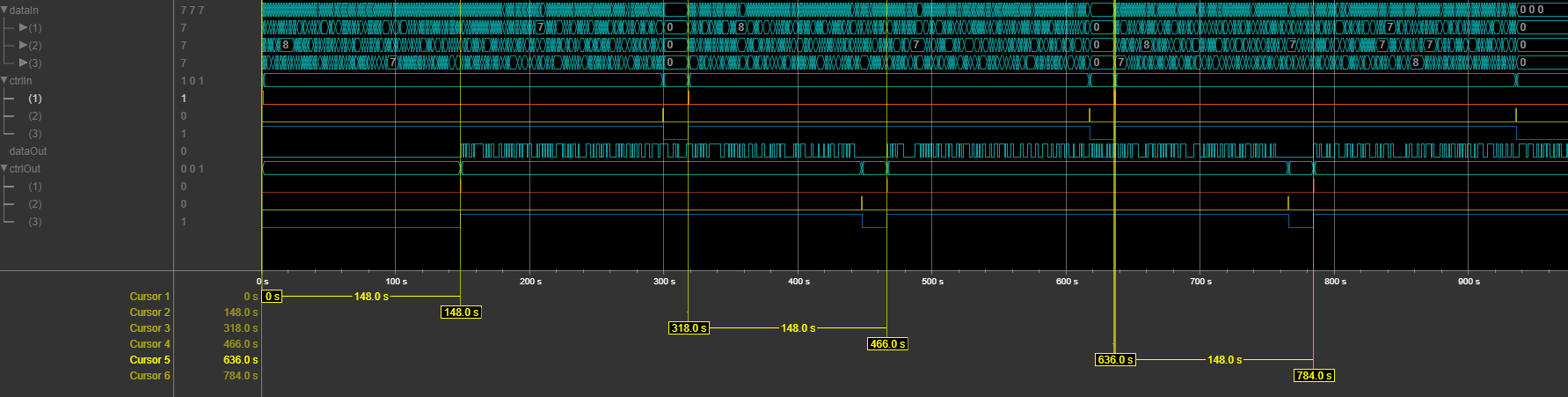

Вторая форма волны показывает три системы координат в отключенном режиме работы. Вход является 4-битными выборками без знака, и блок использует решетку (7, [171 133 112]). Traceback depth является 32. Ввод и вывод шины ctrl расширен, чтобы показать их три управляющих сигнала. Задержка от каждого входа ctrl.start к выходу ctrl.start также 148 тактов.

Управляющие сигналы в шине указывают на валидность каждой выборки и контуры системы координат. Чтобы преобразовать матрицу в демонстрационный поток и соответствующие управляющие сигналы, используйте блок Frame To Samples или whdlFramesToSamples функция. Для полного описания демонстрационного интерфейса потоковой передачи смотрите Демонстрационный Интерфейс Потоковой передачи.

[1] 3GPP TS 36.212. "Мультиплексирование и кодирование канала". Проект Партнерства третьего поколения; Сеть радиодоступа Technical Specification Group; Развитый Универсальный Наземный Радио-доступ (к E-UTRA). URL: https://www.3gpp.org.

[2] Horwitz, M. и Р. Браун. "Обобщенный метод проектирования для управления памятью оставшегося в живых Traceback в декодерах Витерби". Продолжения 1 997 южноафриканских симпозиумов по коммуникациям и обработке сигналов: 63-68. Пискатауэй, NJ: IEEE, 1997.

[3] Shung, C.b., P.h. Зигель, Г. Анджербоек и H.k. Thapar. "Архитектуры VLSI для Метрической Нормализации в алгоритме Viterbi". Международная конференция IEEE по вопросам Коммуникаций, Включая Суперкомма Текникэла Сешнза: vol 4. 1726-728. Нью-Йорк, Нью-Йорк: IEEE, 1990.