Вычислите значение и/или угол фазы комплексного сигнала — оптимизированный для генерации HDL-кода с помощью алгоритма CORDIC

Математические операции

dspmathops

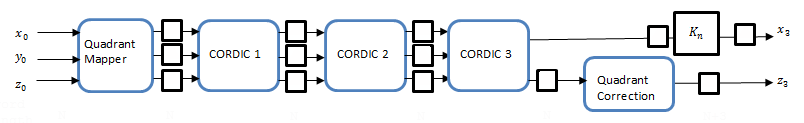

Блок Complex to Magnitude-Angle HDL Optimized вычисляет значение и/или угол фазы комплексного сигнала. Это обеспечивает благоприятные для оборудования управляющие сигналы. Блок использует конвейерный Координатный Компьютер Вращения (CORDIC) алгоритм, чтобы достигнуть эффективной реализации HDL.

Можно также использовать этот блок, чтобы реализовать функцию atan2 в оборудовании.

| Порт | Направление | Описание | Тип данных |

|---|---|---|---|

dataIn | Входной параметр | Объедините скалярный входной сигнал. |

|

validIn | Входной параметр | Указывает, что входной сигнал допустим. Когда validIn высок, блок получает значение dataIn. | boolean |

magnitude | Вывод | Скалярный выходной сигнал. | То же самое как dataIn |

angle | Вывод | Скалярный выходной сигнал. Дополнительный. | То же самое как dataIn |

validOut | Вывод | Указывает, что выходной сигнал допустим. Когда magnitude или angle, вывод готов, блок, устанавливает validOut высоко. | boolean |

Задает источник Number of iterations для алгоритма CORDIC. Выберите Auto, чтобы определить номер итераций к входному размеру слова − 1. Если входом является double или single, Auto определяет номер итераций к 16. Выберите Property, чтобы определить номер итераций от Number of iterations. Значением по умолчанию является Auto.

Задает количество итераций CORDIC, которые выполняет блок. Этот параметр видим только, когда Number of iterations source установлен в Property. Количество итераций должно быть меньше чем или равно размеру слова − 1 входных данных.

Задержка блока зависит от количества выполняемых итераций. Смотрите Задержку.

Задает, какие выходные порты активны. Можно выбрать Magnitude, Angle или Magnitude and angle. Значением по умолчанию является Magnitude and angle.

Задает формат angle вывод. Можно выбрать Normalized или Radians. Выберите Normalized, чтобы возвратить выходной параметр в формате фиксированной точки, который нормирует углы в области значений [–1,1]. Для получения дополнительной информации смотрите Нормированный Угловой Формат. Выберите Radians, чтобы возвратить выходной параметр как значение фиксированной точки между π и −π. Форматом по умолчанию является Normalized.

При использовании этого блока, чтобы реализовать функцию atan2, установите этот параметр на Radians.

Шкалы, выведенные инверсией CORDIC, получают фактор. Значение по умолчанию выбрано.

Если вы выключаете выходное масштабирование и применяете усиление CORDIC в другом месте в вашем проекте, необходимо исключить термин π/4. Квадрант, сопоставляющий алгоритм, заменяет первую итерацию CORDIC путем отображения входных параметров на угловую область значений [0, π/4]. Поэтому начальное вращение не вносит термин усиления.

Если вход является 0+0i, выходной угол не определен. Блок не реализует логику исправления, чтобы обеспечить вывод к 0. Можно проигнорировать этот выходной угол.

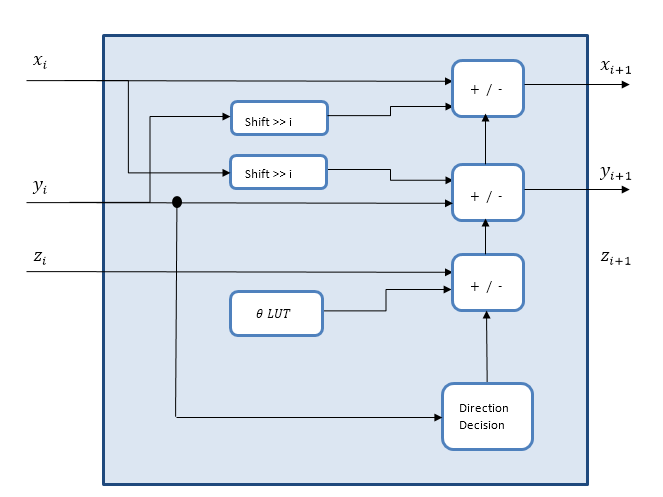

Алгоритм CORDIC является благоприятным для оборудования методом для выполнения тригонометрических функций. Это - итеративный алгоритм, который аппроксимирует решение путем схождения к идеальной точке. Блок использует CORDIC векторизация режима, чтобы итеративно вращать вход на вещественную ось.

Метод Givens для вращения комплексного числа x+iy углом θ следующие. Направление вращения, d, +1 для против часовой стрелки и −1 для по часовой стрелке.

Для аппаратной реализации факторизуйте becauseθ, чтобы оставить термин tanθ.

Чтобы вращать вектор на вещественную ось, выберите ряд вращений θn так, чтобы . Удалите термин becauseθ, таким образом, каждое итеративное вращение использует только сдвиг, и добавьте операции.

Объедините отсутствие условия becauseθ от каждой итерации в константу, и примените его с одним множителем к результату итогового вращения. Выходное значение является масштабированным окончательным значением x. Выходной угол, z, является суммой углов поворота.

Область сходимости для стандартного вращения CORDIC составляет ≈ ±99.7 °. Работать вокруг этого ограничения, прежде, чем сделать любое вращение, блок-диаграммы вход в [0, π/4] область значений с помощью следующего алгоритма.

if abs(x) > abs(y) input_mapped = [abs(x), abs(y)]; else input_mapped = [abs(y), abs(x)]; end

Квадрантное отображение сохраняет аппаратные ресурсы и уменьшает задержку путем сокращения количества настроек канала связи CORDIC одной. Фактор усиления CORDIC, Kn, поэтому не включает n=0, или потому что (π/4), называют.

После того, как итерации CORDIC завершены, блок исправляет угол назад к его исходному местоположению. Сначала это настраивает угол правильной стороне π/4.

if abs(x) > abs(y) angle_unmapped = CORDIC_out; else angle_unmapped = (pi/2) - CORDIC_out; end

if (x < 0)

if (y < 0)

output_angle = - pi + angle_unmapped;

else

output_angle = pi - angle_unmapped;

else

if (y<0)

output_angle = -angle_unmapped;

Блок генерирует конвейерную архитектуру HDL, чтобы максимизировать пропускную способность. Каждая итерация CORDIC сделана в одной настройке канала связи. Множитель усиления, если включено, реализован с логикой Канонической цифры со знаком (CSD).

| Введите размер слова | Выведите размер слова значения |

|---|---|

| fixdt (0, WL, FL) | fixdt (0, WL+2, FL) |

| fixdt (1, WL, FL) | fixdt (1, WL+1, FL) |

| Введите размер слова | Выведите угловой размер слова | |

|---|---|---|

| fixdt ([], WL, FL) | Радианы | fixdt (1, WL+3, WL) |

| 'normalized' | fixdt (1, WL+3, WL+2) | |

Логика CORDIC при каждой настройке канала связи реализует одну итерацию. Для каждой настройки канала связи сдвиг и угловое вращение являются константами.

Когда вы устанавливаете Output format на Magnitude, блок не генерирует HDL-код для углового накопления и квадрантной логики исправления.

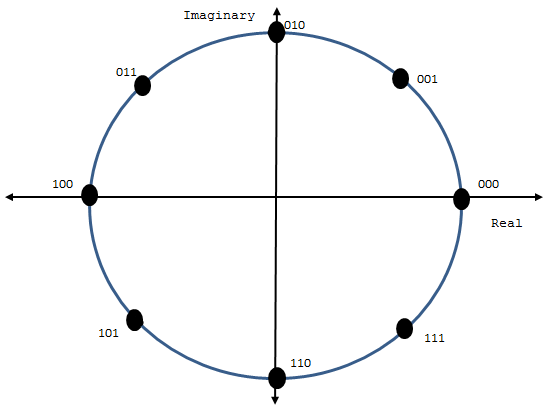

Этот формат нормирует угловые значения радиана фиксированной точки вокруг модульного круга. Это - более эффективное использование битов, чем область значений [0,2π] радианы. Нормированный угловой формат также включает перенос в 0/2π без дополнительного, обнаруживают и исправляют логику.

Например, представляя угол с результатами на 3 бита в следующих нормированных значениях.

Используя отображение, описанное в Измененном Алгоритме CORDIC, блок нормирует углы через [0, π/4] и сопоставляет их с правильным октантом в конце вычисления.

Выводом является допустимый Number of iterations + 4 цикла после допустимого входа.

Когда вы устанавливаете Number of iterations source на Property, блок сразу показывает задержку. Когда вы устанавливаете Number of iterations source на Auto, блок вычисляет задержку на основе типа данных входного порта и отображает его, когда вы обновляете модель.

![]()

Когда вы устанавливаете Number of iterations source на Auto, количество итераций является входным размером слова − 1, и задержка является входным размером слова + 3. Если входом является double или тип single, количество итераций равняется 16, и задержка равняется 20.

Уровень был измерен для настройки по умолчанию с выходным отключенным масштабированием и вход fixdt(1,16,12). Когда сгенерированный HDL-код синтезируется в Xilinx® Virtex®-6 (XC6VLX240T-1FFG1156) FPGA, проект достигает частоты часов на 260 МГц. Это использует следующие ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 882 |

| FFS | 792 |

Xilinx LogiCORE® DSP48 | 0 |

| Блокируйте RAM (16K) | 0 |

Производительность синтезируемого HDL-кода отличается в зависимости от вашей цели и опций синтеза.

Комплекс к углу значения | atan2 | dsp.HDLComplexToMagnitudeAngle