Используя HDL Workflow Advisor, можно сгенерировать пользовательское ядро IP из модели или алгоритма. Сгенерированное ядро IP является с обеспечением совместного доступа и допускающим повторное использование. Можно интегрировать его с большим проектом путем добавления его в среде интегрирования встраиваемой системы, такой как Intel® Qsys, Xilinx® EDK или Интегратор IP Xilinx.

Чтобы изучить, как сгенерировать пользовательское ядро IP, см.:

Можно сгенерировать ядро IP:

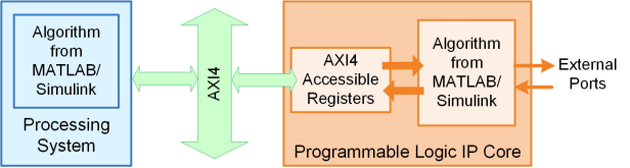

С интерфейсом AXI4 или AXI4-Lite.

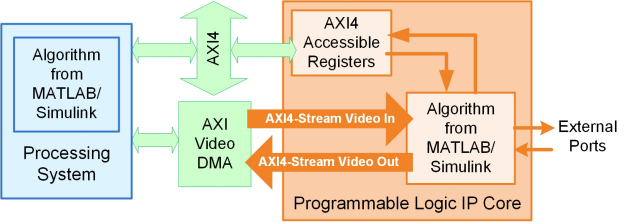

С интерфейсом AXI4 или AXI4-Lite и AXI4-потоковыми Видеоинтерфейсами.

Без любого AXI4 или AXI4-облегченных интерфейсов. Чтобы узнать больше, смотрите, Генерируют Независимое от Совета Ядро IP HDL из Модели Simulink.

Алгоритм из MATLAB/блока Simulink представляет ваш DUT. HDL Coder™ генерирует остальную часть ядра IP на основе ваших настроек интерфейса целевой платформы и режима синхронизации процессора/FPGA.

Можно сопоставить каждый порт в DUT к одному из следующих интерфейсов целевой платформы в ядре IP:

AXI4-облегченный: Используйте этот ведомый интерфейс для регистров управления доступом или для легкой передачи данных. HDL Coder генерирует регистры с отображенной памятью и выделяет смещения адреса для портов, которые вы сопоставляете с этим интерфейсом.

AXI4: Используйте этот ведомый интерфейс, чтобы соединить с компонентами ту пакетную передачу данных поддержки. HDL Coder генерирует регистры с отображенной памятью и выделяет смещения адреса для портов, которые вы сопоставляете с этим интерфейсом.

AXI4-потоковое Видео: Используйте этот интерфейс, чтобы отправить или получить 32-битный скалярный поток видеоданных.

Внешние порты: Используйте внешние порты, чтобы соединить с FPGA внешние контакты IO, или с другими ядрами IP с внешними портами.

Чтобы узнать больше о AXI4, AXI4-облегченном и AXI4-потоковые протоколы Видео, обращаются к вашей документации целевого компьютера.

HDL Coder генерирует логику синхронизации в ядре IP на основе режима синхронизации процессора/FPGA, который вы выбираете.

При генерации пользовательского ядра IP следующие опции синхронизации процессора/FPGA доступны:

Free running (значение по умолчанию)

Coprocessing – blocking

Чтобы узнать больше о режимах синхронизации процессора/FPGA, смотрите Синхронизация FPGA и Процессор.

После того, как вы сгенерируете пользовательское ядро IP, файлы ядра IP находятся в папке ipcore в вашей папке проекта. В HDL Workflow Advisor можно просмотреть имя папки ядра IP в поле IP core folder HDL Code Generation> задача Generate RTL Code and IP Core.

Папка ядра IP содержит следующие сгенерированные файлы:

Файлы определения ядра IP.

Исходные файлы HDL (.vhd или.v).

Заголовочный файл C с таблицей адресов регистра.

(Необязательно) отчет HTML с инструкциями для использования ядра и интеграции ядра IP в вашем проекте встраиваемой системы.