Когда вы открываете HDL Workflow Advisor и запускаете рабочий процесс IP Core Generation для вашей модели Simulink®, можно задать типичную платформу Xilinx® или типичную платформу Intel®. Рабочий процесс затем генерирует типичное ядро IP, которое можно интегрировать в любую целевую платформу по вашему выбору. Для интегрирования ядра IP задайте и укажите пользовательский исходный проект для своей требуемой платы.

Вы не можете сгенерировать ядро IP HDL ни без какого ведомого интерфейса AXI4. По крайней мере один порт DUT должен сопоставить с интерфейсом AXI4 или AXI4-Lite. Чтобы сгенерировать ядро IP HDL без любых ведомых интерфейсов AXI4, используйте рабочий процесс генерации ядра IP Simulink. Для получения дополнительной информации смотрите, Генерируют Независимое от Совета Ядро IP HDL из Модели Simulink.

В том же ядре IP вы не можете сопоставить и с интерфейсом AXI4 и с интерфейсом AXI4-Lite.

Вводы и выводы должны иметь немного ширины, меньше чем или равной 32 битам.

Вход и выходные параметры должны быть скаляром.

Порты должны иметь 32-битную ширину.

Порты должны быть скаляром.

У вас может быть максимум одного входного видеопорта и одного выходного видеопорта.

AXI4-потоковый Видеоинтерфейс не поддержан в Coprocessing – blocking, Processor/FPGA synchronization должен быть установлен в режим Free running. режим Coprocessing – blocking не поддержан.

Сгенерировать независимое от платы ядро IP, чтобы использовать в среде интегрирования встраиваемой системы, такой как Intel Qsys, Xilinx EDK или Интегратор IP Xilinx:

Создайте проект HDL Coder™, содержащий ваш проект MATLAB® и испытательный стенд, или откройте существующий проект.

В HDL Workflow Advisor, входных define типах и выполняют преобразование фиксированной точки.

Чтобы изучить, как преобразовать ваш проект в фиксированную точку, смотрите генерацию HDL-кода и Синтез FPGA из алгоритма MATLAB.

В HDL Workflow Advisor, в задаче Select Code Generation Target:

Workflow: выберите IP Core Generation.

Platform: выберите Generic Xilinx Platform или Generic Altera Platform.

В зависимости от вашего выбора генератор кода автоматически устанавливает Synthesis tool. Например, если вы выбираете Generic Xilinx Platform, Synthesis tool автоматически изменяется на Xilinx Vivado.

Additional source files: Если вы используете Систему hdl.BlackBox object™, чтобы включать существующий Verilog® или код VHDL®, введите имена файлов. Введите вручную каждое имя файла, разделенное точкой с запятой (;), или при помощи кнопки .... Язык исходного файла должен совпадать с вашим выходным языком.

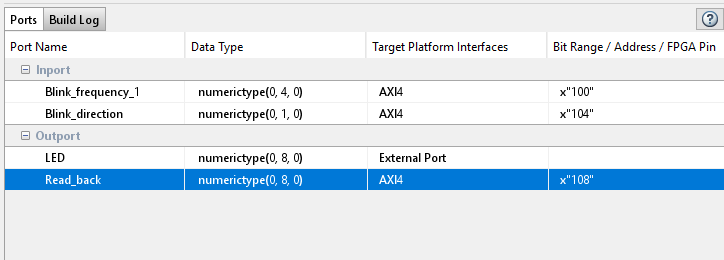

На шаге Set Target Interface, для каждого порта, выбирают опцию из Target Platform Interfaces выпадающий список.

На шаге HDL Code Generation опционально задайте опции генерации кода, затем нажмите Run.

В панели сообщения HDL Workflow Advisor щелкните по ссылке отчета ядра IP, чтобы просмотреть подробную документацию для вашего сгенерированного ядра IP.