Когда вы имеете блоки с состоянием и имеете, включают или сбрасывают порты в подсистеме, используют режим Synchronous блока State Control к:

Обеспечьте эффективный, включают и сбрасывают поведение симуляции на оборудовании.

Сгенерируйте более чистый HDL-код и используйте меньше ресурсов на оборудовании.

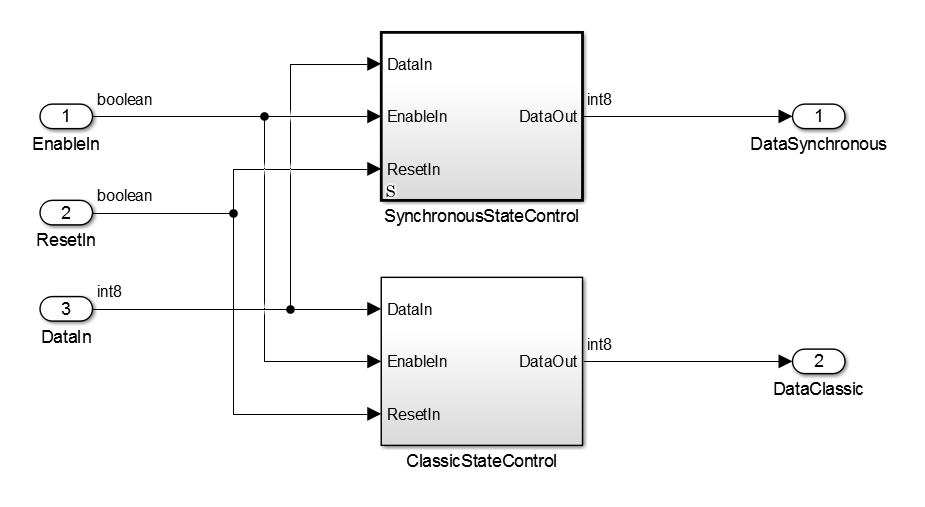

Можно добавить блок State Control в модель Simulink® на любом уровне в иерархии модели. То, как вы устанавливаете блок State Control, влияет на поведение симуляции других блоков в подсистеме, которые имеют состояние.

Для синхронного аппаратного поведения симуляции, набор State control к Synchronous.

Для поведения симуляции Simulink по умолчанию, набор State control к Classic.

| Функциональность | Синхронный режим | Классический режим |

|---|---|---|

| Установка блока State Control | Установка блока по умолчанию, когда вы добавляете блок от библиотеки блоков Подсистем HDL. | Поведение симуляции совпадает с подсистемой, которая не использует блок State Control. |

Поведение симуляции Simulink

| Метод обновления только обновляет состояния. Выходной метод вычисляет выходные значения на каждом временном шаге. Например, когда вы включили подсистемы, изменения выходного значения, когда разрешать сигнал является низким, когда это обрабатывает новые входные значения. Выходное значение совпадает с выводом от режима | Обновления метода обновления утверждают и вычисляют выходные значения. Например, когда вы включили подсистемы, выходное значение считается устойчивое, когда разрешать сигнал является низким и изменяется только, когда разрешать сигнал становится высоким. |

| Поведение симуляции HDL | Более эффективный на оборудовании. | Менее эффективный на оборудовании. |

| Поведение генерации HDL-кода | Сгенерированный HDL-код более чист и использует меньше ресурсов на оборудовании. Например, когда вы включили подсистемы, HDL Coder™ не генерирует обходные регистры для каждого обновления состояния и использует меньше аппаратных ресурсов. | Сгенерированный HDL-код не является столь же чистым и использует больше аппаратных ресурсов. Например, когда вы включили подсистемы, HDL Coder генерирует обходные регистры для каждого обновления состояния и использует больше ресурсов. |

Чтобы узнать больше, когда можно будет использовать блок State Control, смотрите Госконтроль.

Чтобы видеть, использует ли подсистема в вашей модели Simulink синхронную семантику:

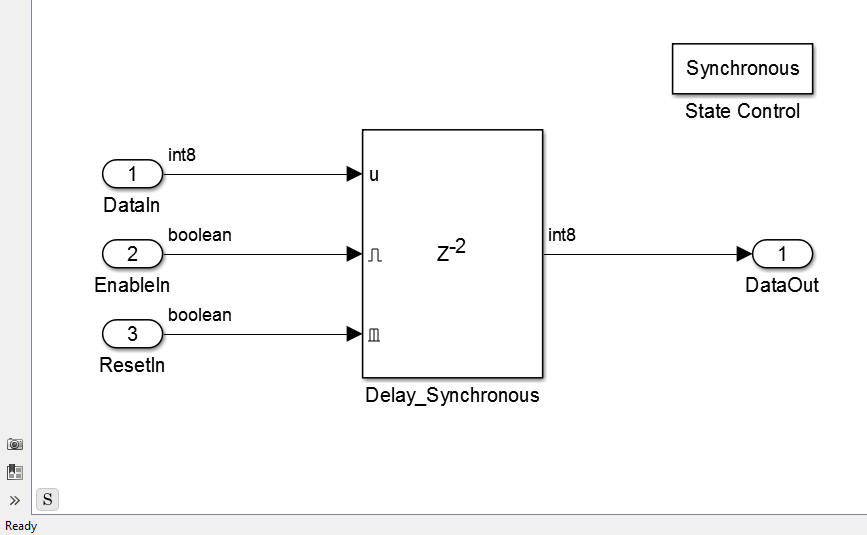

Символ S отображен на подсистеме, чтобы указать на синхронное поведение.

Если вы дважды кликаете подсистему SynchronousStateControl, значок S отображен в редакторе Simulink, чтобы указать, что блоки в подсистеме используют синхронную аппаратную семантику.

SynchronousStateControl и подсистемы ClassicStateControl используют блок Delay с внешним сбросом и разрешать портом в режимах Synchronous и Classic соответственно.

Следующая таблица показывает сравнение HDL-кода, сгенерированного от блока Delay для режимов Classic и Synchronous блока State Control.

| Функциональность | Синхронный режим | Классический режим |

|---|---|---|

Генерация HDL-кода. Настройки применяются:

|

`timescale 1 ns / 1 ns

module SynchronousStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_out1 = Delay_Synchronous_reg[1];

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // SynchronousStateControl

|

`timescale 1 ns / 1 ns

module ClassicStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_bypass; // sfix8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_bypass_next; // sfix8

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_delay_out; // sfix8

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_bypass <= 8'sb00000000;

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_bypass <= Delay_Synchronous_bypass_next;

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_delay_out = (ResetIn == 1'b1 ? 8'sb00000000 :

Delay_Synchronous_reg[1]);

assign Delay_Synchronous_out1 = (EnableIn == 1'b1 ? Delay_Synchronous_delay_out :

Delay_Synchronous_bypass);

assign Delay_Synchronous_bypass_next = Delay_Synchronous_delay_out;

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // ClassicStateControl

|

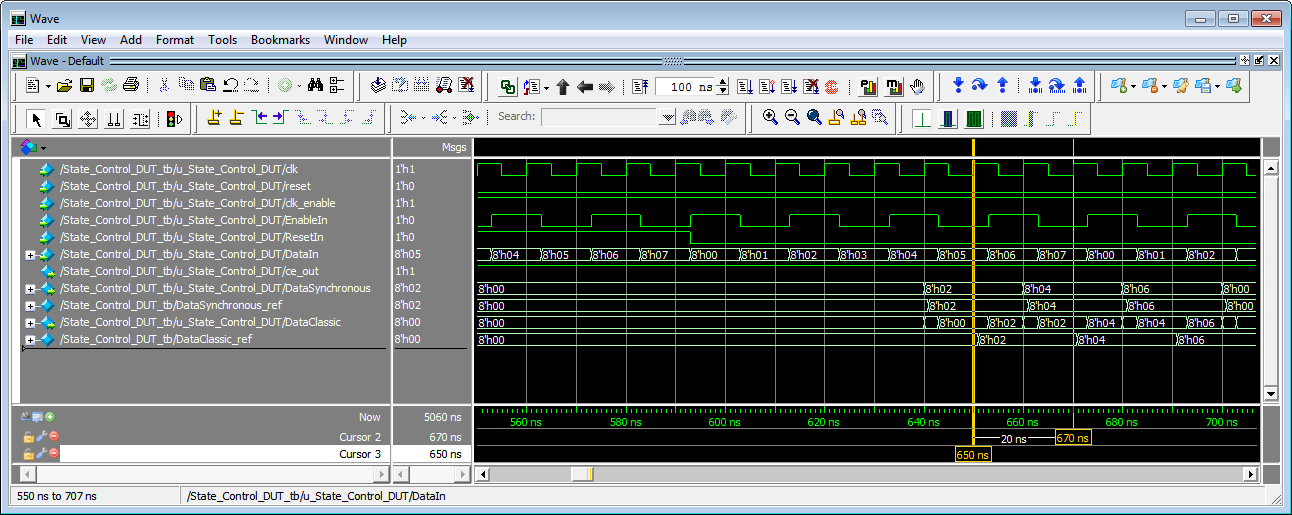

Обратитесь к вышеупомянутой модели Simulink, которая показывает блок Delay что режимы Classic и Synchronous использования блока State Control. Следующая схема показывает поведение симуляции ModelSim® для блока Delay.

Когда сигнал ResetIn высок, DataClassic и сигналы DataSynchronous производят тот же вывод.

Когда и ResetIn и сигналы EnableIn являются низкими, сигнал DataSynchronous содержит свое значение и изменяется только, когда сигнал EnableIn становится высоким в следующем активном фронте синхроимпульса. Значения сигналов DataClassic изменяются, когда сигнал EnableIn является низким, когда он обрабатывает новые входные значения. Значения сигналов DataClassic совпадают со значениями сигналов DataSynchronous, когда EnableIn становится высоким.

Для получения информации о том, как сгенерировать HDL-код и моделировать ваш проект в ModelSim, видит, Генерируют HDL-код из Модели Simulink.