По большей части нет ничего различного в создании модели Simulink®, чтобы действовать как компонент HDL, чем существует от создания модели Simulink, чтобы использовать в качестве испытательного стенда. При использовании Simulink как компонент у вас могут быть несколько HDL блоки Cosimulation, а не один блок HDL Cosimulation, хотя нет никакого ограничения на то, сколько HDL блоки Cosimulation можно использовать в любой ситуации.

Эти шаги описывают, как к cosimulate проект HDL, который тестирует алгоритм, смоделированный с программным обеспечением Simulink.

Создайте проект HDL. Скомпилируйте, разработайте и моделируйте свой модуль в вашем симуляторе HDL. См. Код Компонент HDL.

Разработайте алгоритм и образцовый алгоритм в Simulink. Запустите и протестируйте свою модель полностью прежде заменяющий или добавляющий компоненты модели оборудования, когда Cosimulation блокируется.

Запустите симулятор HDL для использования с MATLAB® и Simulink и загрузите библиотеки HDL Verifier™. Смотрите Запускают симулятор HDL для Cosimulation в Simulink.

Добавьте один или несколько HDL блоки Cosimulation, чтобы обеспечить связь между средствами моделирования. Смотрите Вставляют HDL Блок Cosimulation.

Установите параметры блока HDL Cosimulation. Смотрите Задают HDL Интерфейс Блока Cosimulation.

(Необязательно) Добавьте блок To VCD File, чтобы регистрировать изменения в значениях переменных во время сеанса симуляции. Смотрите Добавляет Файл Дампа изменений значения (VCD).

Начните запускать модель Simulink сначала, затем запустите cosimulation в симуляторе HDL. Смотрите Выполнение Сеанс Cosimulation Simulink.

Задайте режимы направления портов в модуле HDL для симуляции компонента

Задайте типы данных порта в модуле HDL для симуляции компонента

Скомпилируйте и разработайте проект HDL для симуляции компонента

Интерфейс HDL Verifier передает все данные между симулятором HDL и Simulink как данные порта. Программное обеспечение HDL Verifier работает с любым существующим модулем HDL. Однако, когда вы кодируете модуль HDL, который предназначен для верификации Simulink, необходимо полагать, что типы данных совместно используются этими двумя средами и режимами направления.

В вашем операторе модуля необходимо задать каждый порт с режимом направления (вход, вывести, или двунаправленный). Следующая таблица задает эти три режима.

| Используйте VHDL® Mode... | Используйте Verilog® Mode... | Для портов это... |

|---|---|---|

IN | input | Представляйте сигналы, которые могут управляться функцией MATLAB |

OUT | output | Представляйте значения сигналов, которые передаются функции MATLAB |

INOUT | inout | Представляйте двуполярные сигналы, которыми можно управлять или значения передачи к функции MATLAB |

В этом разделе описывается задать типы данных, совместимые с MATLAB для портов в ваших модулях HDL. Для получения дополнительной информации о том, как интерфейс HDL Verifier преобразовывает типы данных для среды MATLAB, смотрите Поддерживаемые Типы данных.

Если вы используете неподдерживаемые типы, программное обеспечение HDL Verifier выдает предупреждение и игнорирует порт во время выполнения. Например, если вы задаете свой интерфейс с пятью портами, один из которых является портом доступа VHDL во время выполнения, затем интерфейс выводит предупреждение, и ваш код видит только четыре порта.

Обратитесь к документации симулятора HDL для инструкции в компиляции и разработке проекта HDL.

Сконфигурируйте временная зависимость симулятора HDL и Simulink

Задайте пред - и постсимуляция команды Tcl с HDL диалоговое окно параметров блоков Cosimulation

После того, как вы кодируете один из компонентов своей модели в VHDL или Verilog и моделируете его в среде симулятора HDL, интегрируете представление HDL в вашу модель Simulink как блок HDL Cosimulation путем выполнения следующих шагов:

Откройте свою модель Simulink, если это не уже открыто.

Удалите компонент модели, который должен заменить блок HDL Cosimulation.

В Браузере Библиотеки Simulink кликните по библиотеке блоков HDL Verifier. Можно затем выбрать библиотеку блоков для поддерживаемого симулятора HDL. Выберите блок Mentor Graphics® ModelSim® HDL Cosimulation или блок Cadence Incisive® HDL Cosimulation, как показано ниже.

![]()

![]()

Скопируйте блок HDL Cosimulation от Браузера Библиотеки до вашей модели.

Соедините любые порты блока HDL Cosimulation с применимыми портами блока в вашей модели Simulink.

Чтобы смоделировать устройство приемника, сконфигурируйте блок с входными параметрами только.

Чтобы смоделировать исходное устройство, сконфигурируйте блок с выходными параметрами только.

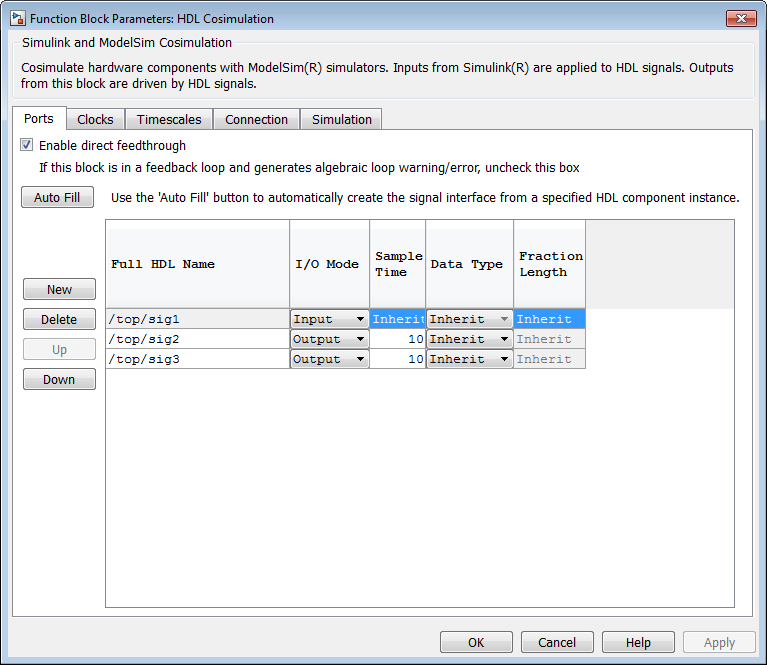

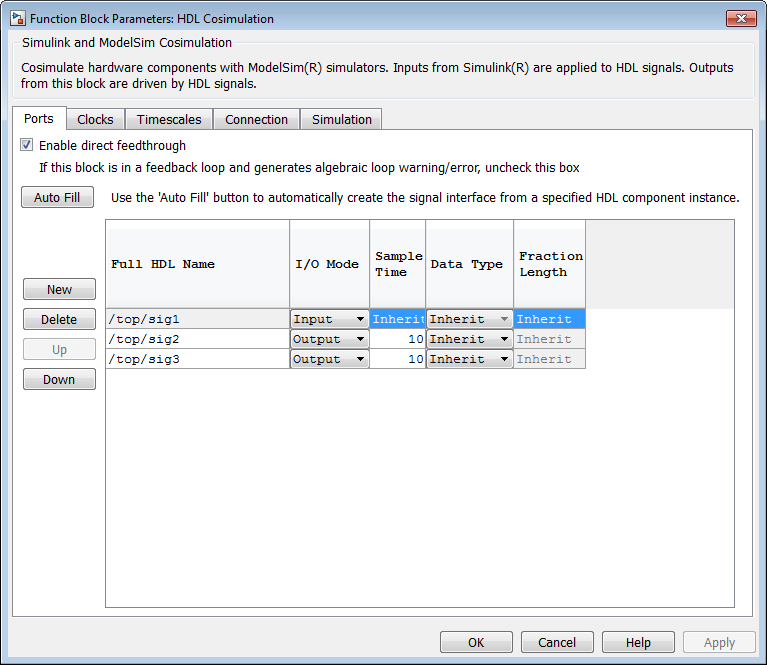

Чтобы открыть диалоговое окно параметров блоков для блока HDL Cosimulation, дважды кликните значок блока. Simulink отображает следующее диалоговое окно Block Parameters (как пример, диалоговое окно для блока HDL Cosimulation для использования с ModelSim показывают ниже).

Задайте Пути к Сигналу/Порту и Модулю HDL для Компонента Simulink Cosimulation

Импортируйте информацию сигнала непосредственно значением входного порта

Первый шаг к конфигурированию вашего блока HDL Verifier HDL Cosimulation должен сопоставить сигналы и экземпляры сигнала вашего проекта HDL к определениям порта в вашем блоке HDL Cosimulation. В дополнение к идентификации портов ввода и вывода можно задать шаг расчета для каждого выходного порта. Можно также задать тип данных с фиксированной точкой для каждого выходного порта.

Сигналы, что вы сопоставляете, могут быть на любом уровне иерархии проекта HDL.

Чтобы сопоставить сигналы, можно выполнить любое из следующих действий:

Введите информацию сигнала вручную в панель Ports диалогового окна параметров блоков. Этот подход может быть более эффективным когда это необходимо, чтобы соединить небольшое количество сигналов от вашей модели HDL до Simulink.

Использование кнопка Auto Fill, чтобы иметь блок HDL Cosimulation получает информацию сигнала для вас путем передачи запроса к симулятору HDL. Этот подход может сэкономить значительные усилия когда это необходимо к cosimulate модель HDL, которая имеет много сигналов, что вы хотите соединиться со своей моделью Simulink. Однако в некоторых случаях необходимо будет отредактировать данные сигнала, возвращенные запросом.

Проверьте, что сигналы, используемые в cosimulation, имеют доступ для чтения-записи. Для более высокой производительности вы хотите обеспечить доступ только к тем сигналам, используемым в cosimulation. Это правило применяется ко всем сигналам на Ports, Clocks и панелях Simulation, и ко всем сигналам, добавленным любым другим способом.

Задайте Пути к Сигналу/Порту и Модулю HDL для Компонента Simulink Cosimulation. Эти правила для сигнала/порта и спецификаций пути к модулю в Simulink. Другие спецификации могут работать, но явным образом или неявно не поддержаны в этом или будущих релизах.

Проекты HDL обычно имеют иерархию; это - причина этого синтаксиса. Эта спецификация не представляет иерархию имени файла.

Спецификации пути для верхнего уровня Verilog

Спецификации пути для верхнего уровня Verilog

Спецификации пути для верхнего уровня VHDL

Спецификации пути для верхнего уровня VHDL

Получите информацию Сигнала от симулятора HDL. Кнопка Auto Fill позволяет вам начать запрос симулятора HDL и предоставить путь к компоненту или модулю в модели HDL при симуляции в симуляторе HDL. Обычно, некоторое изменение информации порта требуется после того, как запрос завершается. У вас должен быть симулятор HDL, запускающийся с модулем HDL, загруженным для Auto Fill, чтобы работать.

Следующий пример описывает необходимые шаги.

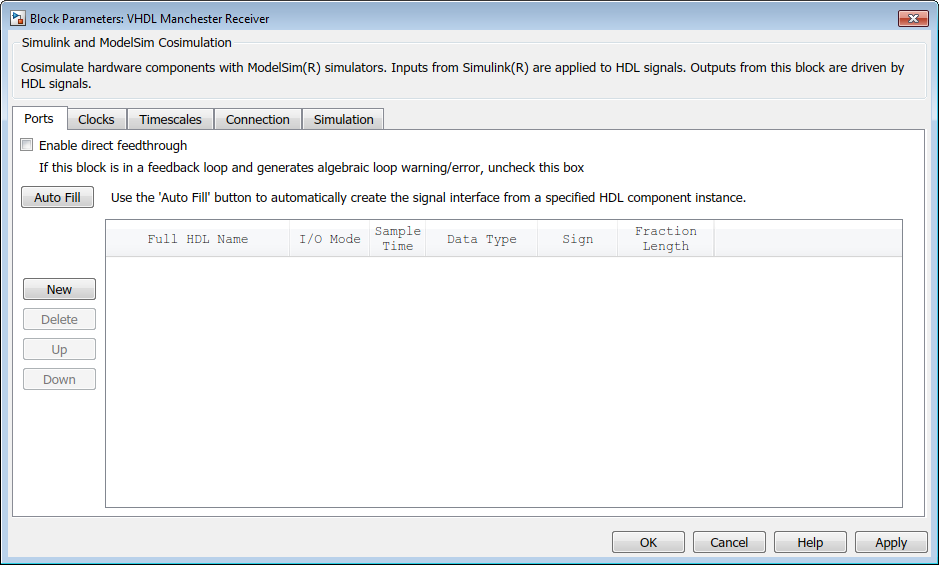

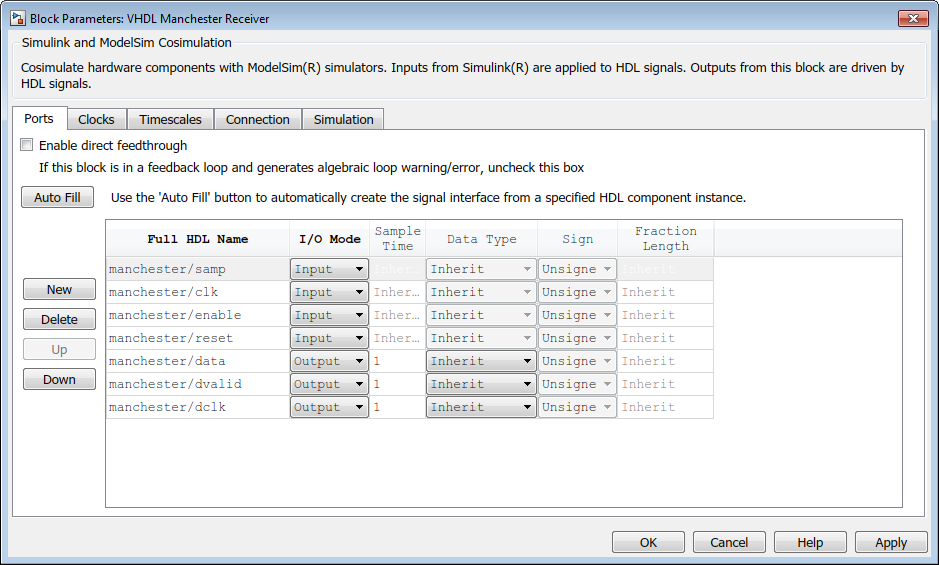

Пример основан на измененной копии модели Manchester Receiver, в которой все сигналы были сначала удалены из панелей Clocks и Ports.

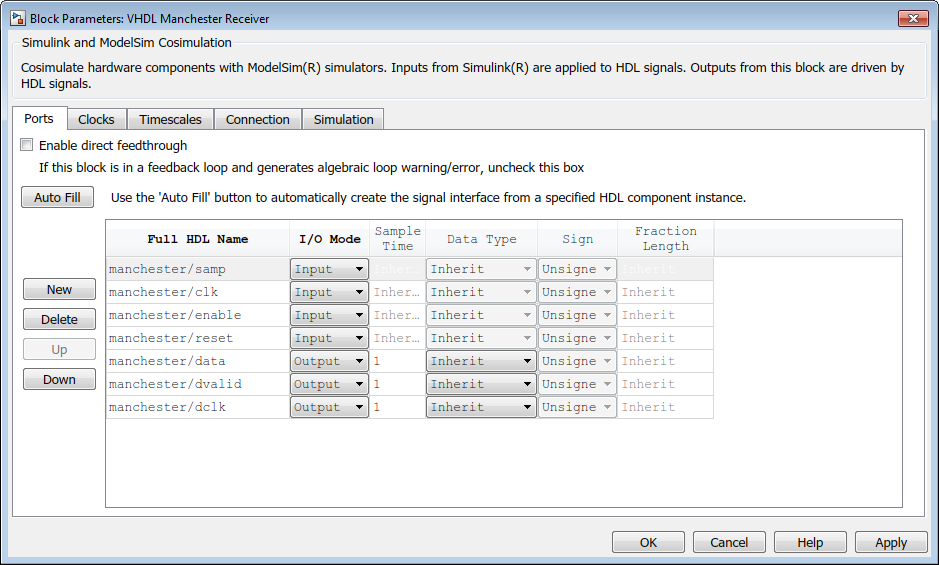

Откройте диалоговое окно параметров блоков для блока HDL Cosimulation. Кликните по вкладке Ports. Панель Ports открывается (как пример, панель Ports для блока HDL Cosimulation для использования с ModelSim показывают на рисунках ниже).

Удалите все порты прежде, чем выполнить Auto Fill, чтобы убедиться, что никакой неиспользованный сигнал не остается в Списке портов никогда.

Нажмите кнопку Auto Fill. Диалоговое окно Auto Fill открывается.

Это модальное диалоговое окно запрашивает путь к экземпляру к компоненту или модулю в вашей модели HDL; здесь вы вводите явный путь к HDL в поле редактирования. Путь, который вы вводите, не является путем к файлу и не имеет никакого отношения к исходным файлам.

В этом примере Автоматическая функция Заливки получает данные порта для компонента VHDL под названием manchester. Путь к HDL задан как /top/manchester. Спецификации пути будут отличаться в зависимости от вашего симулятора HDL, видеть, Задают Пути к Сигналу/Порту и Модулю HDL для Компонента Simulink Cosimulation.

Нажмите Fill, чтобы отклонить диалоговое окно, и запрос передается.

После того, как симулятор HDL возвращает данные порта, Автоматическая функция Заливки вводит его в панель Ports, как показано в следующей фигуре (примеры, показанные для использования с Острым Тактовым сигналом).

Нажмите Apply, чтобы фиксировать сложения порта.

Удалите неиспользованные сигналы из Портов, разделяют на области и добавляют сигнал Часов.

Предыдущие данные показывают, что запрос ввел часы, часы включают и сбрасывают порты (маркировал clk, enable и reset соответственно) в список портов.

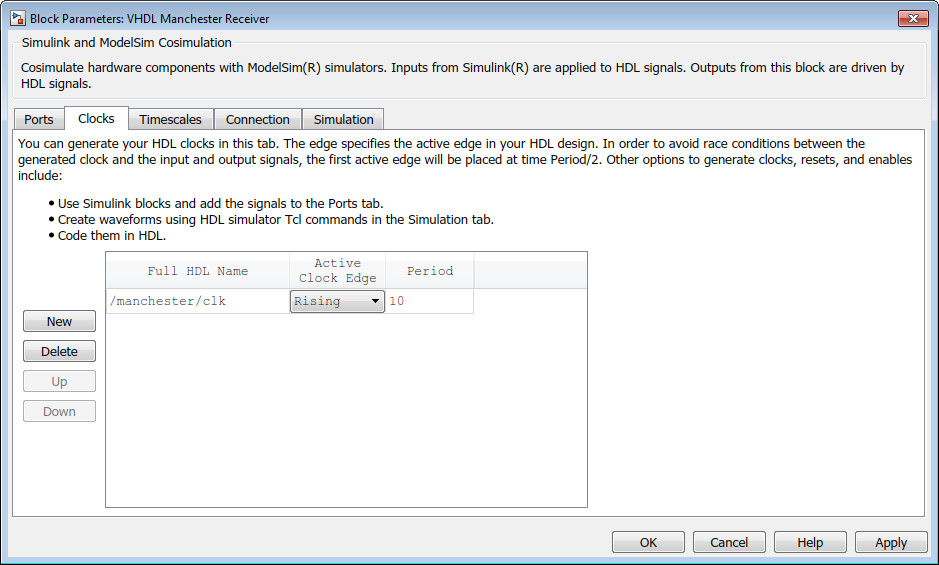

Удалите clk, enable и сигналы reset от панели Ports, и добавьте сигнал clk в панели Clocks.

Эти действия приводят к сигналам, показанным в следующих фигурах.

Auto Fill возвращает значения по умолчанию для выходных портов:

Sample time: 1

Тип данных: Inherit

Fraction length: Inherit

Вы, возможно, должны изменить эти значения как требуется вашей моделью. В этом примере Sample time должен быть установлен в 10 для всех выходных параметров. См., “Задают Типы Данных сигнала”.

Прежде, чем закрыть диалоговое окно параметров блоков, нажмите Apply, чтобы фиксировать любые редактирования, которые вы сделали.

Заметьте, что Auto Fill возвратил информацию обо всех вводах и выводах для целенаправленного компонента. Во многих случаях это будет включать эту функцию сигналов в симулятор HDL, но не может быть соединено в модели Simulink. Можно удалить любые такие записи из списка в панели Ports, если они нежелательны. Можно управлять сигналами от Simulink; только необходимо задать их значения путем установления блоков Simulink.

Обратите внимание на то, что Auto Fill не возвращает информацию для внутренних сигналов. Если ваша модель Simulink должна получить доступ к таким сигналам, необходимо ввести их в панель Ports вручную. Например, в случае модели Manchester Receiver, необходимо было бы добавить записи выходного порта для top/manchester/sync_i, top/manchester/isum_i и top/manchester/qsum_i, как показано на шаге 8.

Incisive® и пользователи ModelSim: Обратите внимание на то, что clk, сброс и clk_enable могут быть в Часах и панелях Симуляции, но они не должны быть. Эти сигналы могут быть портами, если вы принимаете решение управлять ими явным образом от Simulink.

Когда вы импортируете сигналы VHDL с помощью Auto Fill, симулятор HDL возвращает имена сигнала во всех прописных буквах.

Введите информацию Сигнала вручную. Чтобы ввести информацию сигнала непосредственно в панель Ports, выполните следующие шаги:

В симуляторе HDL решите, что имена пути прохождения сигнала для HDL сигнализируют, что вы планируете задать в своем блоке. Например, в средстве моделирования ModelSim, следующее окно волны показывает, что все сигналы зависимы от модуля верхнего уровня manchester.

В Simulink, открытом диалоговое окно параметров блоков для вашего блока HDL Cosimulation, если это не уже открыто.

Выберите вкладку панели Ports. Simulink отображает следующее диалоговое окно (пример, показанный для использования с Острым).

В этой панели вы задаете сигналы HDL своего проекта, что вы хотите включать в свой блок Simulink и установить шаг расчета и тип данных для выходных портов. Параметры, которые необходимо задать на панели Ports, зависят от типа устройства, которое блок моделирует можно следующим образом:

Для устройства, имеющего оба ввода и вывода: задайте входные порты блока, блокируйте выходные порты, выведите типы выходных данных и шаги расчета.

Для выходных портов примите значение по умолчанию или введите явный шаг расчета. Типы данных могут быть заданы явным образом или установлены в Inherit (значение по умолчанию). В случае по умолчанию тип данных выходного порта наследован или от сигнала, соединенного с портом, или вывел из модели HDL.

Для устройства приемника: задайте выходные порты блока.

Для исходного устройства: задайте входные порты блока.

Введите имена пути прохождения сигнала в столбце Full HDL name путем двойного клика на существующем сигнале по умолчанию.

Используйте синтаксис пути симулятора HDL (как описано в, Задают Пути к Сигналу/Порту и Модулю HDL для Места размещения Simulink Test Cosimulation).

Если вы добавляете сигналы, нажмите New и затем отредактируйте значения по умолчанию. Выберите Input или Output из столбца I/O Mode.

Если вы хотите, установите Sample Time, Data Type и параметры Fraction Length для сигналов явным образом, как обсуждено на остающихся шагах.

Когда вы закончите редактировать сигналы часов, нажмите Apply, чтобы указать ваши изменения с Simulink.

Следующее диалоговое окно показывает определения порта для блока HDL Cosimulation. Имена пути прохождения сигнала совпадают с путями, которые появляются в окне wave симулятора HDL (Острый показанный пример).

Когда вы задаете входной порт, убедитесь, что только один источник настраивается, чтобы обеспечить вход к тому порту. Если многочисленные источники управляют сигналом, ваша модель Simulink может привести к непредсказуемым результатам.

Необходимо задать шаг расчета для выходных портов. Simulink использует значение, которое вы задаете, и текущие настройки панели Timescales, чтобы вычислить фактический шаг расчета симуляции.

Для получения дополнительной информации о шагах расчета в HDL Verifier cosimulation среда, смотрите Масштабы времени Симуляции.

Можно сконфигурировать тип данных с фиксированной точкой каждого выходного порта явным образом при желании или использовать значение по умолчанию (Inherited). В случае по умолчанию Simulink определяет тип данных для выходного порта можно следующим образом:

Если Simulink может определить тип данных сигнала, соединенного с выходным портом, это применяет тот тип данных к выходному порту. Например, тип данных связанного блока Signal Specification известен обратной связью. В противном случае Simulink запрашивает симулятор HDL, чтобы определить тип данных сигнала от модуля HDL.

Чтобы присвоить явный тип данных с фиксированной точкой сигналу, выполните следующие шаги:

Выберите Signed или Unsigned из столбца Data Type.

Если сигнал имеет дробную часть, введите Fraction Length.

Например, если модель имеет 8-битный сигнал с типом данных Signed и Fraction Length 5, блок HDL Cosimulation присваивает его тип данных sfix8_En5. Если модель имеет Unsigned 16-битный сигнал без дробной части (Fraction Length 0), блок HDL Cosimulation присваивает его тип данных ufix16.

Прежде, чем закрыть диалоговое окно, нажмите Apply, чтобы указать ваши редактирования.

Импортируйте информацию Сигнала Непосредственно Значением Входного порта. Включение прямого сквозного соединения позволяет изменениям значения входного порта распространить к выходным портам в нулевое время, таким образом устраняя возможную задержку на выходной выборке в проектах HDL с чистой комбинационной логикой. Задайте опцию, чтобы включить прямое сквозное соединение на панели Ports, как показано в следующей фигуре.

Data Type и параметры Fraction Length применяются только к выходным сигналам. Смотрите Data Type и Fraction Length на описании панели Портов блока HDL Cosimulation.

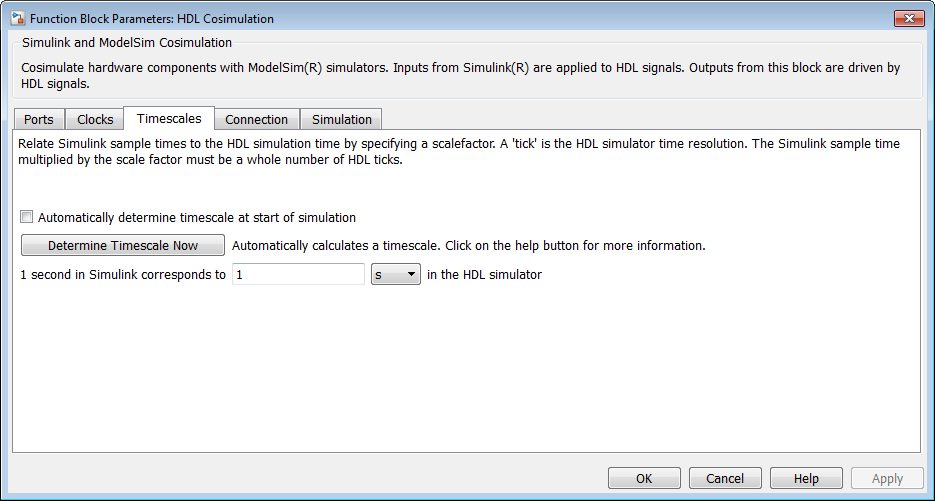

Вы конфигурируете временную зависимость между Simulink и симулятором HDL при помощи панели Timescales диалогового окна параметров блоков. Прежде, чем установить параметры Timescales, считайте Масштабы времени Симуляции, чтобы понять поддерживаемые режимы синхронизации и проблемы, которые определят ваш выбор синхронизации режима.

Можно задать или родственника или абсолютную временную зависимость между Simulink и симулятором HDL в панели Timescales, как описано в ссылке блока HDL Cosimulation.

Задайте Временная зависимость симулятора HDL и Simulink. Различия в представлении времени симуляции могут быть согласованы в одном из двух способов использовать интерфейс HDL Verifier:

Путем определения временной зависимости вручную (с панелью Timescales)

Когда вы задаете отношение вручную, вы определяете, сколько фемтосекунд, пикосекунд, наносекунды, микросекунды, миллисекунды, секунды или метки деления в симуляторе HDL представляет 1 секунду в Simulink.

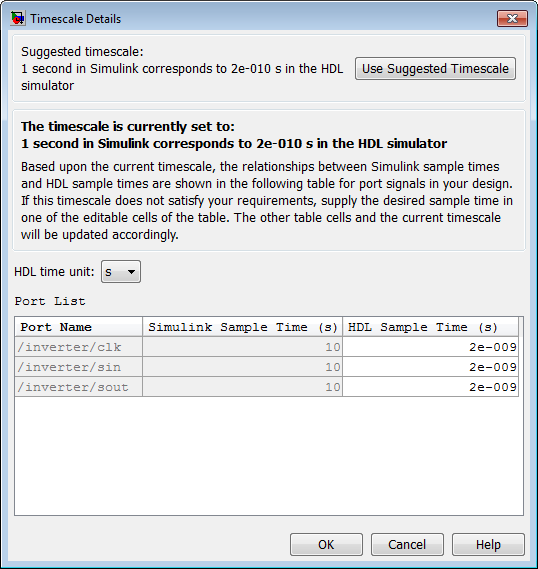

![]()

Это количество времени симулятора HDL может быть выражено одним из следующих способов:

В относительном выражении (т.е. как некоторое количество меток деления симулятора HDL). В этом случае cosimulation, как говорят, действует в относительном режиме синхронизации. Значения по умолчанию блока HDL Cosimulation к относительному режиму синхронизации для cosimulation. Для больше на относительном режиме синхронизации, смотрите Относительный Режим Синхронизации.

В абсолютных единицах (таких как миллисекунды или наносекунды). В этом случае cosimulation, как говорят, действует в абсолютном режиме синхронизации. Для больше на абсолютном режиме синхронизации, смотрите Абсолютный Режим Синхронизации.

Для больше на относительном и абсолютном времени, смотрите Масштабы времени Симуляции.

Позволяя HDL Verifier задать масштаб времени (с панелью Timescales)

Когда вы позволяете программному обеспечению ссылки задавать временную зависимость, оно пытается установить фактор масштаба времени между симулятором HDL и Simulink быть максимально близким к 1 секунде в симуляторе HDL = 1 секунда в Simulink. Если эта установка не возможна, продукт ссылки пытается установить уровень сигнала на порте модели Simulink к самому низкому количеству меток деления симулятора HDL.

Прежде чем вы начнете, проверите, что симулятор HDL запускается. Программное обеспечение HDL Verifier может получить предел разрешения симулятора HDL только, когда то средство моделирования запускается.

Можно принять решение иметь HDL Verifier, вычисляют масштаб времени, в то время как вы устанавливаете параметры на диалоговом окне блока путем нажатия на опцию Timescale, затем нажатие по Determine Timescale Now, или у вас может быть HDL Verifier, вычисляют масштаб времени, когда симуляция начинается путем выбора Automatically determine timescale at start of simulation.

Когда вы нажимаете Determine Timescale Now, HDL Verifier соединяет Simulink с симулятором HDL так, чтобы это могло использовать разрешение симулятора HDL, чтобы вычислить лучший масштаб времени. Можно признать, что HDL Verifier масштаба времени предлагает, или можно внести изменения в списке портов непосредственно. Если вы хотите вернуться к первоначально расчетным настройкам, нажмите Use Suggested Timescale. Если вы хотите просмотреть шаги расчета для всех портов в проекте HDL, выберите Show all ports and clocks.

Если вы выбираете Automatically determine timescale at start of simulation, вы получаете то же диалоговое окно, когда симуляция запускается в Simulink. Внесите те же корректировки в то время, если применимо, что вы были бы, если вы нажали Determine Timescale Now, когда вы конфигурировали блок.

Необходимо выбрать коммуникацию общей памяти или сокета. Смотрите HDL Cosimulation с MATLAB или Simulink.

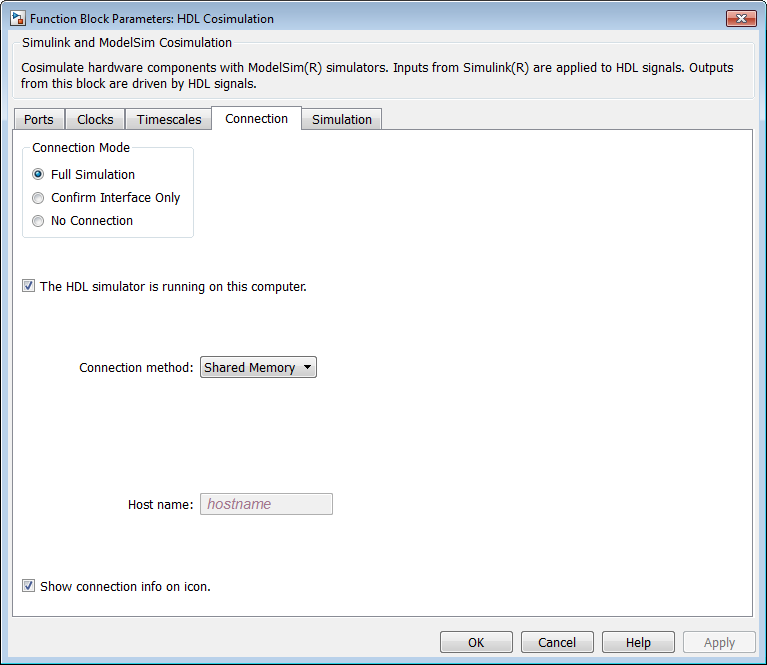

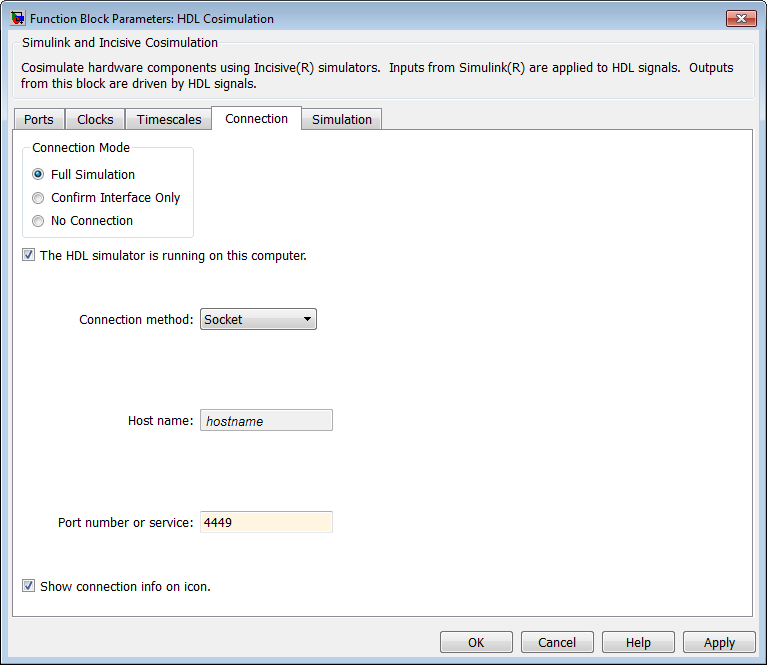

После того, как вы решите, который тип коммуникации, сконфигурируйте линию связи блока с панелью Connection диалогового окна параметров блоков (пример, показанный для использования с ModelSim).

Следующие шаги проводят вас по коммуникационной настройке:

Определите, работают ли Simulink и симулятор HDL на том же компьютере. Если они, пропускают к шагу 4.

Отменяйте The HDL simulator is running on this computer. (Этот флажок значения по умолчанию к выбранному.), Поскольку Simulink и симулятор HDL работают на различных компьютерах, HDL Verifier устанавливает Connection method на Socket.

Введите имя хоста компьютера, который запускает вашу симуляцию HDL (в симуляторе HDL) в текстовом поле Host name. В текстовом поле Port number or service задайте номер действительного порта или сервис для вашей компьютерной системы. Для получения информации о выборе портов сокета TCP/IP смотрите Порты Сокета TCP/IP. Пропустите к шагу 5.

Если симулятор HDL и Simulink работают на том же компьютере, решают, собираетесь ли вы использовать общую память или сокеты TCP/IP для канала связи. Для получения информации о различных режимах коммуникации смотрите HDL Cosimulation с MATLAB или Simulink.

Если вы выбираете коммуникацию сокета TCP/IP, задаете номер действительного порта или сервис для вашей компьютерной системы в текстовом поле Port number or service. Для получения информации о выборе портов сокета TCP/IP смотрите Порты Сокета TCP/IP.

Если вы выбираете коммуникацию общей памяти, устанавливаете флажок Shared memory.

Если вы хотите обойти симулятор HDL, когда вы запускаете симуляцию Simulink, используйте опции Connection Mode, чтобы задать, какую связь симуляции вы хотите. Выберите одну из следующих опций:

Full Simulation: Подтвердите интерфейс и симуляцию HDL выполнения (значение по умолчанию).

Confirm Interface Only: Проверяйте симулятор HDL на ожидаемые имена сигнала, размерности и типы данных, но не запускайте симуляцию HDL.

No Connection: не связывайтесь с симулятором HDL. Симулятор HDL не должен быть запущен.

Со вторыми и третьими опциями программное обеспечение HDL Verifier не связывается с симулятором HDL во время симуляции Simulink.

Нажмите Apply.

Следующее диалоговое окно примера показывает коммуникационные определения для блока HDL Cosimulation. Блок сконфигурирован для Simulink и симулятора HDL, работающего на том же компьютере, связывающемся в режиме сокета TCP/IP по порту TCP/IP 4449.

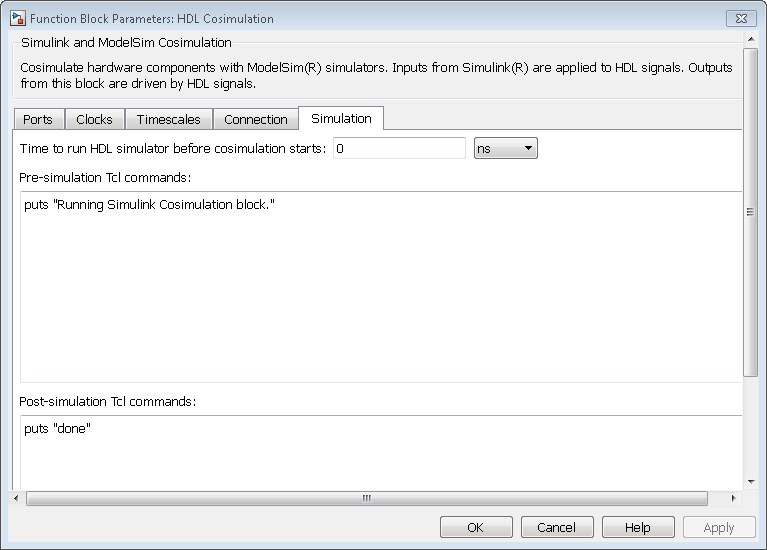

У вас есть опция определения, что команды Tcl, чтобы выполниться до и после симулятора HDL моделируют компонент HDL вашей модели Simulink. Tcl является программируемым языком сценариев, поддержанным большинством сред симуляции HDL. Использование Tcl может колебаться от чего-то столь же простого как короткая команда puts, чтобы подтвердить, что симуляция запускается или столь же завершенная как комплексный скрипт, который выполняет обширную последовательность инициализации и запуска симуляции. Например, можно использовать поле Post- simulation command на Панели Симуляции, чтобы дать симулятору HDL команду перезапускать в конце запущенной симуляции.

После каждой симуляции требуется время ModelSim, чтобы обновить результат покрытия. Чтобы предотвратить потенциальный конфликт между этим процессом и следующим cosimulation сеансом, добавьте короткую паузу между каждой последовательной симуляцией.

Можно задать предварительную симуляцию и постсимуляцию команды Tcl путем ввода команд Tcl в the Pre-simulation команды или текстовых полей команд Post-simulation в панели Simulation HDL диалоговое окно параметров блоков Cosimulation.

Чтобы задать команды Tcl, выполните следующие шаги:

Выберите вкладку Simulation диалогового окна параметров блоков. Диалоговое окно появляется можно следующим образом (пример, показанный для использования с ModelSim).

Текстовое поле Pre-simulation commands включает команду puts в ссылочных целях.

Введите одну или несколько команд в текстовые поля Pre-simulation command и Post-simulation command. Можно задать одну команду Tcl на строку в текстовом поле или ввести несколько команд на строку путем добавления каждой команды с точкой с запятой (;), который является стандартным оператором конкатенации Tcl.

Нажмите Apply.

Одним путем к параметрам блока управления является через блок HDL Cosimulation графическое диалоговое окно. Однако вы можете также блоки управления, программно управляя значениями параметров маски и выполнением симуляций. Значения параметров могут быть считаны с помощью функции get_param Simulink и записаны с помощью функции set_param Simulink. Все параметры блоков имеют атрибуты, которые указывают, являются ли они:

Настраиваемый — атрибуты могут измениться во время запущенной симуляции.

Оцененный — значение параметров подвергается оценке, чтобы определить ее фактическое значение, используемое S-функцией.

Блок HDL Cosimulation не имеет никаких настраиваемых параметров; таким образом вы получаете ошибку, при попытке изменить значение, в то время как симуляция запускается. Однако это действительно имеет несколько оцененных параметров.

Вы видите список параметров и их атрибутов путем выполнения щелчка правой кнопкой мыши по блоку, выбора View Mask, и затем вкладки Parameters. Столбец Variable показывает программируемые названия параметра. Также можно получить имена программно путем выбора блока HDL Cosimulation и затем ввода следующих команд в посдказке MATLAB:

>> get_param(gcb, 'DialogParameters')

Некоторые примеры использования MATLAB, чтобы управлять симуляциями и значениями параметров маски следуют. Обычно, команды помещаются в скрипт или файл функции и вызваны несколькими рычагами коллбэка, доступными образцовому разработчику. Можно поместить код в любое из этих предложенных местоположений, или где угодно вы выбираете:

В рабочем пространстве модели, например, View> Model Explorer> Simulink Root> model_name> Model Workspace, опция Data Source установлен в Model File.

В образцовом коллбэке, например, File> Model Properties> Callbacks.

Коллбэк подсистемы (щелчок правой кнопкой мыши по пустой подсистеме и затем выбирают Properties> Callbacks). Многие демонстрации HDL Verifier используют этот метод, чтобы запустить симулятор HDL путем размещения кода MATLAB в коллбэк OpenFcn.

Коллбэк блока HDL Cosimulation (щелчок правой кнопкой мыши по блоку HDL Cosimulation, и затем выбирают Properties> Callbacks).

Пример: Сценарии Значения Номера Сокета для Коммуникации симулятора HDL. В среде регрессии вы, возможно, должны определить номер сокета для связи SIMULINK/СИМУЛЯТОРА HDL во время симуляции, чтобы избежать столкновений с другими выполнениями симуляции. Этот пример показывает код, который мог справиться с той задачей. Скрипт для 32-битной платформы Linux®.

ttcp_exec = [matlabroot '/toolbox/shared/hdllink/scripts/ttcp_glnx'];

[status, results] = system([ttcp_exec ' -a']);

if ~s

parsed_result = textscan(results,'%s');

avail_port = parsed_result{1}{2};

else

error(results);

end

set_param('MyModel/HDL Cosimulation', 'CommPortNumber', avail_port);