Этот пример проводит вас по основным шагам для подготовки приложения HDL Verifier™, которое использует Simulink® и симулятор HDL, чтобы проверить проект HDL, с помощью модели Simulink в качестве испытательного стенда. В этом примере вы выполняете шаги к cosimulate Simulink и симулятору HDL, чтобы проверить простой повышенный фильтр косинуса, написанный в Verilog®.

Этот пример требует Simulink, HDL Verifier, Fixed-Point Designer™, и симулятора HDL Incisive® или ModelSim®. Этот пример предполагает, что вы считали HDL-код Импорта для HDL Блок Cosimulation.

В этом примере вы выполняете следующие шаги:

Чтобы помочь копиям доступа других учебных файлов, настройте папку для своей собственной учебной работы путем следования этим инструкциям:

Создайте папку вне осциллографа вашей папки установки MATLAB®, в которую можно скопировать учебные файлы. Папка должна быть перезаписываема. Этот пример предполагает, что вы создаете папку под названием MyTests.

Скопируйте все файлы, расположенные в следующей директории к папке, которую вы создали:

matlabroot\toolbox\edalink\foundation\hdllink\demo_src\tutorial

где matlabroot является корневым каталогом MATLAB в вашей системе.

У вас теперь есть все следующие файлы в вашей рабочей директории, несмотря на то, что для этого примера вам будут нужны только два из них:

filter_tb.v (не используемый для этого примера)

mycallback_solution.m (не используемый для этого примера)

rcosflt_beh.v (не используемый для этого примера)

rcosflt_rtl.v

rcosflt_rtl.vhd

rcosflt_tb.mdl

StartMatlab.

Установите директорию, которую вы создали в Примере: Настройте Учебные Файлы (Simulink) как ваш текущий каталог в MATLAB.

В подсказке команды MATLAB введите следующее:

>>cosimWizard

Команда запускает Cosimulation Wizard.

Этот пример приводит вас через следующие страницы мастера, разработанные, чтобы помочь вам в создании блока HDL Cosimulation.

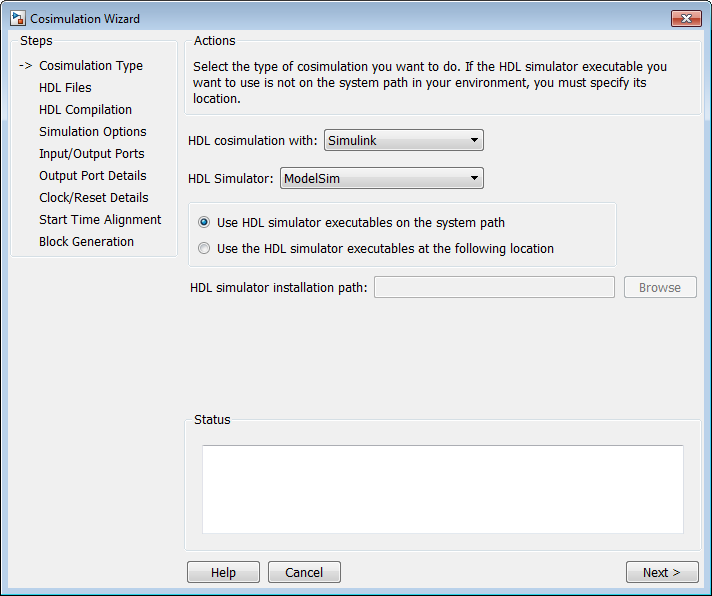

В Полосе набора Cosimulation выполните следующие шаги:

Оставьте набор опции HDL cosimulation with Simulink.

Если вы используете ModelSim, оставляете опцию HDL Simulator как ModelSim.

Если вы используете Острый, изменяете опцию HDL Simulator на Incisive.

Оставьте опцию опции по умолчанию Use HDL simulator executables on the system path, если исполняемые файлы симулятора HDL появляются на вашем системном пути.

Если они, исполняемый файл не появляется на пути, задают путь к симулятору HDL, как описано в Типе Cosimulation — блок Simulink.

Нажмите Next, чтобы перейти к странице HDL Files.

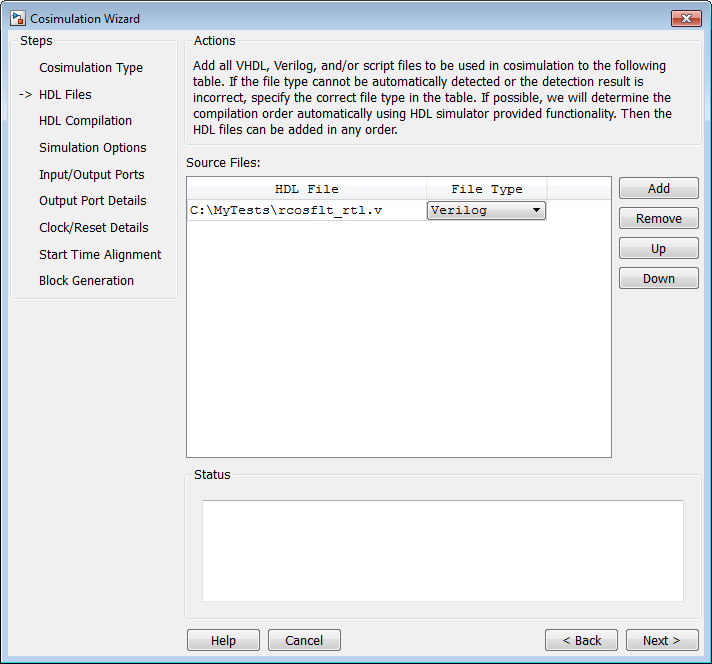

На странице HDL Files выполните следующие шаги:

Добавьте файлы HDL в список файлов.

Нажмите Add и обзор к директории, которую вы создали в Примере: Настройте Учебные Файлы (Simulink).

Для Verilog выберите rcosflt_rtl.v. Для VHDL® выберите rcosflt_rtl.vhd.

Рассмотрите файл в списке файлов с типом файла, идентифицированным, как вы ожидали.

Нажмите Next, чтобы перейти к странице HDL Compilation.

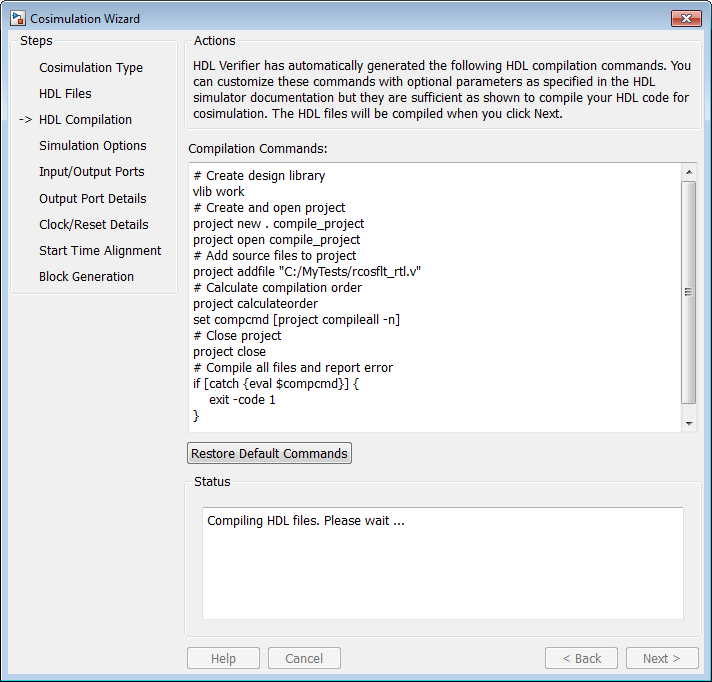

Cosimulation Wizard перечисляет команды по умолчанию в окне Compilation Commands. Вы не должны изменять эти команды для этого примера.

Когда вы запускаете Cosimulation Wizard со своим собственным кодом, можно добавить или изменить команды компиляции в этом окне. Например, можно добавить переключатель -vlog01compat.

Пользователи ModelSim: панель Компиляции HDL будет выглядеть подобной той в этой фигуре:

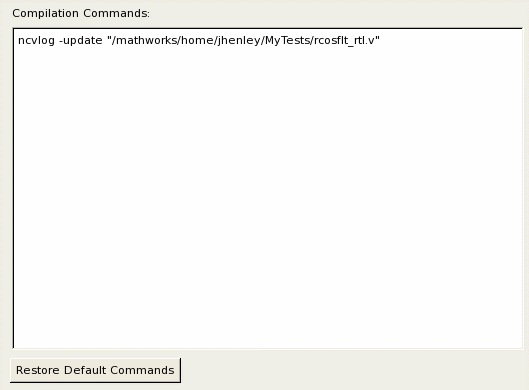

Острые пользователи: Ваша панель Компиляции HDL будет выглядеть подобной той в следующей фигуре.

Нажмите Next, чтобы перейти к панели Модулей HDL.

Консоль MATLAB отображает журнал компиляции. Если ошибка происходит во время компиляции, та ошибка появляется в области Status. Измените любые настройки, вы можете, чтобы удалить ошибку прежде, чем перейти к следующему шагу.

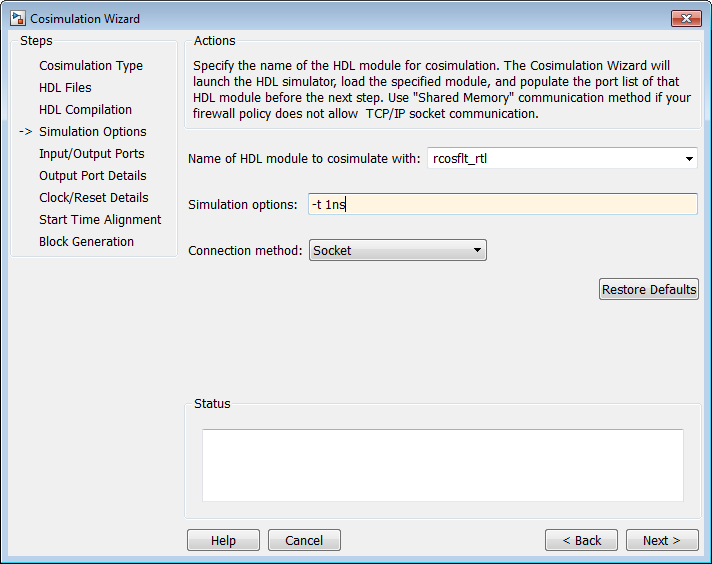

В панели Опций Симуляции выполните следующие шаги:

Задайте имя модуля/сущности HDL для cosimulation.

Из выпадающего списка выберите rcosflt_rtl. Этот модуль является модулем Verilog/VHDL, который вы используете для cosimulation.

Если вы не видите rcosflt_rtl в выпадающем списке, можно ввести имя файла вручную.

Для Connection method выберите Shared Memory, если ваша политика брандмауэра не позволяет коммуникацию сокета TCP/IP.

Опции симуляции теперь выглядят подобными показанным в следующей фигуре.

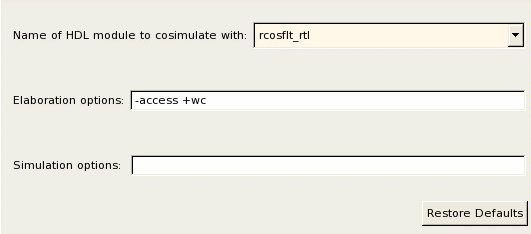

Острые пользователи: Ваши опции Модуля HDL выглядят подобными следующей фигуре

Нажмите Next, чтобы перейти к панели Портов Simulink.

Cosimulation Wizard запускает симулятор HDL в фоновом режиме консоль с помощью заданного модуля HDL и опций симуляции. После того, как мастер запускает симулятор HDL, мастер заполняет порты ввода и вывода на модели Verilog/VHDL rcosflt_rtl и отображает их на следующем шаге.

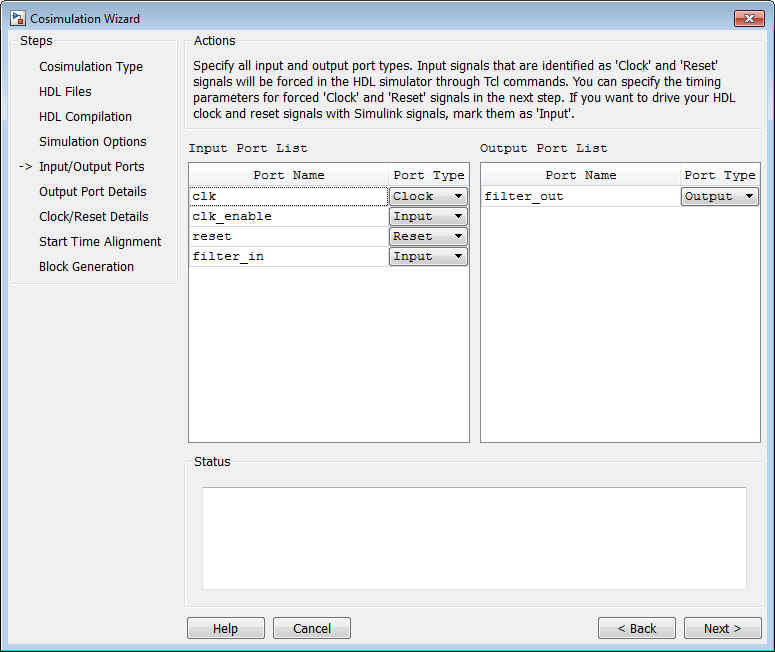

На этом шаге Cosimulation Wizard отображает две таблицы, содержащие порты ввода и вывода rcosflt_rtl, соответственно.

Cosimulation Wizard пытается идентифицировать тип порта для каждого порта. Если мастер неправильно идентифицирует порт, можно изменить тип порта с помощью этих таблиц.

Для входных портов можно выбрать из Clock, Reset, Input или Unused. HDL Verifier соединяется, только входные порты отметили Input к Simulink во время cosimulation.

HDL Verifier соединяется, выходные порты отметили Output Simulink во время cosimulation. Мастер и Simulink игнорируют те выходные порты, отмеченные Unused во время cosimulation.

Можно изменить параметры для сигналов, идентифицированных как Clock и Reset на более позднем шаге.

Примите типы порта по умолчанию и нажмите Next, чтобы перейти к странице Output Port Details.

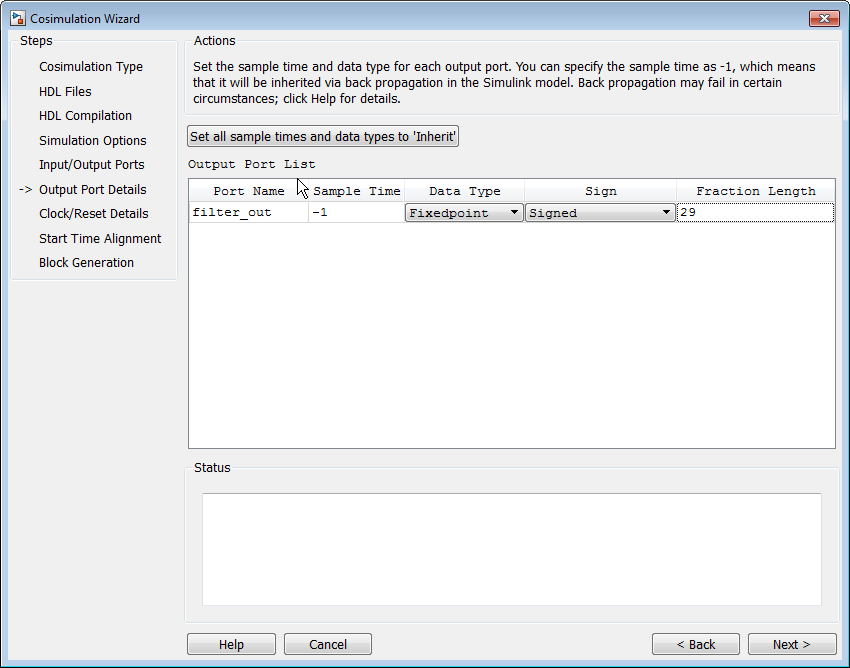

На странице Output Port Details выполните следующие шаги:

Установите шаг расчета filter_out к-1 наследоваться через обратное распространение.

Вы видите из кода Verilog, что Cosimulation Wizard представляет вывод в формате S34,29. Измените следующие поля:

Тип данных к Fixedpoint

Подайте знак Signed

Дробная длина к 29

. Ваши результаты теперь выглядят подобными следующему изображению.

Нажмите Next, чтобы перейти к странице Clock/Reset Details.

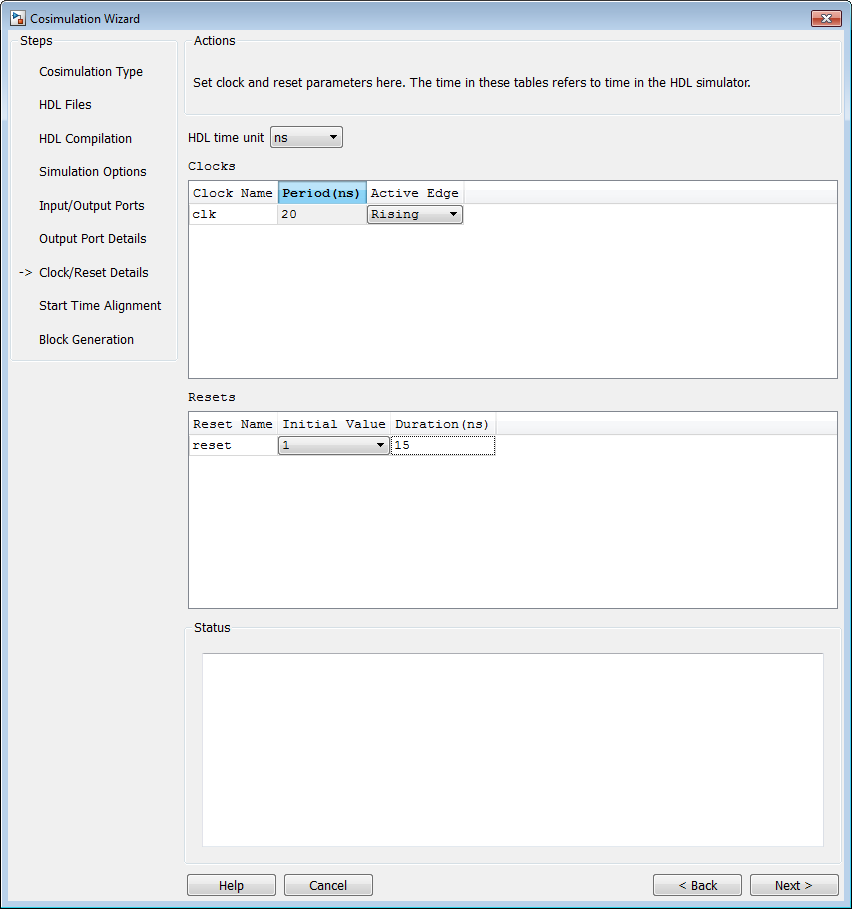

Для этого примера, набор часы Period (ns) к 20. Из кода Verilog вы знаете, что сброс синхронен, и активное значение равняется 1. Можно сбросить целый проект HDL во время 1 нс, инициированный фронтом. Используйте длительность 15 нс для сигнала сброса.

На странице Clock/Reset Details выполните следующие шаги:

Установите период часов на 20.

Оставьте или установите активное ребро на Rising.

Оставьте или установите начальное значение сброса к 1.

Установите длительность сигнала сброса на 15.

Ваши часы и сброс являются теперь тем же самым как теми теми же сигналами, показанными в следующей фигуре.

Нажмите Next, чтобы перейти к странице Start Time Alignment.

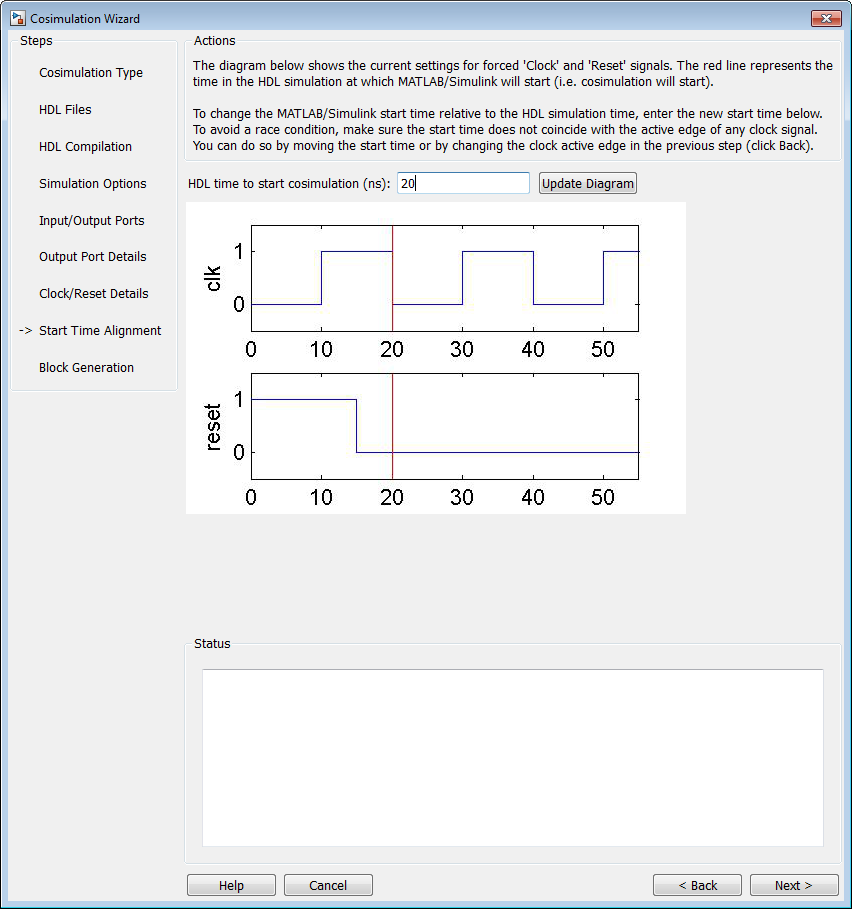

Отображения страницы Выравнивания Времени начала график для форм волны часов и сигналов сброса. Cosimulation Wizard показывает время HDL, чтобы запустить cosimulation с красной линии. Время начала является также временем, в которое Simulink получает первую входную выборку от симулятора HDL.

Установите или подтвердите Выравнивание Времени начала

Активное ребро наших часов является возрастающим ребром. Таким образом, во время 20 нс в симуляторе HDL, зарегистрированный вывод повышенного фильтра косинуса стабилен. Никакое состояние состязания не существует, и время HDL по умолчанию, чтобы запустить cosimulation (20 нс) - то, что мы хотим для этой симуляции. Вы не должны вносить изменения во время начала.

Нажмите Next, чтобы продолжить Блокировать Генерацию.

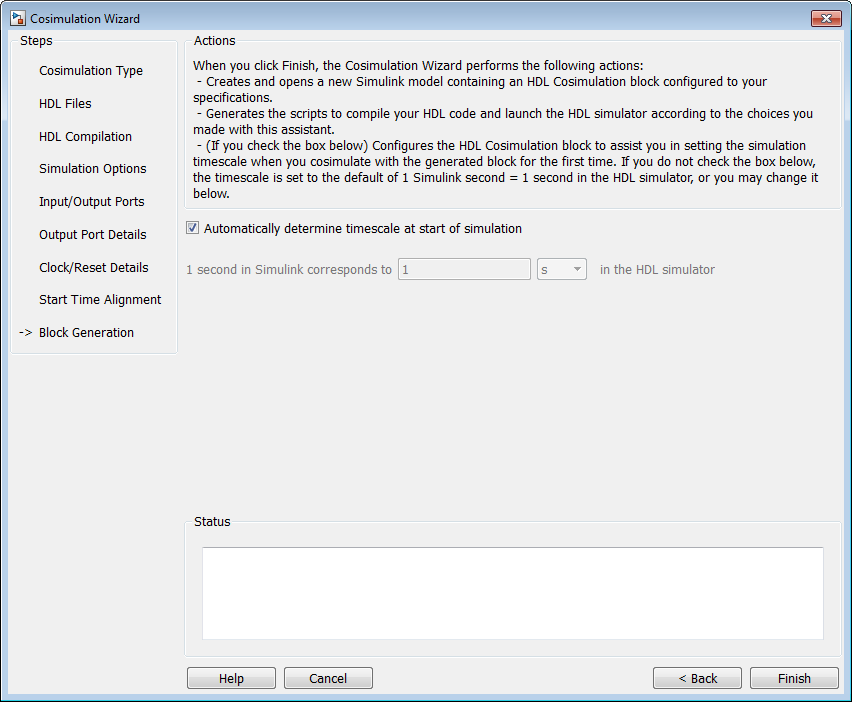

Прежде чем вы сгенерируете блок HDL Cosimulation, у вас есть опция, чтобы определить масштаб времени, прежде чем вы закончите Cosimulation Wizard. Поочередно, можно дать HDL Verifier команду вычислить масштаб времени позже. Вычисление масштаба времени программным обеспечением верификации происходит после того, как вы соедините все порты ввода/вывода сгенерированного блока HDL Cosimulation и запустите симуляцию.

Оставьте Automatically determine timescale at start of simulation выбранным (значение по умолчанию). Позже, у вас будет возможность просмотреть расчетный масштаб времени и изменение, что значение, прежде чем вы начнете симуляцию.

Нажмите Finish, чтобы завершить сеанс Cosimulation Wizard.

Для этого примера вы на самом деле не создаете испытательный стенд. Вместо этого можно найти законченную модель (rcosflt_tb.mdl) в директории, которую вы создали в Примере: Настройте Учебные Файлы (Simulink).

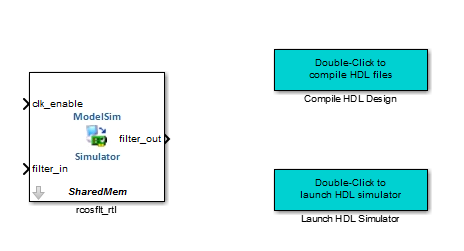

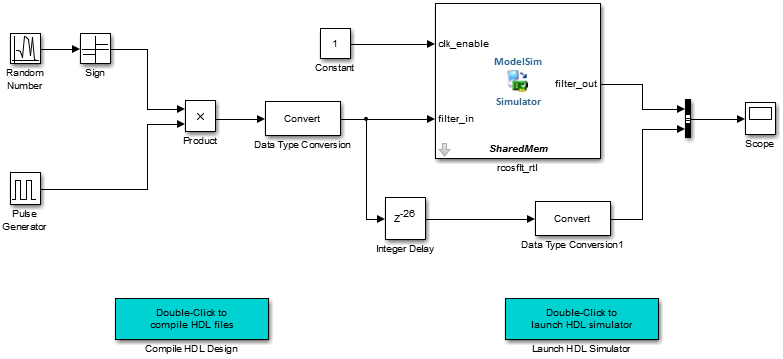

После того, как вы нажмете Finish в Cosimulation Wizard, Simulink создает модель и заполняет ее со следующими элементами:

Блок HDL Cosimulation

Блок, чтобы перекомпилировать проект HDL (содержит ссылку на скрипт, который запускается путем двойного клика по блоку),

Блок, чтобы запустить симулятор HDL (содержит ссылку на скрипт, который запускается путем двойного клика по блоку),

Оставьте модель в настоящий момент и перейдите к следующему шагу.

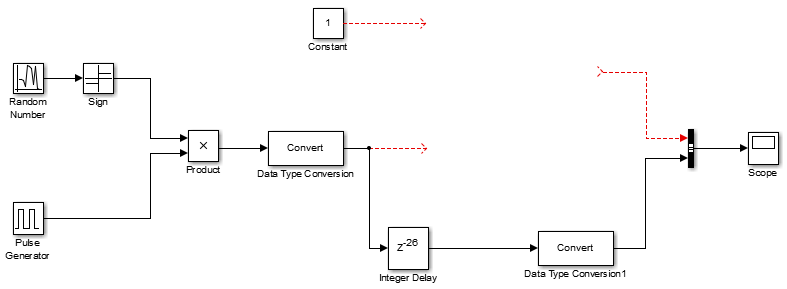

Откройте файл rcosflt_tb, расположенный в директории, которую вы создали в Примере: Настройте Учебные Файлы (Simulink).

Этот файл содержит модель испытательного стенда Simulink. Вы будете использовать этот испытательный стенд, чтобы проверить проект HDL, для которого вы только сгенерировали соответствующий блок HDL Cosimulation.

Добавьте блок HDL Cosimulation в тестовую модель можно следующим образом:

Скопируйте блок HDL Cosimulation от недавно сгенерированной модели до этой тестовой модели.

Поместите блок так, чтобы константа и преобразовала блоки, выстраиваются в линию как входные параметры к блоку HDL Cosimulation и линиям шины, как выведено.

Соедините блоки в испытательном стенде к блоку HDL Cosimulation.

Скопируйте блоки сценария в область ниже испытательного стенда. Ваша модель теперь выглядит подобной этому в следующей фигуре.

Сохраните модель.

Запуститесь симулятор HDL путем двойного клика по блоку маркировал Launch HDL Simulator.

Когда симулятор HDL будет готов, возвратитесь к Simulink и запустите симуляцию.

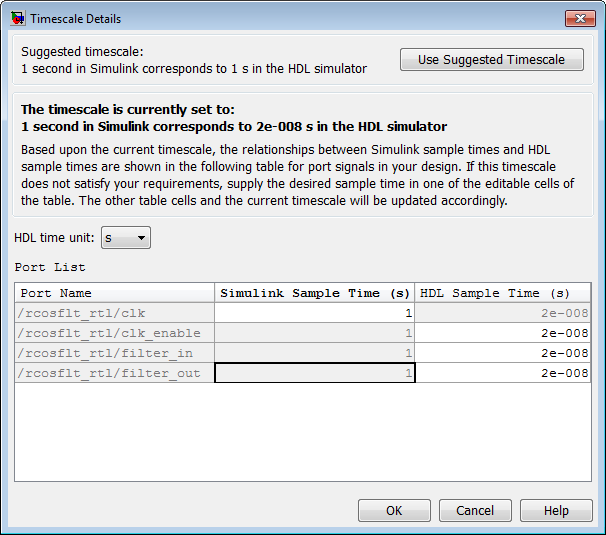

Определите масштаб времени.

Вспомните, что вы выбрали опцию Automatically determine timescale at start of simulation на последней странице Cosimulation Wizard. Поскольку вы сделали так, HDL Verifier запускает графический интерфейс пользователя Деталей Масштаба времени вместо того, чтобы запустить симуляцию.

И симулятор HDL и Simulink выбирают порты filter_in и filter_out в 1 секунду. Однако их шаг расчета в симуляторе HDL должен совпасть с периодом часов (2 нс).

Измените шаг расчета Simulink /rcosflt_rtl/filter_in к 1 (секунды) и нажмите Enter. Мастер затем обновляет таблицу. Следующие данные показывают новый масштаб времени: 1 секунда в Simulink соответствует 2e-008 s в симуляторе HDL.

Нажмите OK, чтобы выйти из Деталей Масштаба времени.

Перезапустите симуляцию.

Проверьте результат осциллографа в тестовой модели. Осциллограф отображает и задержанную версию входа к повышенному фильтру косинуса и что вывод фильтра. Если вы выбираете вывод этого фильтра, вывод непосредственно, нет "предают интерференцию символа земле", происходит

Этот шаг завершает Cosimulation Wizard для использования с примером Simulink.