Целочисленный делитель часов с отношениями на два делителя

Mixed-Signal Blockset / PLL / Стандартные блоки

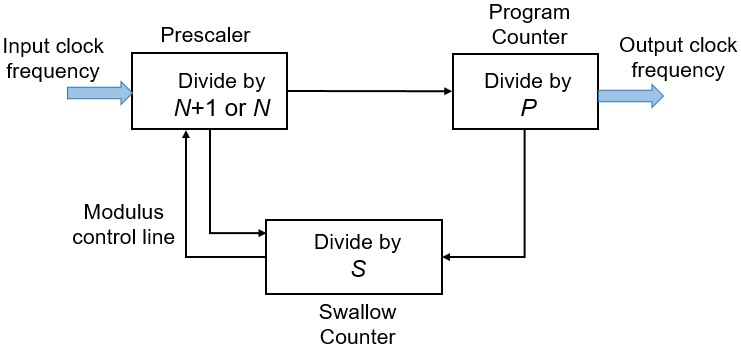

Двойной блок подсистемы Делителя частоты Модуля состоит из счетчика команд, счетчика ласточки и делителя частоты.

Когда блок сначала получает входной сигнал, импульсная функция ласточки активируется. Делитель частоты делит частоту входного сигнала на (N +1), где N задан параметром Prescaler divider value (N). Оба программа и счетчики ласточки начинают рассчитывать. Сбросы счетчика ласточки после подсчета к импульсам S, или (N +1) S циклы, где S задан параметром Swallow counter value (S). Затем импульсная функция ласточки деактивирована, и делитель частоты делит входную частоту на N.

Поскольку счетчик команд уже обнаружил импульсы S, он требует (P-S), чтобы больше импульсов, или (P-S) циклы N достигло переполнения, где P задан параметром Program counter value (P). Повторения цикла после обоих счетчиков сбрасываются.

Эффективное значение делителя двойного делителя частоты модуля является отношением выходной частоты к входной частоте:

Чтобы препятствовать тому, чтобы счетчик команд и делитель частоты сбросили преждевременно перед, счетчик ласточки закончил рассчитывать, условие должен соответствоваться.

Двойной делитель частоты модуля также известен как импульсный делитель ласточки.

[1] Razavi, Behzad. Микроэлектроника РФ. Верхний Сэддл-Ривер, NJ: PTR Prentice Hall, 1998.

Дробный делитель часов с аккумулятором | Дробный делитель часов с DSM | PFD | Один делитель частоты модуля | VCO