В этом примере проекта SoC FPGA генерирует тестовые данные, и обработайте его в алгоритме FPGA прежде, чем передать его процессору с помощью общей памяти.

Откройте новую модель Simulink®. Сохраните модель как soc_hwsw_fpga_sample.slx в подпапку, названную referencedmodels, в папке проекта.

На вкладке Modelling нажмите Model Settings. На the Configuration parameters окне, в панели Hardware Implementation, устанавливает Hardware board на None и набор Device vendor к ASIC/FPGA. В панели Solver, набор Solver selection> Type к Fixed-step. Нажмите OK, чтобы применить изменения и закрыть параметры конфигурации.

Примечание

SoC Blockset™ требует, чтобы образцы модели FPGA задали намеченное оборудование развертывания, в этом случае FPGA.

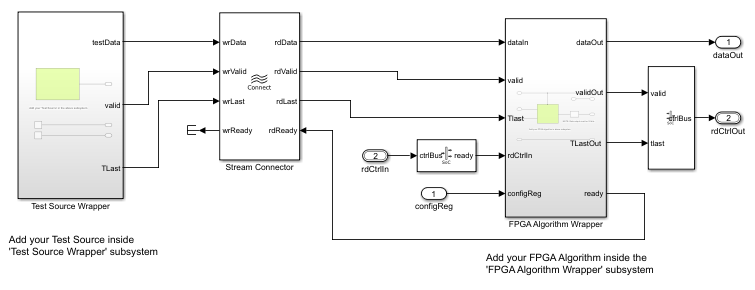

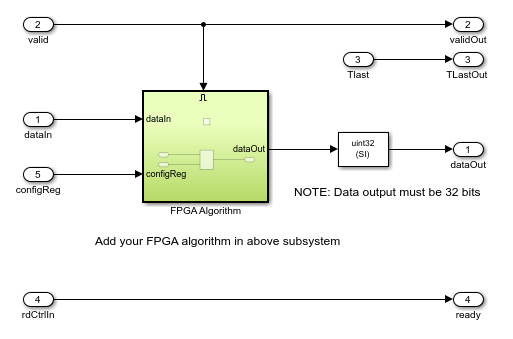

В новой модели, с помощью блока Stream Connector, блока SoC Bus Selector, блок SoC Bus Creator и блоки Subsystem, создают следующую систему.

Примечание

Сигналы для rdCtrlIn и rdCtrlOut должен использовать набор типов сигнала шины для StreamS2MBusObj и StreamM2SBusObj, соответственно.

Совет

Когда ваша модель FPGA включает больше чем один IP, необходимо задать каждый IP как подсистему и соединить подсистемы с помощью блока Stream Connector или Video Stream Connector. Для получения дополнительной информации смотрите Факторы для Нескольких дюйм/с в Модели FPGA.

В диалоговой маске блока SoC Bus Creator, набор Control type к Valid.

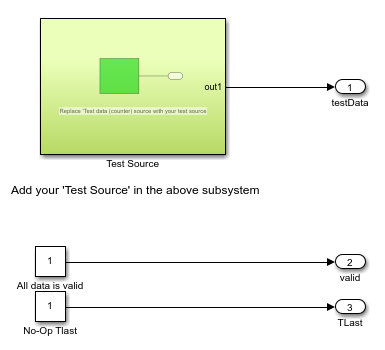

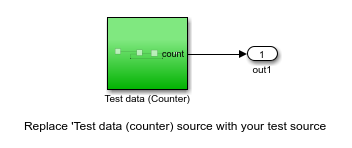

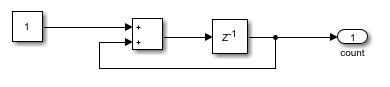

Test Source подсистема симулирует счетчик свободного доступа. Откройте Test Source подсистема и создает следующую систему.

Примечание

Источники, All data is valid и No-Op Tlast, должен произвести сигнал с boolean тип данных.

FPGA Algorithm подсистема симулирует умножение переданных потоком данных. Откройте FPGA Algorithm подсистема и использование Enabled Subsystem, Logical Operator, и блоков Data Type Conversion, создают следующую систему.

Поток от FPGA до Шаблона Процессора, подсистема FPGA использует вариант модели, чтобы выбрать между основанной на выборке моделью, разработанной в этом разделе и основанной на системе координат моделью. Основанная на системе координат модель позволяет более быстрые симуляции, но не поддерживает генерацию кода.

SoC Bus Creator | SoC Bus Selector | Stream Connector