Демодуляция QPSK-модулированных данных

PM, в цифровом поддиапазоне модулирования

Блок основной полосы частот демодулятора QPSK демодулирует сигнал, который был модулирован с использованием способа квадратурной фазовой манипуляции. Вход является представлением модулированного сигнала в основной полосе частот.

Вход должен быть сложным сигналом. Этот блок принимает входной сигнал скалярного вектора или вектора столбца. Сведения о типах данных, поддерживаемых каждым блочным портом, см. в разделе Поддерживаемые типы данных.

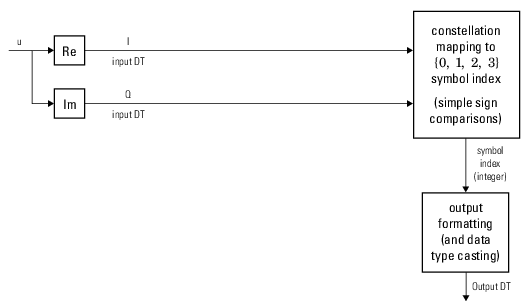

Диаграмма сигналов демодулятора QPSK с жестким решением для тривиального фазового сдвига (нечетное кратное δ/4)

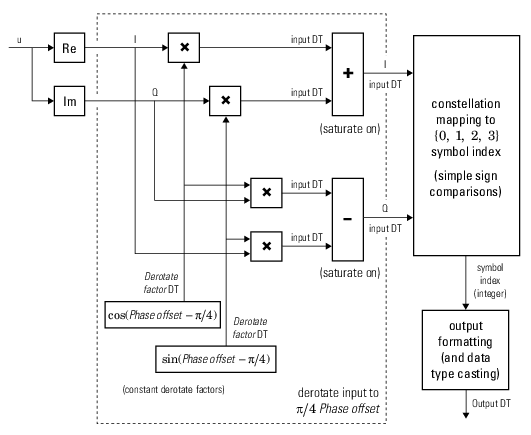

Диаграмма сигнала с плавающей запятой демодулятора QPSK с жестким решением для нетривиального фазового сдвига

Схема сигнала фиксированной точки демодулятора QPSK с жестким решением для нетривиального фазового сдвига

Точный LLR и приблизительный LLR случаи (мягкое решение) описаны в Exact LLR Algorithm и Approximate LLR Algorithm.

Фаза нулевой точки сигнальной совокупности.

Определяет, как блок сопоставляет каждое целое число паре выходных битов.

Определяет, состоят ли выходные данные из целых чисел или битов.

Если для параметра Output type установлено значение Integer и порядок созвездий установлен в Binary, то блок отображает точку

exp (jstart+ jām/2)

к m, где θ - параметр смещения Фазы и m, 0, 1, 2, или 3.

Справочная страница для блока основной полосы частот модулятора QPSK показывает совокупности сигналов для случаев, когда порядок созвездия установлен на Binary или Gray.

Если для типа Output установлено значение Bit, то выход содержит пары двоичных значений, если для типа решения установлено значение Hard decision. Самый значащий бит (т.е. самый левый бит в векторе) - это первый бит, выводимый блоком.

Если для типа решения установлено значение Log-likelihood ratio или Approximate log-likelihood ratio, то выход содержит побитовые значения LLR или приблизительные значения LLR соответственно.

Определяет использование жесткого решения, LLR или приблизительного LLR во время демодуляции. Этот параметр появляется при выборе Bit из выпадающего списка Тип вывода. Выходные значения для типов принятия решений логарифмического отношения правдоподобия и приблизительного логарифмического отношения правдоподобия имеют тот же тип данных, что и входные значения. Для целочисленного вывода блок всегда выполняет демодуляцию жесткого решения.

Подробные сведения об алгоритме см. в разделах Точный алгоритм LLR и Приблизительный алгоритм LLR.

Это поле появляется, когда Approximate log-likelihood ratio или Log-likelihood ratio выбран для типа решения.

Если установлено значение Dialog, дисперсию шума можно задать в поле дисперсии шума. Если установлено значение Portв блоке появляется порт, через который может быть введена дисперсия шума.

Этот параметр появляется, если для источника дисперсии шума установлено значение Dialog и определяет дисперсию шума во входном сигнале. Этот параметр настраивается в обычном режиме, в режиме ускорителя и в режиме ускорителя.

Если для создания исполняемого файла RSIM используется цель Rapid Simulink ® Coder™ (RSIM), можно настроить параметр без повторной компиляции модели. Это полезно при моделировании Монте-Карло, при котором моделирование выполняется несколько раз (возможно, на нескольких компьютерах) с различным уровнем шума.

Алгоритм LLR включает в себя вычисление экспоненций очень больших или очень малых чисел с использованием арифметики конечной точности и дает:

Inf кому -Inf если дисперсия шума очень высока

NaN если дисперсия шума и мощность сигнала очень малы

В таких случаях используйте приблизительное LLR, так как его алгоритм не включает вычисления экспонентов.

Панель типов данных для жесткого решения

Для битовых выходов, если для типа решения установлено значение Hard decision, тип выходных данных может быть установлен в 'Inherit via internal rule', 'Smallest unsigned integer', double, single, int8, uint8, int16, uint16, int32, uint32, или boolean.

Для целочисленных выходов тип выходных данных может быть установлен в 'Inherit via internal rule', 'Smallest unsigned integer', double, single, int8, uint8, int16, uint16, int32, или uint32.

Если для этого параметра установлено значение 'Inherit via internal rule' (установка по умолчанию), блок наследует тип выходных данных из входного порта. Тип выходных данных будет таким же, как и тип входных данных, если входной тип является типом с плавающей запятой (single или double). Если входной тип данных имеет фиксированную точку, то выходной тип данных будет работать так, как если бы для этого параметра было установлено значение 'Smallest unsigned integer'.

Если для этого параметра установлено значение 'Smallest unsigned integer'тип выходных данных выбирается на основе настроек, используемых на панели Аппаратная реализация (Hardware Implementation) диалогового окна Параметры конфигурации (Configuration Parameters) модели.

Если ASIC/FPGA выбран на панели Hardware Implementation, а тип вывода: Bit, тип выходных данных является идеальным минимальным однобитовым размером, т.е. ufix(1). Для всех остальных вариантов выбора это беззнаковое целое число с наименьшей доступной длиной слова, достаточно большой для размещения одного бита, обычно соответствующего размеру символа (например, uint8).

Если ASIC/FPGA выбран на панели Hardware Implementation, а тип вывода: Integer, тип выходных данных является идеальным минимальным двухразрядным размером, т.е. ufix(2). Для всех остальных вариантов выбора это беззнаковое целое число с наименьшей доступной длиной слова, достаточно большой для размещения двух битов, обычно соответствующих размеру символа (например, uint8).

Этот параметр применяется только в том случае, если входной сигнал имеет фиксированную точку, а фазовое смещение не является четным кратным δ/4.

Можно выбрать Same word length as input или Specify word length, в этом случае длина слова определяется с помощью поля ввода.

Панель «Типы данных» для мягкого решения

Для битовых выходов, если для типа решения установлено значение Log-likelihood ratio или Approximate log-likelihood ratio, тип выходных данных наследуется от входных данных (например, если входные данные относятся к типу данных) double, выходные данные также относятся к типу данных double).

| Порт | Поддерживаемые типы данных |

|---|---|

Вход |

|

Вар |

|

Продукция |

|