Некоторые модели требуют знать, сколько времени требуется для того, чтобы данные в одной части модели повлияли на сигнал в другой части модели. Например, при настройке калькулятора частоты ошибок необходимо указать задержку между передатчиком и приемником. Если вы просчитаете задержку, калькулятор частоты ошибок обрабатывает несовпадающие пары данных и, следовательно, возвращает бессмысленный результат.

Этот раздел иллюстрирует вычисление задержек в многоскоростных моделях и в моделях, где полная задержка в последовательности блоков содержит множественные задержки из отдельных блоков. В этом разделе также показано, как использовать блоки Найти задержку (Find Delay) и Задержка (Delay), чтобы помочь справиться с задержками в модели.

В других частях этого набора документации также обсуждаются задержки. Для получения информации о работе с задержками или о задержках в определенных типах блоков см.

Страница ссылки на блок «Найти задержку»

Страница ссылки на блок задержки

Справочная страница блока декодера Витерби

Страница ссылок на блоки Дерепеата

Для обсуждения задержек в более простых примерах, чем в данном разделе, см.

В то время как некоторые блоки могут определять свое текущее выходное значение, используя только текущее входное значение, другим блокам необходимы входные значения из нескольких временных шагов для вычисления текущего выходного значения. В последней ситуации блок несет задержку. Примером этого случая является случай, когда блок Дерепеата должен усреднить пять выборок из скалярного сигнала. Блок должен отложить вычисление среднего значения до тех пор, пока не получит все пять выборок.

В целом задержки в модели могут происходить из различных источников:

Цифровые демодуляторы

Сверточные перемежители или обращенные перемежители

Уравнители

Блок декодера Витерби

Буферизация, понижающая дискретизация, прерывание и аналогичные операции с сигналами

Явные блоки задержки, такие как задержка и переменная целочисленная задержка

Фильтры

Ниже рассматриваются некоторые из этих причин задержки.

В этом разделе рассматривается пример 256-Channel ADSL и показано, как вычислить правильное значение параметра задержки приема в одном из блоков вычисления частоты ошибок в модели. Модель включает в себя задержки от сверточного перемежения и явный блок задержки. Для открытия примера модели ADSL введите commadsl в командной строке MATLAB.

В примере ADSL данные следуют по одному из двух параллельных трактов, один с ненулевой задержкой, а другой с нулевой задержкой. Один тракт включает в себя сверточный перемежитель и обращенный перемежитель, в то время как другой делает это. Рядом с концом каждого тракта находится блок вычисления частоты ошибок, параметр задержки приема которого должен отражать задержку данного тракта. В остальном обсуждение делает наблюдение о периодах кадра в модели, а затем рассматривает путь для перемежающихся данных.

Прежде чем искать отдельные задержки, сначала обратите внимание, что большинство сигнальных линий в модели имеют одинаковый период кадра. На вкладке «Отладка» разверните узел «Информационные наложения». В разделе «Образец времени» выберите «Цвета». Эта опция цветит блоки и сигналы в соответствии с периодами их кадров (или периодами выборки, в случае сигналов на основе выборок). Все сигнальные линии на верхнем уровне модели имеют одинаковый цвет, что означает, что они имеют одинаковый период кадра. Как следствие, кадры являются удобным блоком для измерения задержек в блоках, которые обрабатывают эти сигналы. При вычислении суммарной задержки по маршруту средневзвешенное значение (количества кадров, взвешенного по периоду каждого кадра) уменьшается до суммы.

В передающей части модели чередующийся тракт представляет собой нижнюю ветвь, показанную ниже желтым цветом. Аналогично, перемежающийся тракт в приемной части модели является нижней ветвью. Рядом с концом чередующегося пути находится блок вычисления частоты ошибок, который вычисляет значение, обозначенное Interleaved BER.

В следующей таблице суммированы задержки в тракте для данных без перемежения. Последующие параграфы более подробно объясняют задержки и объясняют, почему общая задержка относительно блока вычисления частоты ошибок составляет один кадр или 776 выборок.

| Блок | Задержка в выходных выборках из отдельного блока | Задержка, в кадрах | Задержка в блоке вычисления частоты ошибок входных выборок |

|---|---|---|---|

| Пара сверточного перемежителя и сверточного обращенного перемежителя | 40 | 1 (комбинированный) | 776 (комбинированный) |

| Задержка | 800 | ||

| Общее количество | Н/Д | 1 | 776 |

Перемежение. В отличие от пути без перемежения, путь с перемежением содержит блок сверточного перемежителя в передатчике и блок сверточного обращенного перемежителя в приемнике. Задержка пары перемежитель/обращенный перемежитель является произведением параметра Rows of shift regisers, параметра Register length step и на единицу меньше параметра Rows of shift regisers. В этом случае задержка пары перемежитель/обращенный перемежитель оказывается 5 * 2 * 4 = 40 выборок.

Блок задержки. Приемная часть перемеженного тракта также содержит блок задержки. Этот блок явно вызывает задержку в 800 выборок, имеющих то же время выборки, что и 40 выборок задержки из пары перемежитель/обращенный перемежитель. Следовательно, полная задержка от перемежения, обращенного перемежения и явной задержки составляет 840 выборок. Эти 840 выборок составляют один кадр данных, выходящих из блока задержки.

Суммирование задержек. Никакие другие блоки в перемежающемся тракте примера не вызывают каких-либо задержек. Сложение задержек из пары перемежитель/обращенный перемежитель и блока задержки указывает, что полная задержка в перемеженном тракте является одним кадром.

Общая задержка относительно блока вычисления частоты ошибок. Блок вычисления частоты ошибок, который вычисляет значение с меткой Interleaved BER требуется значение параметра задержки приема, эквивалентное одному кадру. Параметр задержки приема измеряется в выборках, и каждый входной кадр в блок вычисления частоты ошибок содержит 776 выборок. Кроме того, частота кадров на выходных портах всех блоков, вызывающих задержку, в перемежающемся тракте равна частоте кадров на входе блока вычисления частоты ошибок. Поэтому правильным значением параметра задержки приема является 776 образцы.

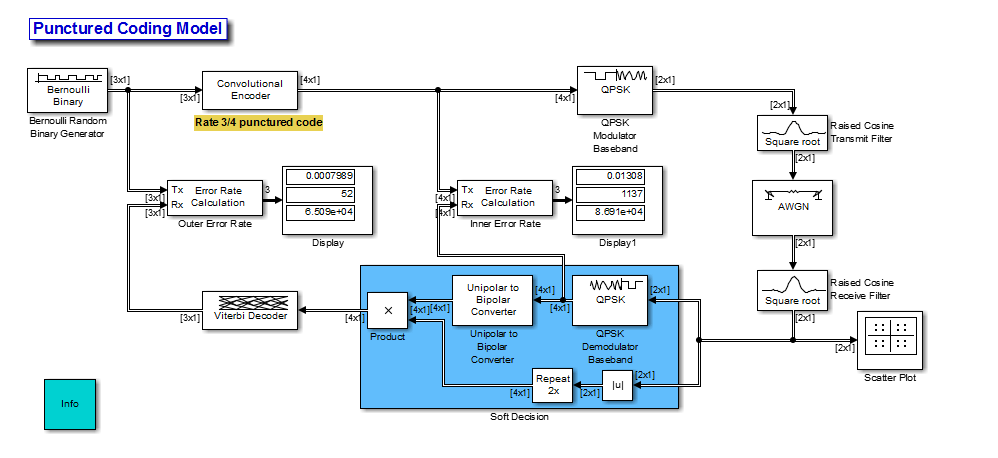

В этом разделе рассматривается модель проколотого кодирования, которая включает в себя задержки от декодирования, понижающей дискретизации и фильтрации. Два блока вычисления частоты ошибок в модели работают правильно, если и только если их параметры задержки получения точно отражают задержки в модели. Для открытия модели введите doc_punct в командной строке MATLAB.

Перед поиском отдельных задержек, если панель Timing Legend еще не открыта, на вкладке Debug разверните Information Overlays. В разделе «Образец времени» выберите «Легенда». На панели Легенда синхронизации (Timing Legend) > Выделить (Highlight) > Все (All). Только крайняя правая часть модели отличается по цвету от остальной части модели. Это означает, что все сигналы и блоки в модели, за исключением сигналов в крайнем правом крае, имеют одинаковый период кадра. Следовательно, кадры с этой преобладающей частотой кадров являются удобной единицей для измерения задержек в блоках, которые обрабатывают эти сигналы. При вычислении суммарной задержки по маршруту средневзвешенное значение (количества кадров, взвешенного по периоду каждого кадра) уменьшается до суммы.

Желтые блоки представляют многоскоростные системы, в то время как блок канала AWGN работает с более высокой частотой кадров, чем все остальные блоки в модели.

Блок с именем Внутренняя частота ошибок (Inner Error Rate), расположенный рядом с центром модели, является копией блока Расчет частоты ошибок (Error Rate Calculation) из библиотеки приемников сообщений. Он вычисляет частоту битовых ошибок для части модели, которая исключает проколотый сверточный код. В части модели между двумя входными сигналами этого блока задержки поступают от фильтра передачи и фильтра приема. В этом разделе объясняется, почему параметр «Задержка получения» блока «Частота внутренних ошибок» является общим значением задержки, равным 16.

Блок фильтра передачи. Блок с меткой Tx Filter является копией блока Raised Cosine Transmit Filter. Он интерполирует входной сигнал на коэффициент 8 и применяет фильтр возведения косинуса квадратного корня. Значение параметра Filter в символах блока равно 6, что означает, что его групповая задержка равна 3 символам. Поскольку частота дискретизации этого блока увеличивается от входного порта к выходному порту, он должен выводить начальный кадр нулей в начале моделирования. Поскольку размер входного кадра равен 2, общая задержка блока составляет 2 + 3 = 5 символов. Это соответствует 5 выборкам на входном порту блока.

Блок фильтра приема. Блок с меткой Rx Filter является копией блока Raised Cosine Receive Filter. Он прореживает свой входной сигнал в 8 раз и применяет другой фильтр косинуса с квадратным корнем. Значение параметра Filter в символах этого блока равно 6, что означает, что его групповая задержка равна 3 символам. На выходе блока 3 символа соответствуют 3 выборкам.

Блок демодулятора QPSK. Блок, обозначенный как базовая полоса демодулятора QPSK, принимает комплексные сигналы QPSK и выводит 2 бита для каждого комплексного входа. Это преобразование в выходные биты удваивает накопленную задержку на входе блока.

Суммирование задержек. Никакие другие блоки в части модели между двумя входными сигналами внутреннего блока частоты ошибок не вызывают каких-либо задержек. Общая задержка тогда (2 + 3 + 3) * 2 = 16 образцы. Это значение можно использовать в качестве параметра задержки приема во внутреннем блоке частоты ошибок.

Блок с именем «Частота внешних ошибок», расположенный слева от модели, является копией блока «Расчет частоты ошибок» из библиотеки «Приемники сообщений». Он вычисляет частоту битовых ошибок для всей модели, включая проколотый сверточный код. Задержки поступают из блоков Tx Filter, Rx Filter и Viterbi Decoder. В этом разделе объясняется, почему параметр Receive delay блока External Error Rate является общим значением задержки, равным 108.

Фильтр и блоки понижающей дискретизации. Блоки Tx Filter, Rx Filter и Downsample имеют суммарную задержку 16 выборок. Дополнительные сведения см. в разделе Внутренний блок частоты ошибок.

Блок декодера Витерби. Поскольку блок декодера Витерби декодирует скорость 3/4 проколотый код, он фактически уменьшает задержку, наблюдаемую на его входе. Это сокращение приводится как 16 * 3/4 = 12 образцы.

Блок декодера Витерби декодирует сверточный код, и использование алгоритмом пути отслеживания вызывает задержку. Блок обрабатывает сигнал на основе кадра и имеет режим работы, равный Continuous. Следовательно, задержка, измеренная в выходных выборках, равна значению параметра глубины Traceback, равному 96. (Величина задержки указана на справочной странице для блока декодера Витерби.) Поскольку выходной сигнал блока декодера Витерби является точно одним из входных сигналов блока частоты внешних ошибок, проще рассматривать задержку как 96 выборок, чем преобразовывать ее в эквивалентное количество кадров.

Общая задержка относительно блока частоты внешних ошибок. Для блока «Частота внешних ошибок» требуется значение параметра задержки приема, которое является суммой всех задержек в системе. Эта общая задержка составляет 12 + 96 = 108 образцы.

Предшествующие обсуждения объяснили, почему определенные блоки вычисления частоты ошибок в моделях имели конкретные значения параметров задержки приема. Вы могли прийти к этим числам независимо, используя блок Найти задержку. В этом разделе объясняется, как найти задержку сигнала с помощью примерной модели ADSL. commadsl, в качестве примера. Применение метода к примеру проколотого сверточного кодирования, обсуждаемого в модели проколотого кодирования, было бы аналогичным.

Из тракта для перемеженных данных следует, что задержка в тракте для перемеженных данных составляет 776 выборок. Чтобы блок «Найти задержку» рассчитал это значение, выполните следующие действия.

Вставка блока «Найти задержку» и блока «Отображение» в модель рядом с блоком «Расчет частоты ошибок», в котором вычисляется значение с меткой Interleaved BER.

Подключите блоки, как показано ниже.

Установите для параметра длины окна корреляции блока «Найти задержку» значение, существенно превышающее 776, например 2000.

Примечание

Необходимо использовать достаточно большую длину окна корреляции, иначе значения, создаваемые блоком задержки поиска, не стабилизируются при правильном значении.

Запустите моделирование.

Новый блок отображения теперь показывает значение 776, как и ожидалось.

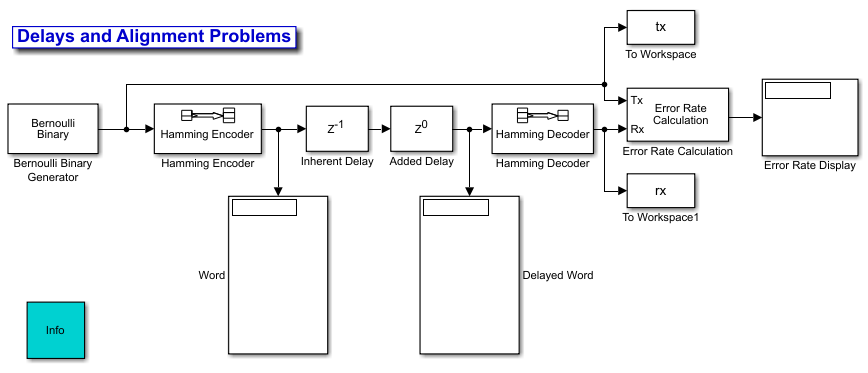

Задержки и проблемы выравнивания. Некоторые модели требуют не только вычислять задержки, но и манипулировать ими. Например, если модель несет задержку между блочным кодером и его соответствующим декодером, декодер может неправильно интерпретировать границы между кодовыми словами, которые он принимает, и, следовательно, возвращать бессмысленные результаты. В более общем случае такая ситуация может возникнуть, когда путь между парными компонентами блочно-ориентированной операции (такой как перемежение, блочное кодирование или преобразования бит в целое) включает в себя операцию, вызывающую задержку (такую как те, которые перечислены в источниках задержек).

Чтобы избежать этой проблемы, можно вставить дополнительную задержку соответствующей величины между кодером и декодером. Если модель также вычисляет частоту ошибок, то дополнительная задержка влияет на этот процесс, как описано в разделе Задержки. В этом разделе используются примеры, иллюстрирующие цель, методы и последствия манипулирования задержками в различных обстоятельствах.

Этот раздел иллюстрирует чувствительность блочно-ориентированных операций к задержкам, используя небольшую модель, которая направлена на фиксацию сути проблемы в простой форме. Откройте модель путем ввода doc_alignment в командной строке MATLAB ®. Затем выполните моделирование таким образом, чтобы в блоках просмотра отображались соответствующие значения.

В этой модели два блока кодирования создают и декодируют блочный код. Две копии блока задержки создают задержку между кодером и декодером. Два блока задержки имеют разные цели в этой иллюстративной модели:

Блок внутренней задержки представляет любые блоки, вызывающие задержку, которые могут возникнуть в модели между кодером и декодером. Список возможностей, которые могут возникнуть в более реалистичной модели, см. в разделе Источники задержек.

Блок «Добавленная задержка» представляет собой явную задержку, вставляемую для получения соответствующей величины суммарной задержки между кодером и декодером. Например, commadsl модель содержит блок задержки, который служит для этой цели.

Наблюдение за проблемой. По умолчанию для параметров задержки в блоках «Внутренняя задержка» и «Добавленная задержка» установлено значение 1 и 0соответственно. Это представляет ситуацию, в которой некоторая операция вызывает однобитовую задержку между кодером и декодером, но вы еще не пытались ее компенсировать. Общая задержка между кодером и декодером составляет один бит. Из блоков Word и Delayed Word видно, что кодовое слово, которое выходит из кодера, сдвигается вниз на один бит к моменту его поступления в декодер. Декодер принимает сигнал, в котором граница кодового слова находится во втором бите кадра, вместо совпадения с началом кадра. То есть кодовые слова и кадры, которые их содержат, не выровнены друг с другом.

Эта несогласованность является проблематичной, поскольку блок декодера Хэмминга предполагает, что каждый кадр начинает новое кодовое слово. В результате он пытается декодировать слово, которое состоит из последнего бита одного выходного кадра из кодера, за которым следуют первые шесть битов следующего выходного кадра из кодера. Из блока отображения частоты ошибок видно, что частота ошибок в этой операции декодирования близка к 1/2. То есть декодер редко правильно восстанавливает исходное сообщение.

Чтобы использовать аналогию, предположим, кто-то развращает абзац прозы, перемещая каждый символ периода из конца предложения в конец первого слова следующего предложения. Если вы пытаетесь прочитать такой абзац, предполагая, что новое предложение начинается через некоторое время, вы неправильно понимаете начало и конец каждого предложения. В результате вы можете не понять значение абзаца.

Чтобы увидеть, как задержки различных величин влияют на производительность декодера, измените значения параметра Delay в блоке Added Delay и параметра Receive delay в блоке Error Rate Calculation, а затем снова запустите моделирование. Многие комбинации значений параметров приводят к коэффициентам ошибок, близким к 1/2. Кроме того, при проверке переданных и полученных данных путем ввода

[tx rx]

в командной строке MATLAB может отсутствовать какая-либо корреляция между переданными и полученными данными.

Исправление задержек

Некоторые комбинации значений параметров приводят к нулевым коэффициентам ошибок, поскольку задержки являются подходящими для системы. Например:

В блоке «Добавленная задержка» установите значение «Задержка». 6.

В блоке «Расчет частоты ошибок» установите для параметра «Задержка получения» значение 4.

Запустите моделирование.

Войти [tx rx] в командной строке MATLAB.

Верхний номер в блоке отображения частоты ошибок показывает, что частота ошибок равна нулю. Декодер правильно восстановил каждое переданное сообщение. Однако блоки Word и Displayed Word не отображают совпадающих значений. Не сразу ясно, как выход кодера и вход декодера связаны друг с другом. Для уточнения вопроса проверьте выходные данные в окне команд MATLAB. Последовательность вдоль первого столбца (tx) появляется во втором столбце (rx) через четыре строки. Для подтверждения введите

isequal(tx(1:end-4),rx(5:end))

в командной строке MATLAB и убедитесь, что результат 1 Правда. Эта последняя команда проверяет соответствие первого столбца смещенной версии второго столбца. Смещение вектора MATLAB rx на четыре строки соответствует поведению блока вычисления частоты ошибок, если для его параметра задержки получения установлено значение 4.

Таким образом, эти специальные значения параметров задержки и задержки получения работают по следующим причинам:

В сочетании блоки «внутренняя задержка» и «добавленная задержка» задерживают кодированный сигнал на полное кодовое слово, а не на частичное кодовое слово. Таким образом, декодер является правильным в своем предположении, что граница кодового слова падает в начале входного кадра и правильно декодирует слова. Однако задержка в кодированном сигнале заставляет каждое восстановленное сообщение появляться на одно слово позже, то есть на четыре бита позже.

Блок вычисления частоты ошибок компенсирует однословную задержку в системе путем сравнения каждого слова передаваемого сигнала с данными на четыре бита позже в принятом сигнале. Таким образом, он правильно делает вывод, что частота ошибок декодера равна нулю.

Примечание

Это не единственные значения параметров, которые приводят к нулевым коэффициентам ошибок. Так как код в этой модели представляет собой (7, 4) блочный код, а внутреннее значение задержки равно 1, можно установить параметры задержки задержки на 7k-1 и 4k соответственно для любого положительного целого числа k. Важно, чтобы сумма собственной задержки (1) и добавленной задержки (7k-1) была кратной длине кодового слова (7).

Выравнивание слов блочного кода. Пример ADSL, обсуждаемый в примере модели ADSL, иллюстрирует необходимость манипулирования задержкой в модели так, чтобы каждый кадр данных, который входит в блочный декодер, имел границу кодового слова в начале кадра. Необходимость возникает потому, что путь между блочным кодером и блочным декодером включает в себя операцию сверточного перемежения, вызывающую задержку. В этом разделе объясняется, почему модель использует блок задержки для управления задержкой между сверточным обращенным перемежителем и блочным декодером, и почему блок задержки сконфигурирован как есть. Для открытия примера модели ADSL введите commadsl в командной строке MATLAB.

Несоответствие кодовых слов

В примере ADSL блоки сверточного перемежителя и сверточного обращенного перемежителя появляются после подсистем Scrambler & FEC, но перед подсистемами Descrambler & FEC. Эти две подсистемы содержат блоки, которые выполняют кодирование Рида-Соломона, и блоки кодирования ожидают, что каждый кадр входных данных начнется с нового слова, а не в середине слова.

Как обсуждалось в тракте для перемеженных данных, задержка пары перемежитель/обращенный перемежитель составляет 40 выборок. Однако вход в подсистему дескремблера и FEC является кадром размера 840, а 40 не кратным 840. Следовательно, сигнал, который выходит из блока сверточного обращенного перемежителя, является кадром, первая запись которого не представляет начало нового кодового слова. Как описано в разделе «Наблюдение за проблемой», это несоответствие между кодовыми словами и кадрами, которые их содержат, препятствует правильному декодированию декодера.

Вставка задержки для исправления выравнивания

Пример ADSL решает проблему, перемещая границу слова от 41-й выборки кадра из 840 выборок к первой выборке последовательного кадра. Перемещение границы слова эквивалентно задержке сигнала. С этой целью в примере содержится блок задержки между блоком сверточного обращенного перемежителя и подсистемой дескремблера и FEC.

Параметр Delay в блоке Delay имеет значение 800 потому что это минимальное количество выборок, необходимое для сдвига 41-й выборки одного кадра 840 выборок в первую выборку следующего кадра 840 выборок. Другими словами, сумма собственной задержки 40 выборок (из процесса перемежения/обращенного перемежения) и искусственной задержки 800 выборок является полным кадром данных, а не частичным кадром.

Эта задержка в 800 выборок имеет значение для других частей модели, а именно для параметра задержки приема в одном из блоков вычисления частоты ошибок. Дополнительные сведения о том, как задержка влияет на значение этого параметра, см. в разделе Путь для перемежающихся данных.

Использование блока задержки поиска

Предшествующее обсуждение объяснило, почему 800-отсчетная задержка необходима для исправления рассогласования между кодовыми словами и кадрами, которые их содержат. Зная, что подсистема Descrambler & FEC требует, чтобы границы кадра возникали на границах слов, можно было независимо получить число 800, используя блок задержки поиска. Используйте следующую процедуру:

Вставьте в модель блок задержки поиска и блок отображения.

Создайте линию ответвления, соединяющую вход блока сверточного перемежителя с sRef вход блока «Задержка поиска».

Создайте другую линию ответвления, соединяющую выход блока сверточного обращенного перемежителя с sDel вход блока «Задержка поиска».

Подключите delay вывод блока задержки поиска в новый блок отображения. Измененная часть модели теперь выглядит следующим образом (на котором также показаны тени на ключевых блоках, чтобы подчеркнуть изменения).

Отображение размеров каждого сигнала в модели. На вкладке «Отладка» разверните узел «Информационные наложения». В разделе «Сигналы» выберите «Размеры сигнала».

Запустите моделирование.

Новый блок отображения теперь показывает значение 40. Кроме того, отображение размеров сигнала показывает, что выходной сигнал блока сверточного обращенного перемежителя представляет собой кадр длиной 840. Эти результаты показывают, что последовательность блоков между сверточным перемежителем и сверточным обращенным перемежителем, включительно, задерживает кадр из 840 выборок на 40 выборок. Дополнительная задержка в 800 выборок доводит общую задержку до 840. Поскольку общая задержка теперь кратна длине кадра, задержанные обращенно перемеженные данные могут быть декодированы.

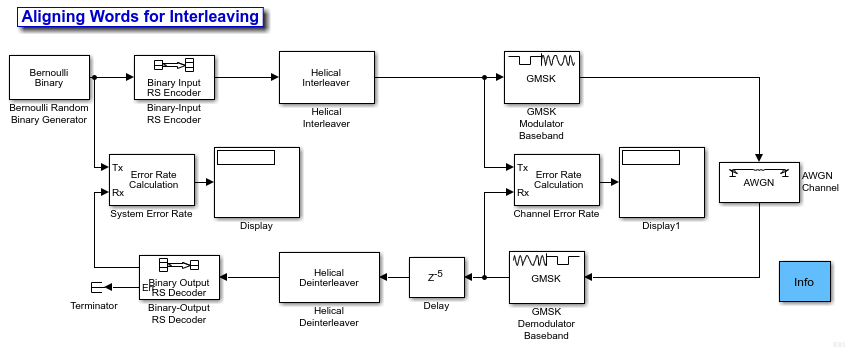

Выравнивание слов для перемежения. В этом разделе описан пример, который манипулирует задержкой перед обращенным перемежителем, поскольку путь между перемежителем и обращенным перемежителем включает задержку от демодуляции. Для открытия модели введите doc_gmskint в командной строке MATLAB.

Модель включает в себя блочное кодирование, спиральное перемежение и модуляцию GMSK. В таблице ниже суммированы отдельные задержки блоков в модели.

| Блок | Задержка в выходных выборках из отдельного блока | Ссылка |

|---|---|---|

| Модулирующая полоса демодулятора GMSK | 16 | Задержки цифровой модуляции |

| Спиральный обращенный перемежитель | 42 | Задержки сверточных перемежителей |

| Задержка | 5 | Страница ссылки на задержку |

Несоответствие чередующихся слов

Процесс демодуляции в этой модели вызывает задержку между перемежителем и обращенным перемежителем. Поскольку обращенный перемежитель ожидает, что каждый кадр входных данных начнется с нового слова, важно гарантировать, что полная задержка между перемежителем и обращенным перемежителем включает в себя один или более полных кадров, но не частичные кадры.

Задержка демодулятора составляет 16 выходных выборок. Однако вход в блок спирального обращенного перемежителя является кадром размера 21, а 16 не кратным 21. Следовательно, сигнал, который выходит из блока основной полосы частот демодулятора GMSK, является кадром, первая запись которого не представляет начало нового слова. Как описано в разделе «Наблюдение за проблемой», это несоответствие между словами и кадрами, которые их содержат, препятствует обратному перемежителю.

Вставка задержки для исправления выравнивания

Модель перемещает границу слова из 17-го образца 21-образного кадра в первый образец следующего кадра. Перемещение границы слова эквивалентно задержке сигнала на пять выборок. Блок задержки между блоком основной полосы частот демодулятора GMSK и блоком спирального обращенного перемежителя выполняет такую задержку. Для блока задержки установлен параметр Delay 5.

Комбинируя эффекты демодулятора и блока задержки, полная задержка между перемежителем и обращенным перемежителем является полным кадром данных с 21 выборкой, а не частичным кадром.

Проверка выравнивания кодовых слов блоков

Перемежитель и обращенный перемежитель вызывают комбинированную задержку из 42 выборок, измеренных на выходе из блока спирального обращенного перемежителя. Поскольку задержанный выходной сигнал от обращенного перемежителя идет рядом с декодером Рида-Соломона, и поскольку декодер ожидает, что каждый кадр входных данных начнется с нового слова, важно гарантировать, что полная задержка между кодером и декодером включает в себя один или более полных кадров, но не частичные кадры.

В этом случае задержка 42 выборок составляет ровно два кадра. Поэтому нет необходимости вставлять блок задержки между блоком спирального обращенного перемежителя и блоком двоичного выходного RS-декодера.

Вычислительные задержки для настройки блоков вычисления частоты ошибок

Модель содержит два блока «Расчет частоты ошибок» с метками «Частота ошибок канала» и «Частота системных ошибок». Каждый из этих блоков имеет параметр задержки приема, который должен отражать задержку тракта между блоками Tx и Rx сигналы. В следующей таблице поясняются значения задержки приема в двух блоках.

| Блок | Значение задержки получения | Причина |

|---|---|---|

| Частота ошибок канала | 16

| Задержка блока основной полосы частот демодулятора GMSK в отсчетах |

| Частота системных ошибок | 15*3

| Три кадра из пятнадцати выборок: один кадр из блоков основной полосы частот и задержки демодулятора GMSK и два кадра из пары перемежитель/обращенный перемежитель |

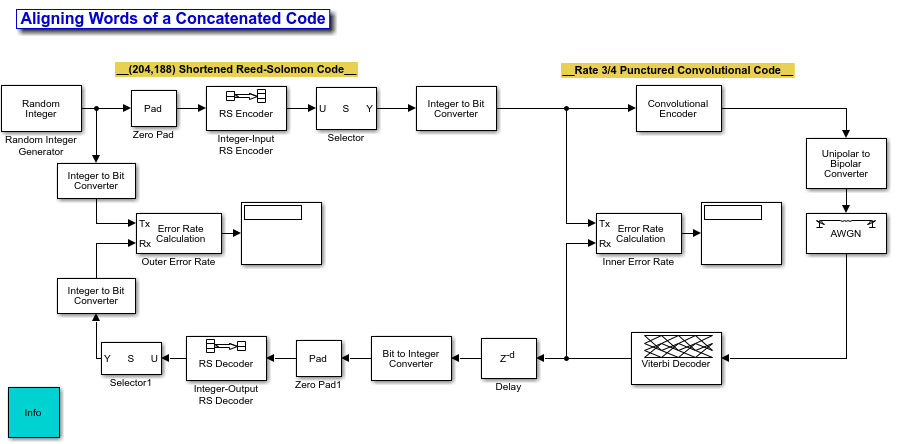

Выравнивание слов конкатенированного кода. Этот раздел описывает пример, который манипулирует задержкой между двумя частями кодового декодера с конкатенацией, поскольку первая часть включает в себя задержку от декодирования Витерби, в то время как вторая часть ожидает, что границы кадра будут совпадать с границами слов. Для открытия модели введите doc_concat в командной строке MATLAB. Он использует блочный и сверточный коды из commdvbt пример, но значительно упрощает общую конструкцию.

Модель включает в себя укороченный блочный код и проколотый сверточный код. Все сигналы и блоки в модели имеют одинаковый период кадра. В следующей таблице представлены задержки отдельных блоков в модели.

| Блок | Задержка в выходных выборках из отдельного блока |

|---|---|

| Декодер Витерби | 136 |

| Задержка | 1496 (то есть 1632 - 136) |

Несоответствие кодовых слов блоков

Процесс декодирования Витерби в этой модели вызывает задержку между блоком преобразования целочисленных в битовые и блоком преобразования битовых в целочисленные. Поскольку последний блок ожидает, что каждый кадр входных данных начнется с нового 8-битового слова, важно гарантировать, что полная задержка между двумя блоками преобразователя включает в себя один или более полных кадров, но не частичные кадры.

Задержка блока декодера Витерби составляет 136 выходных выборок. Однако вход в блок преобразования битов в целое представляет собой кадр размера 1632. Следовательно, сигнал, который выходит из блока декодера Витерби, является кадром, первая запись которого не представляет начало нового слова. Как описано в разделе «Наблюдение за проблемой», это несоответствие между словами и кадрами, которые их содержат, препятствует блоку преобразователя.

Примечание

Внешний декодер в этой модели (декодер RS с целочисленным выходом) также ожидает, что каждый кадр входных данных начнется с нового кодового слова. Поэтому проблема несовпадения в этой модели влияет на многие проекты конкатенированных кодов, а не только на те, которые преобразуются между двоичными и целочисленными сигналами.

Вставка задержки для исправления выравнивания

Модель перемещает границу слова из 137-й выборки кадра 1632-образной выборки в первую выборку следующего кадра. Перемещение границы слова эквивалентно задержке сигнала на 1632-136 выборок. Блок задержки между блоком декодера Витерби и блоком преобразования битов в целое выполняет такую задержку. Для блока задержки установлен параметр Delay 1496.

Комбинируя эффекты блока декодера Витерби и блока задержки, полная задержка между перемежителем и обращенным перемежителем является полным кадром данных из 1632 выборок, а не частичным кадром.

Вычислительные задержки для настройки блоков вычисления частоты ошибок

Модель содержит два блока «Расчет частоты ошибок», помеченных как «Внутренняя частота ошибок» и «Внешняя частота ошибок». Каждый из этих блоков имеет параметр задержки приема, который должен отражать задержку тракта между блоками Tx и Rx сигналы. В таблице ниже поясняются значения задержки приема в двух блоках.

| Блок | Значение задержки получения | Причина |

|---|---|---|

| Частота внутренних ошибок | 136

| Задержка блока декодера Витерби в выборках |

| Частота внешних ошибок | 1504 (188*8 bits) | Один кадр из 188 выборок, из комбинации собственной задержки блока декодера Витерби и добавленной задержки блока задержки |

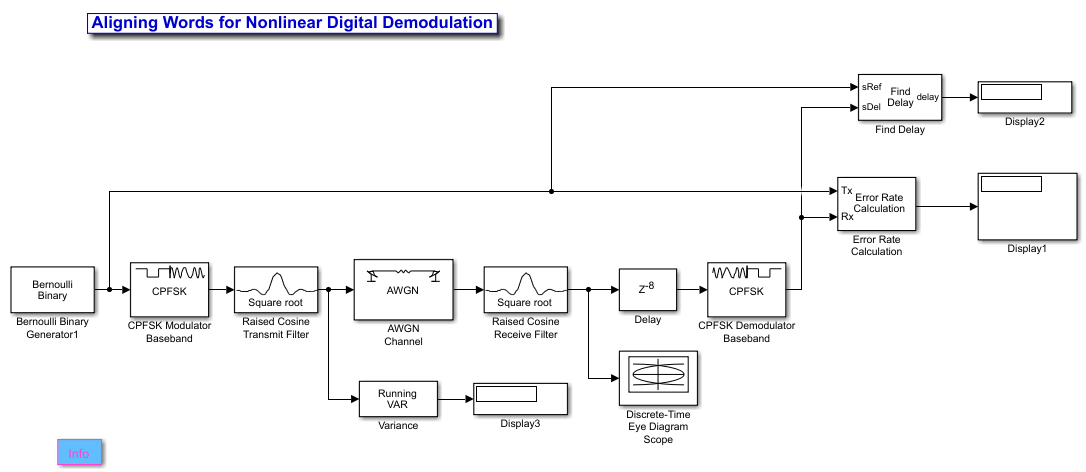

Выравнивание слов для нелинейной цифровой демодуляции. Этот пример манипулирует задержкой для получения правильной символьной синхронизации сигнала, так что границы символов правильно выравниваются до того, как происходит демодуляция.

Чтобы открыть эту модель, введите doc_nonlinear_digital_demod в командной строке MATLAB.

Эта модель включает в себя схему модуляции CPFSK и фильтр формирования импульсов. Для правильной работы демодуляции входной сигнал в блок демодулятора CPFSK должен иметь правильное выравнивание. Различные блоки в этой модели вводят задержки обработки. Из-за этих задержек входной сигнал в блок демодулятора CPFSK не находится в правильном выравнивании.

Оба блока Raised Cosine Transmit и Receive Filter создают задержку. Задержка определяется как:

где Ts представляет время входной выборки блока Raised Cosine Transmit Filter.

Время входной выборки блока фильтра передачи с увеличенным косинусом равно времени выходной выборки блока фильтра приема с увеличенным косинусом. Следовательно, общая задержка на выходе фильтра приема с повышенным косинусом равна:

или

как GroupDelay = 4

Блок демодулятора CPFSK принимает этот задержанный сигнал и затем обрабатывает каждый набор из 8 выборок на символ для вычисления 1 выходного символа. Необходимо убедиться, что демодулятор CPFSK принимает входные выборки в правильном наборе выборок. Для двоичного CPFSK с индексом модуляции 1/2 вход демодулятора должен выравниваться вдоль четного числа символов. Следует отметить, что это требование применяется только к двоичному CPFSK с индексом модуляции 1/2. Другие схемы CPM с различными значениями M-ary и индексами модуляции имеют различные требования.

Чтобы гарантировать, что демодулятор CPFSK в этой модели получает правильный набор входных выборок с правильной выравниванием, введите задержку в 8 выборок (в данном примере ). Полная задержка на входе демодулятора CPFSK равна , что равно двум задержкам символа (2.T, где T - период символа).

В режиме на основе выборок демодулятор CPFSK вводит задержку длины Traceback + 1 отсчетов на своем выходе. В этом примере длина Traceback равна 16. Следовательно, общая задержка приемника в блоке вычисления частоты ошибок равна 17 + 2 или 19. Дополнительные сведения см. в разделе Задержки цифровой модуляции.