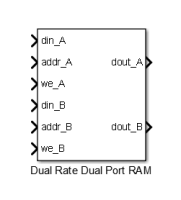

Двухпортовая ОЗУ, поддерживающая две скорости

Кодер HDL/RAM HDL

Двухпортовый блок двухпортовой ОЗУ моделирует ОЗУ, которое поддерживает одновременные операции чтения и записи на разные адреса с двумя тактовыми скоростями. Порт A ОЗУ может работать с одной скоростью, а порт B - с другой.

В высокопроизводительных аппаратных приложениях этот блок можно использовать для доступа к оперативной памяти дважды за тактовый цикл. При создании кода HDL этот блок отображается в двухпортовое ОЗУ с двумя тактовыми импульсами в большинстве FPGA.

Доступ к различным адресам из портов A и B возможен одновременно. Вы также можете считывать один и тот же адрес из портов A и B.

Однако не обращайтесь к адресу с одного порта ОЗУ, пока он записывается с другого порта ОЗУ. Во время моделирования при доступе к адресу из одного порта ОЗУ одновременно с записью этого адреса из другого порта ОЗУ программное обеспечение сообщает об ошибке.

В ОЗУ действует режим «первая запись». При записи в ОЗУ новые данные записи немедленно становятся доступными на выходном порту.

Битовая ширина адреса. Минимальная битовая ширина равна 2, а максимальная битовая ширина равна 28. Значение по умолчанию - 8.

Блок имеет следующие порты:

din_AЗапись данных для порта RAM A. Данные могут иметь любую ширину. Он наследует ширину и тип данных из входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_AАдрес записи для порта RAM A.

Тип данных: скалярное целое число без знака (uintN) или беззнаковая фиксированная точка (ufixN) с длиной фракции 0

we_AВключить запись для порта RAM A. Установка we_A кому true для операции записи, или false для операции чтения.

Тип данных: Логический

din_BЗапись данных для порта RAM B. Данные могут иметь любую ширину и наследуют ширину и тип данных из входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_BАдрес записи для порта RAM B.

Тип данных: скалярное целое число без знака (uintN) или беззнаковая фиксированная точка (ufixN) с длиной фракции 0

we_BРазрешение записи для порта ОЗУ B. Установка we_B кому true для операции записи, или false для операции чтения.

Тип данных: Логический

dout_AВыходные данные из адреса порта RAM A, addr_A.

dout_BВыходные данные из адреса порта B ОЗУ, addr_B.