Двухпортовая ОЗУ с одним портом вывода

Кодер HDL/RAM HDL

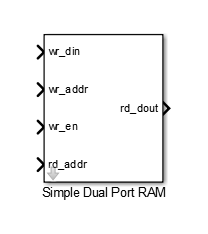

Блок простого двухпортового ОЗУ моделирует ОЗУ, которое поддерживает одновременные операции чтения и записи и имеет один выходной порт для чтения данных. Этот блок можно использовать для создания кода HDL, который отображается в ОЗУ в большинстве FPGA.

Простое двухпортовое ОЗУ аналогично двухпортовому ОЗУ, но двухпортовое ОЗУ имеет как порт вывода данных записи, так и порт вывода данных чтения.

Во время операции записи, если операция чтения происходит по тому же адресу, на выходе появляются старые данные.

Битовая ширина адреса. Минимальная битовая ширина равна 2, а максимальная битовая ширина равна 29. Значение по умолчанию - 8.

Блок имеет следующие порты:

wr_dinЗапись входных данных. Данные могут иметь любую ширину. Он наследует ширину и тип данных из входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

wr_addrАдрес записи.

Тип данных: скалярное целое число без знака (uintN) или беззнаковая фиксированная точка (ufixN) с длиной фракции 0

wr_enВключить запись.

Тип данных: Логический

rd_addrАдрес для чтения.

Тип данных: скалярное целое число без знака (uintN) или беззнаковая фиксированная точка (ufixN) с длиной фракции 0

rd_doutВыходные данные из считанного адреса, rd_addr.