Параметры, которые настраивают создание файлов сценариев, задаются на панели Сценарии инструмента EDA (EDA Tool Scripts). Эти параметры соответствуют свойствам, описанным в разделе Свойства для управления созданием сценариев.

Чтобы просмотреть и задать параметры сценариев инструмента EDA, выполните следующие действия.

Откройте диалоговое окно «Параметры конфигурации».

Выберите панель Создание кода HDL (HDL Code Generation) > Сценарии инструмента EDA (EDA Tool Scripts).

Параметр Генерировать сценарии EDA (Generate EDA scripts) управляет созданием файлов сценариев. По умолчанию этот параметр выбран.

Если вы хотите отключить создание сценариев, снимите этот флажок и нажмите кнопку Применить.

Список в левой части панели Сценарии инструмента EDA (EDA Tool Scripts) позволяет выбрать несколько категорий опций. Выберите категорию и задайте нужные параметры. Категории:

Сценарий компиляции: Параметры настройки сценариев для компиляции сгенерированного кода VHDL ® или Verilog ®. Дополнительные сведения см. в разделе Параметры сценария компиляции.

Сценарий моделирования: Параметры, связанные с настройкой сценариев для имитаторов ЛПВП. Дополнительные сведения см. в разделе Параметры сценария моделирования.

Сценарий синтеза: Параметры, связанные с настройкой сценариев для инструментов синтеза. Дополнительные сведения см. в разделе Параметры сценария синтеза.

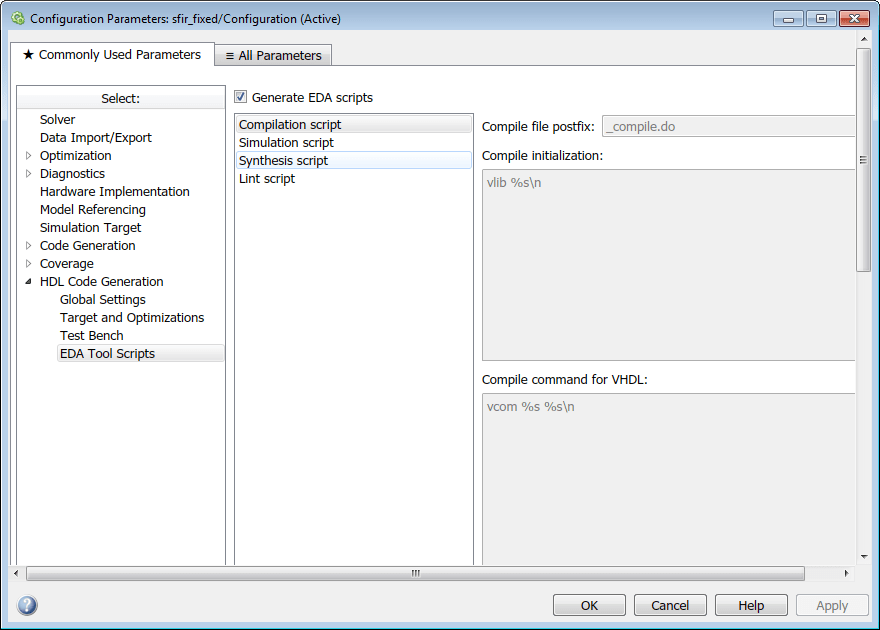

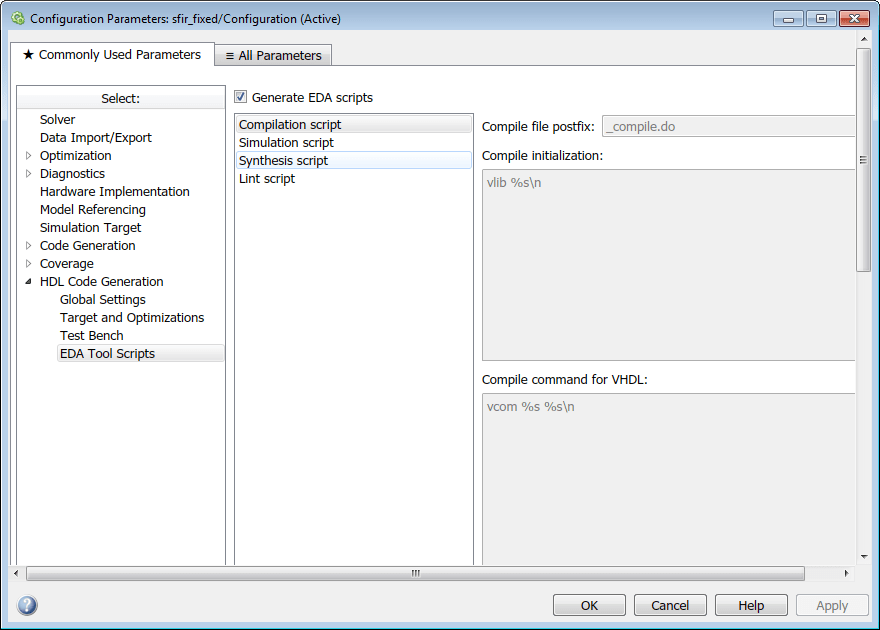

На следующем рисунке показана панель «Сценарий компиляции» с параметрами по умолчанию.

В следующей таблице представлены параметры сценария компиляции.

| Опцион и по умолчанию | Описание |

|---|---|

Скомпилировать файл postfix '

| Постфикс добавляется к имени DUT или имени тестового стенда для формирования имени файла сценария. |

Имя: Инициализация компиляции По умолчанию: | Имя формата передано fprintf для записи Init раздел сценария компиляции. Аргумент является содержимым VHDLLibraryName свойство, которое по умолчанию'work'. Можно переопределить значение по умолчанию Init 'vlib work\n' путем изменения значения VHDLLibraryName. |

Имя: Компиляция команды для VHDL По умолчанию: | Имя формата передано fprintf для записи Cmd раздел сценария компиляции для файлов VHDL. Два аргумента являются содержанием SimulatorFlags и имя файла текущего объекта или модуля. Чтобы опустить флаги, установите SimulatorFlags кому '' (значение по умолчанию). |

Имя: команда «Компиляция» для Verilog По умолчанию: | Имя формата передано fprintf для записи Cmd раздел сценария компиляции файлов Verilog. Два аргумента являются содержанием SimulatorFlags и имя файла текущего объекта или модуля. Чтобы опустить флаги, установите SimulatorFlags кому '' (значение по умолчанию). |

Имя: Завершение компиляции По умолчанию: | Имя формата передано fprintf для записи части завершения сценария компиляции. |

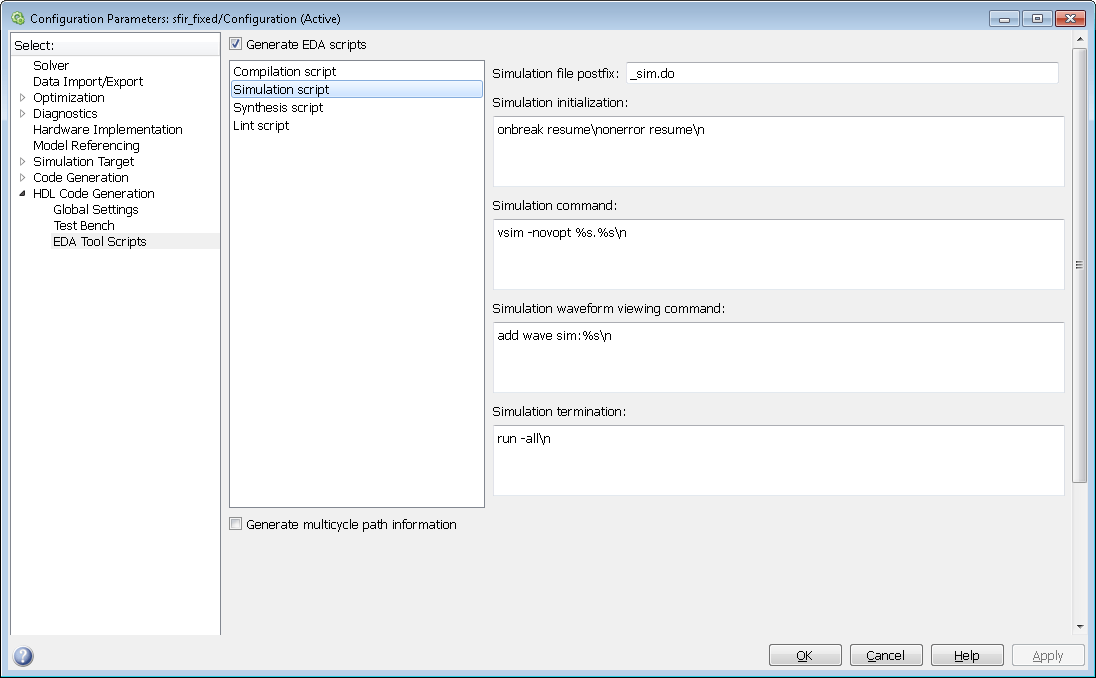

На следующем рисунке показана панель сценария моделирования с параметрами, установленными по умолчанию.

В следующей таблице представлены параметры сценария моделирования.

| Опцион и по умолчанию | Описание |

|---|---|

Постфикс файла моделирования

| Постфикс добавляется к имени модели или тестового стенда для формирования имени файла сценария моделирования. |

Инициализация моделирования По умолчанию: ['onbreak resume\nonerror resume\n'] | Имя формата передано fprintf для записи раздела инициализации сценария моделирования. |

Команда моделирования По умолчанию: | Имя формата передано Если ваш Вторым неявным аргументом является имя модуля или сущности верхнего уровня. |

Команда просмотра имитационной формы сигнала По умолчанию: | Имя формата передано fprintf для записи команды просмотра формы сигнала сценария моделирования. Имена сигналов модулей или объектов верхнего уровня являются неявными аргументами. |

Завершение моделирования По умолчанию: | Имя формата передано fprintf для записи Term часть сценария моделирования. |

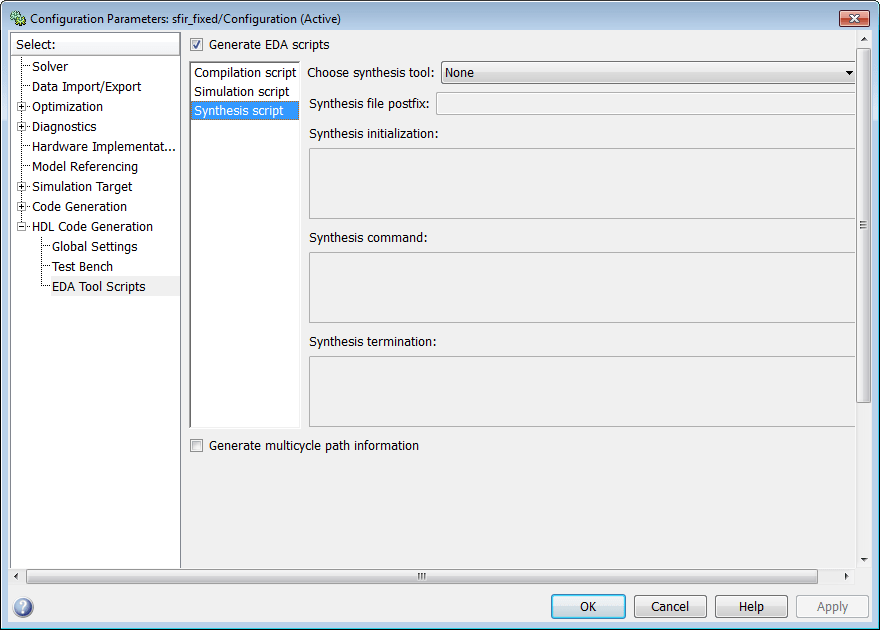

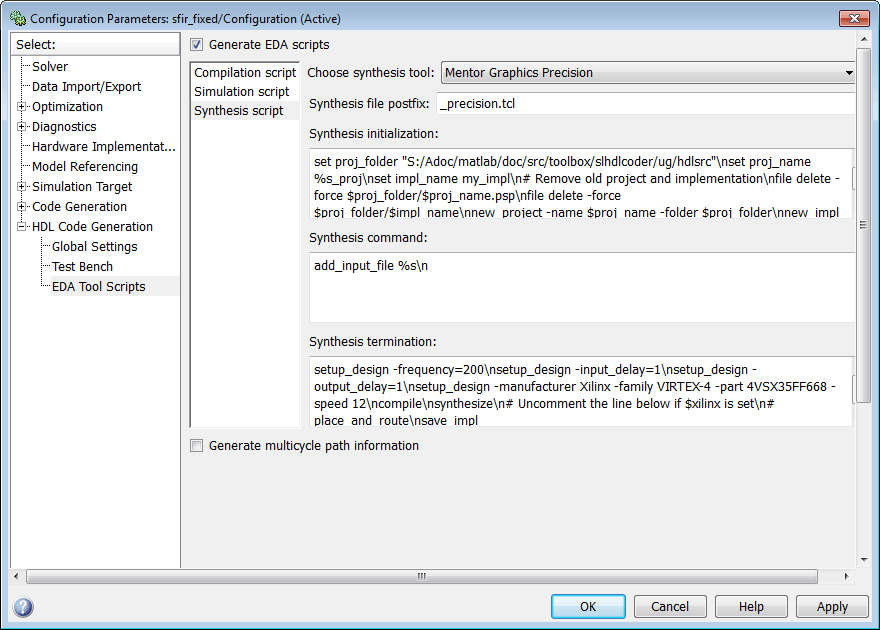

На следующем рисунке показана панель сценария синтеза с параметрами, установленными в значения по умолчанию. Свойство инструмента «Выбрать синтез» по умолчанию имеет значение None, что отключает генерацию сценария синтеза.

Чтобы включить генерацию сценариев синтеза, выберите инструмент синтеза в меню Выбрать инструмент синтеза.

При выборе инструмента синтеза Coder™ HDL:

Включает генерацию сценариев синтеза.

Вводит имя файла postfix (для выбранного инструмента синтеза) в поле Synthesis file postfix.

Ввод строк (характерных для выбранного инструмента синтеза) в поля инициализации, команды и завершения.

На следующем рисунке показаны значения опций по умолчанию, введенные для инструмента Mentor Graphics ® Precision.

В следующей таблице представлены параметры сценария синтеза.

| Имя опции | Описание | ||||||||

|---|---|---|---|---|---|---|---|---|---|

Выбрать инструмент синтеза |

| ||||||||

Постфикс файла синтеза | При выборе средства синтеза постфикс для созданных имен файлов синтеза устанавливается в одно из следующих значений:

| ||||||||

Инициализация синтеза | Имя формата передано fprintf для записи Init раздел сценария синтеза. Строка по умолчанию - это команда создания проекта синтеза. Неявным аргументом является имя модуля или сущности верхнего уровня. Содержимое строки зависит от выбранного инструмента синтеза. | ||||||||

Команда синтеза | Имя формата передано fprintf для записи Cmd раздел сценария синтеза. Неявным аргументом является имя файла сущности или модуля.Содержимое строки зависит от выбранного инструмента синтеза. | ||||||||

Завершение синтеза | Имя формата передано fprintf для записи Term раздел сценария синтеза.Содержимое строки зависит от выбранного инструмента синтеза. |