При определении пользовательской ссылочной конструкции можно дополнительно использовать свойства в hdlcoder.ReferenceDesign для определения пользовательских параметров и функций обратного вызова.

Этот код MATLAB ® показывает, как определить пользовательские параметры и зарегистрировать дескриптор функции пользовательских функций обратного вызова в функции определения ссылочного проекта.

function hRD = plugin_rd() % Reference design definition % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'My Reference Design'; hRD.BoardName = 'ZedBoard'; % Tool information hRD.SupportedToolVersion = {'2018.3'}; %% Add custom design files % ... % ... %% Add optional custom parameters by using addParameter property. % Specify custom 'DUT path' and 'Channel Mapping' parameters. % The parameters get populated in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. hRD.addParameter( ... 'ParameterID', 'DutPath', ... 'DisplayName', 'Dut Path', ... 'DefaultValue', 'Rx', ... 'ParameterType', hdlcoder.ParameterType.Dropdown, ... 'Choice', {'Rx', 'Tx'}); hRD.addParameter( ... 'ParameterID', 'ChannelMapping', ... 'DisplayName', 'Channel Mapping', ... 'DefaultValue', '1'); %% Enable JTAG MATLAB as AXI Master IP Insertion. The IP % insertion setting is visible in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. By default, the % AddJTAGMATLABasAXIMasterParameter property is set to 'true'. hRD.AddJTAGMATLABasAXIMasterParameter = 'true'; hRD.JTAGMATLABasAXIMasterDefaultValue = 'on'; %% Add custom callback functions. These are optional. % With the callback functions, you can enable custom % validations, customize the project creation, software % interface model generation, and the bistream build. % Register the function handle of these callback functions. % Specify an optional callback for 'Set Target Reference Design' % task in Workflow Advisor. Use property name % 'PostTargetReferenceDesignFcn'. hRD.PostTargetReferenceDesignFcn = ... @my_reference_design.callback_PostTargetReferenceDesign; % Specify an optional callback for 'Set Target Interface' task in Workflow Advisor. % Use the property name 'PostTargetInterfaceFcn'. hRD.PostTargetInterfaceFcn = ... @my_reference_design.callback_PostTargetInterface; % Specify an optional callback for 'Create Project' task % Use the property name 'PostCreateProjectFcn' for the ref design object. hRD.PostCreateProjectFcn = ... @my_reference_design.callback_PostCreateProject; % Specify an optional callback for 'Generate Software Interface Model' task % Use the property name 'PostSWInterfaceFcn' for the ref design object. hRD.PostSWInterfaceFcn = ... @my_reference_design.callback_PostSWInterface; % Specify an optional callback for 'Build FPGA Bitstream' task % Use the property name 'PostBuildBitstreamFcn' for the ref design object. hRD.PostBuildBitstreamFcn = ... @my_reference_design.callback_PostBuildBitstream; % Specify an optional callback for 'Program Target Device' % task to use a custom programming method. hRD.CallbackCustomProgrammingMethod = ... @my_reference_design.callback_CustomProgrammingMethod; %% Add interfaces % ... % ...

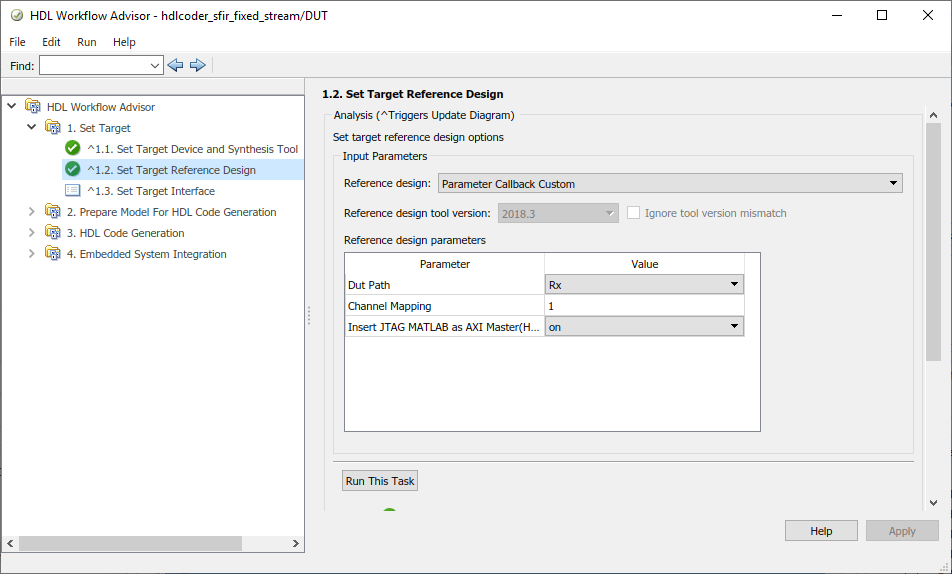

С помощью addParameter способ hdlcoder.ReferenceDesign , можно определить пользовательские параметры. В предыдущем примере кода ссылочная конструкция определяет два пользовательских параметра: DUT Path и Channel Mapping. Чтобы узнать больше о addParameter метод, см. addParameter.

По умолчанию HDL Coder™ добавляет параметр Insert JTAG MATLAB в качестве AXI Master (требуется проверка HDL) ко всем ссылочным конструкциям. При установке для этого параметра значения onгенератор кода автоматически вставляет JTAG MATLAB AXI Master IP в эталонную конструкцию. С помощью JTAG MATLAB AXI Master IP можно легко получить доступ к регистрам AXI в сгенерированном ядре DUT IP на плате FPGA из MATLAB через соединение JTAG. См. также Настройка для MATLAB AXI Master (HDL Verifier).

Для использования этой возможности необходимо установить и загрузить пакеты поддержки HDL Verifier™ оборудования. См. раздел Загрузка пакета поддержки платы FPGA (HDL Verifier).

Генератор кода регулирует Рабскую Ширину удостоверения личности AXI4, чтобы приспособить MATLAB как IP-соединение Владельца AXI. После создания ядра IP HDL и проекта эталонного дизайна можно открыть проект блока Vivado ®, чтобы увидеть JTAG MATLAB AXI Master IP, вставленный в эталонный проект.

В предыдущем примере кода ссылочная конструкция определяет AddJTAGMATLABasAXIMasterParameter и JTAGMATLABasAXIMasterDefaultValue свойства hdlcoder.ReferenceDesign класс. Эти свойства управляют поведением по умолчанию параметра Вставить JTAG MATLAB как мастер AXI (требуется верификатор HDL) в задаче Задать целевое ссылочное проектирование помощника по рабочим процессам HDL. Если не указать ни одно из этих свойств в hdlcoder.ReferenceDesign класс, параметр Insert JTAG MATLAB as AXI Master (HDL Verifier Required) отображается в задаче Set Target Reference Design и устанавливается значение off. Этот пример кода иллюстрирует поведение по умолчанию.

%% Default behavior of Insert JTAG as AXI Master option % This parameter controls visibility of the option in % 'Set Target Reference Design Task' of HDL Workflow Advisor % By default, the parameter value is set to 'true', % which means that the option is displayed in the UI. If % you do not want the parameter to be displayed, set this % value to 'false'. hRD.AddJTAGMATLABasAXIMasterParameter = 'true'; % This parameter controls the value of the option in the % the 'Set Target Reference Design Task' task. By default, % the value is 'off', which means that the parameter is % displayed in the task and the value is off. To enable % automatic insertion of JTAG AXI Master IP in the reference % design, set this value to 'on'. In that case, the % AddJTAGMATLABasAXIMasterParameter must be set to 'true'. hRD.JTAGMATLABasAXIMasterDefaultValue = 'off';

Примеры см. в разделе:

При открытии помощника по рабочему процессу HDL кодер HDL заполняет задачу Задать целевое ссылочное проектирование с указанным именем ссылочного проекта, версией инструмента, пользовательскими параметрами и опцией Вставить JTAG MATLAB как AXI Master (требуется верификатор HDL), которая имеет значение on.

Затем кодер HDL передает эти значения параметров функциям обратного вызова в структуре ввода.

Если инструментом синтеза является Xilinx ® Vivado, кодер HDL устанавливает значения ссылочных параметров конструкции в качестве переменных. Затем переменные вводятся в Tcl-файл конструкции блока. Этот фрагмент кода является примером из файла Tcl создания ссылочного проектного проекта .

update_ip_catalog

set DutPath {Rx}

set ChannelMapping {1}

source vivado_custom_block_design.tcl

В коде показано, как кодер HDL устанавливает ссылочные параметры конструкции перед подачей в Tcl-файл пользовательской конструкции блока.

В определении ссылочного проекта можно зарегистрировать дескриптор функции для ссылки на пользовательские функции обратного вызова. Затем можно:

Включить настраиваемые проверки.

Динамическая настройка ссылочной конструкции.

Настройка параметров создания ссылочного проектного проекта.

Измените созданную модель программного интерфейса.

Настройте процесс построения битового потока FPGA.

Укажите пользовательский метод программирования FPGA.

С помощью hdlcoder.ReferenceDesign , можно определить имена свойств обратного вызова. Свойства обратного вызова имеют соглашение об именовании. Функции обратного вызова могут иметь любое имя. В помощнике по рабочим процессам HDL можно определить функции обратного вызова для настройки этих задач.

| Задача советника по рабочим процессам | Имя свойства обратного вызова | Функциональность |

|---|---|---|

Задать целевую ссылочную конструкцию |

|

|

Задать целевой интерфейс | PostTargetInterfaceFcn | Включить настраиваемые проверки. Пример проверки отсутствия выбора определенного интерфейса для определенного пользовательского параметра см. в разделе |

Создать проект | PostCreateProjectFcn | Укажите пользовательские параметры при создании проекта с помощью кодера HDL. Пример см. в разделе |

Создание программного интерфейса | PostSWInterfaceFcn | Измените созданную модель программного интерфейса. Пример см. в разделе |

Построение битового потока FPGA | PostBuildBitstreamFcn | Укажите пользовательские параметры при построении битового потока FPGA. При использовании этой функции процесс построения не может выполняться извне. Необходимо запустить процесс построения в помощнике по рабочим процессам HDL, сняв флажок Выполнить процесс построения внешне в задаче Bitstream сборки FPGA. Пример см. в разделе |

Целевое устройство программы | CallbackCustomProgrammingMethod | Укажите пользовательский метод программирования FPGA. Пример см. в разделе |

Для каждой функции обратного вызова, которую кодер HDL должен выполнить после выполнения задачи, создайте файл, определяющий функцию MATLAB с любым именем.

Убедитесь, что функция обратного вызова имеет задокументированные входные и выходные аргументы.

Убедитесь, что функции доступны по пути MATLAB.

Зарегистрируйте дескриптор функции функций обратного вызова в функции определения ссылочного проекта.

Следуйте правилам именования для имен свойств обратного вызова.

Дополнительные сведения об этих функциях обратного вызова см. в разделе hdlcoder.ReferenceDesign.

hdlcoder.Board | hdlcoder.ReferenceDesign