При открытии помощника по рабочим процессам HDL и запуске IP Core Generation для модели Simulink ® можно указать общую платформу Xilinx ® или общую платформу Intel ®. Затем поток операций создает общее IP-ядро, которое можно интегрировать в любую целевую платформу по своему выбору. Для интеграции с ядром IP определите и зарегистрируйте пользовательский эталонный дизайн для целевой платы.

Невозможно создать ядро IP HDL без AXI4 подчиненного интерфейса. По крайней мере один порт DUT должен соответствовать интерфейсу AXI4 или AXI4-Lite. Чтобы создать ядро IP HDL без AXI4 подчиненных интерфейсов, используйте рабочий процесс создания ядра IP Simulink. Дополнительные сведения см. в разделе Создание независимого от платы IP-ядра HDL на основе модели Simulink.

В одном IP-ядре невозможно сопоставить интерфейс AXI4 и интерфейс AXI4-Lite.

Входы и выходы должны иметь битовую ширину меньше или равную 32 битам.

Входные и выходные данные должны быть скалярными.

Порты должны иметь 32-разрядную ширину.

Порты должны быть скалярными.

Можно иметь максимум один входной видеопорт и один выходной видеопорт.

Интерфейс AXI4-Stream Video не поддерживается в сопроцессировании - для блокировки синхронизации процессора/FPGA должно быть установлено значение Free running режим. Coprocessing – blocking режим не поддерживается.

Чтобы создать независимое от платы ядро IP для использования в среде интеграции встраиваемых систем, такой как Intel Qsys, Xilinx EDK или Xilinx IP Integrator:

Создайте проект Coder™ HDL, содержащий ваш стенд проектирования и тестирования MATLAB ®, или откройте существующий проект.

В помощнике по рабочим процессам HDL определите типы ввода и выполните преобразование с фиксированной точкой.

Сведения о том, как преобразовать конструкцию в фиксированную точку, см. в разделах Создание базового кода HDL и Синтез FPGA от MATLAB.

В помощнике по рабочим процессам HDL в задаче Выбор цели создания кода:

Рабочий процесс: Выбрать IP Core Generation.

Платформа: Выбор Generic Xilinx Platform или Generic Altera Platform.

В зависимости от выбранного значения генератор кода автоматически задает инструмент «Синтез». Например, при выборе Generic Xilinx Platform, инструмент синтеза автоматически изменяется на Xilinx Vivado.

Дополнительные исходные файлы: если вы используете hdl.BlackBox object™ системы, чтобы включить существующий код Verilog ® или VHDL ®, введите имена файлов. Введите имя каждого файла вручную, разделяя его точкой с запятой (;) или с помощью... кнопка. Язык исходного файла должен совпадать с целевым языком.

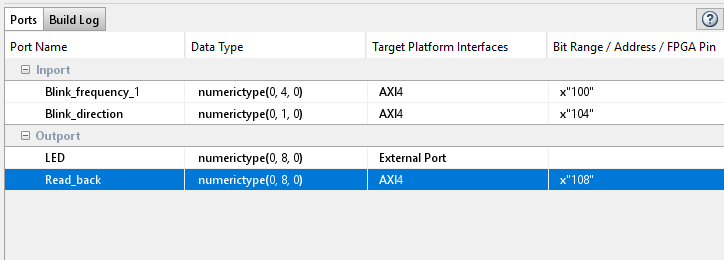

На шаге Set Target Interface для каждого порта выберите опцию из выпадающего списка Target Platform Interfaces.

На шаге Создание кода HDL (HDL Code Generation) при необходимости укажите параметры создания кода и нажмите кнопку Выполнить (Run).

На панели сообщений помощника по рабочим процессам HDL щелкните ссылку отчета по IP-ядру для просмотра подробной документации по сформированному IP-ядру.