При открытии помощника по рабочим процессам HDL и запуске IP Core Generation для модели Simulink ® можно указать общую платформу Xilinx ® или общую платформу Intel ®. Затем поток операций создает общее IP-ядро, которое можно интегрировать в любую целевую платформу по своему выбору. Для интеграции с ядром IP определите и зарегистрируйте пользовательский эталонный дизайн для целевой платы с помощью hdlcoder.ReferenceDesign класс. Дополнительные сведения см. в следующих разделах:

Чтобы создать независимое от платы пользовательское IP-ядро для использования в среде интеграции встраиваемых систем, такой как Intel Qsys, Xilinx EDK или Xilinx IP Integrator:

Выберите DUT в модели Simulink и откройте помощник по рабочим процессам HDL. Например, откройте модель hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

Задайте путь к установленному средству синтеза для целевого устройства с помощью hdlsetuptoolpath функция. Например, если Xilinx Vivado ® является инструментом синтеза, используйте команду:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2018.2\bin\vivado.bat');

Последнюю поддерживаемую версию средства синтеза см. в разделах Поддержка языка HDL и Поддерживаемые сторонние инструменты и оборудование.

Откройте помощник по рабочим процессам HDL для подсистемы DUT. Для модели мигания светодиода led_counter Подсистема - это DUT. В задании Set Target > Set Target Device and Synthesis Tool выполните следующие действия.

В поле Целевой рабочий процесс выберите IP Core Generation.

Для целевой платформы, в зависимости от средства синтеза и устройства, на которое вы нацелены, выберите Generic Altera Platform или Generic Xilinx Platform. Щелкните Выполнить эту задачу.

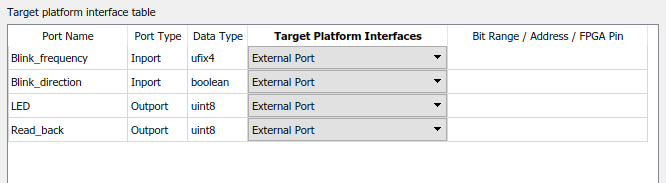

В задании Set Target > Set Target Interface выберите интерфейс целевой платформы для каждого порта и нажмите Apply. Каждый порт DUT можно сопоставить с одним из следующих интерфейсов: AXI4-Lite, AXI4, AXI4-Stream, AXI4-Stream Video, External Port, или FPGA Data Capture - JTAG. Дополнительные сведения об этих интерфейсах см. в разделе Интерфейсы целевой платформы.

Можно также сопоставить порты с несколькими интерфейсами целевой платформы. Дополнительные сведения см. в разделе Создание IP-ядра HDL с несколькими AXI4-Stream и основными интерфейсами AXI4.

Если не требуется сопоставлять порты DUT с AXI4 подчиненными интерфейсами, их можно сопоставить с External Port интерфейсы.

Разверните задачу Задать параметры создания кода. Щелкните правой кнопкой мыши задачу Задать опции оптимизации и выберите Выполнить до выбранной задачи.

В разделе Создание кода HDL > Создание кода RTL и задача IP Core можно указать:

Требуется ли подключить ядро IP DUT к нескольким главным интерфейсам AXI. По умолчанию Рабское значение Ширины удостоверения личности AXI4 12, что позволяет подключить ядро IP HDL к одному главному интерфейсу AXI. Чтобы соединить IP ядро DUT с несколькими Основными интерфейсами AXI, Вы можете хотеть увеличить Рабскую Ширину удостоверения личности AXI4. При выполнении этой задачи этот параметр сохраняется в DUT в качестве AXI4SlaveIDWidth свойств блока HDL.

Дополнительные сведения см. в разделе Определение нескольких главных интерфейсов AXI в эталонных конструкциях для доступа к подчиненному интерфейсу DUT AXI4.

Требуется ли создать AXI4 подчиненный интерфейс по умолчанию. По умолчанию HDL Coder™ генерирует AXI4 подчиненные интерфейсы для таких сигналов, как тактовый сигнал, сброс, готовность, метка времени и т.д. Если не требуется создавать подчиненные интерфейсы AXI4, снимите флажок Генерировать подчиненный интерфейс по умолчанию (Generate default default AXI4 slave interface).

Примечание

Если любой из портов DUT сопоставлен с AXI4 подчиненными интерфейсами в задаче Set Target Interface, генератор кода сопоставляет порты с AXI4 подчиненными интерфейсами, независимо от того, снят ли флажок Generate default AXI4 slave interface.

Щелкните Выполнить эту задачу. При снятии флажка и запуске задачи генератор кода сохраняет этот параметр в подсистеме DUT в качестве GenerateDefaultAXI4Slave свойств блока HDL.

После выполнения задачи HDL Coder генерирует основные файлы IP в папке вывода, показанной в поле основной папки IP, включая документацию HTML. Чтобы просмотреть отчет по IP-ядру, щелкните ссылку в окне сообщения.

При запуске IP Core Generation кроме того, можно создать ядро IP HDL без каких-либо AXI4 подчиненных интерфейсов в эталонном проекте.

Чтобы запустить этот рабочий процесс, откройте помощник по рабочим процессам HDL, укажите Generic Xilinx Platform или Generic Altera Platform в качестве целевой платформы и сопоставить порты DUT только с внешним портом или AXI4-Stream интерфейсом с отображением TLAST. Кроме того, при создании IP-ядра HDL в задаче Создать RTL-код и IP-ядро снимите флажок Создать подчиненный интерфейс AXI4 по умолчанию и выберите Выполнить эту задачу.

Используйте эту возможность в следующих случаях:

Настройка основных параметров IP с помощью подчиненных интерфейсов AXI4 не требуется.

Требуется создать пользовательскую эталонную конструкцию без AXI4 подчиненных интерфейсов, таких как автономные платы FPGA.

Кроме того, исключение генерации AXI4 подчиненных интерфейсов в таких случаях снижает использование аппаратных ресурсов и сложность проектирования.

Примечание

Внешние интерфейсы ввода-вывода и внутренние интерфейсы ввода-вывода соединяют ядро IP HDL с другими существующими IP-адресами в пользовательском эталонном проекте. Для определения этих интерфейсов используется addInternalIOInterface и addExternalIOInterface методы hdlcoder.ReferenceDesign класс.

Для интеграции ядра IP HDL можно создать пользовательский эталонный проект без AXI4 подчиненных интерфейсов. В пользовательской ссылочной конструкции можно использовать только интерфейс внешнего ввода-вывода, внутреннего ввода-вывода или AXI4-Stream с отображением TLAST. Примеры см. в разделе:

При создании IP-ядра HDL без AXI4 подчиненных интерфейсов применяются определенные ограничения. См. раздел Ядро IP без ограничений подчиненного интерфейса AXI4.

DUT должен быть атомной системой.

Одно и то же ядро IP не может использовать как интерфейс AXI4, так и интерфейс AXI4-Lite.

DUT не может содержать блоки Xilinx System Generator или блоки Intel DSP Builder Advanced.

Если целевым языком является VHDL ®, а инструментом синтеза является Xilinx ISE или Intel Quartus Prime, DUT не может содержать ссылку на модель.

Входной и выходной порты должны иметь битовую ширину меньше или равную 32 битам.

Входные и выходные порты должны быть скалярными.

Порты должны иметь 32-разрядную ширину.

Порты должны быть скалярными.

Можно иметь максимум один входной видеопорт и один выходной видеопорт.

Интерфейс AXI4-Stream Video не поддерживается в Coprocessing – blocking режим. Для синхронизации процессора/FPGA должно быть установлено значение Free running режим.

Можно сопоставить порты только с внешними/внутренними интерфейсами ввода-вывода или AXI4-Stream интерфейсом с отображением TLAST. Другие интерфейсы, которые требуют AXI4 подчиненных интерфейсов, такие как AXI4 Master, AXI4-Stream и AXI4-Stream Video, не поддерживаются.

Необходимо использовать Free running режим синхронизации процессора/FPGA. Coprocessing – blocking режим не поддерживается.