Опции и параметры, влияющие на создание кода HDL, можно просматривать и редактировать в диалоговом окне Параметры конфигурации (Configuration Parameters) или в Обозревателе моделей (Model Explorer). В этом примере показано, как можно использовать диалоговое окно Параметры конфигурации (Configuration Parameters) для создания кода HDL для модели симметричного фильтра FIR.

Перед созданием кода HDL модель должна быть совместима для создания кода HDL. Сведения о проверке и обновлении модели на совместимость с HDL см. в разделе Проверка совместимости HDL модели Simulink с помощью помощника по коду HDL.

В этом примере используется модель симметричного фильтра FIR, совместимая с генерацией кода HDL. Чтобы открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует разделение труда, которое подходит для конструирования ЛПВП.

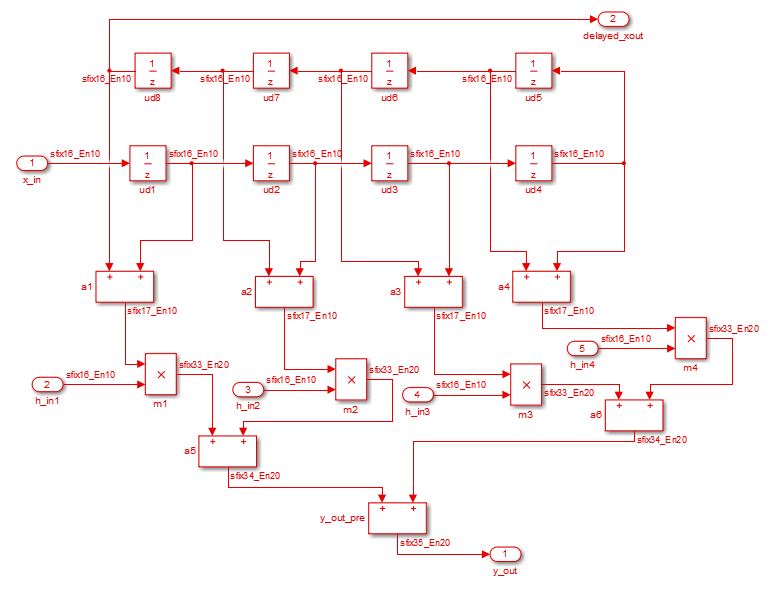

symmetric_fir подсистема, реализующая алгоритм фильтрации, является тестируемым устройством (DUT). Объект HDL генерируется из этой подсистемы.

Компоненты модели верхнего уровня, управляющие подсистемой, работают как испытательный стенд.

Модель верхнего уровня генерирует 16-разрядные входные сигналы с фиксированной точкой для symmetric_fir подсистема. Блок «Сигнал из рабочего пространства» генерирует тестовый входной (стимулирующий) сигнал для фильтра. Четыре постоянных блока обеспечивают коэффициенты фильтра. Блоки Scope используются для моделирования и не используются для генерации кода HDL.

Для перехода к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB ®:

Создание папки с именем sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели примера и папок и сгенерированный код HDL. Используйте папку, которая не находится в дереве папок MATLAB.

Сделать sl_hdlcoder_work папка рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохранение локальной копии sfir_fixed в текущую рабочую папку. Оставьте модель открытой.

На этом рисунке показана панель «Создание кода HDL» верхнего уровня диалогового окна «Параметры конфигурации». Чтобы открыть это диалоговое окно, в галерее Приложения щелкните Кодер HDL. Появится вкладка Код HDL (HDL Code). В разделе «Подготовка» нажмите кнопку «Параметры».

Панель Создание кода HDL (HDL Code Generation) содержит основные параметры, определяющие DUT, для которого требуется создать код, язык назначения и настройки папки. Параметр Generate HDL for setting синхронизируется с меню Code for на вкладке HDL Code. Можно также использовать кнопки на этой панели, чтобы инициировать создание кода и выполнить проверку совместимости. Панель Создание кода HDL (HDL Code Generation) состоит из различных подпанелей, которые можно использовать для определения различных параметров настройки, связанных с тактовыми сигналами и сбросом сигналов в параметры отчетности и оптимизации.

На панели «Создание кода HDL»

Поле Generate HDL for определяет sfir_fixed/symmetric_fir подсистема формирования кода.

Поле Язык определяет создание кода VHDL.

Поле Папка указывает целевую папку, в которой хранятся созданные файлы кода и сценарии.

Дополнительные сведения о различных параметрах на панели «Создание кода HDL» см. в разделе Опции создания кода HDL в диалоговом окне «Параметры конфигурации».

Для создания кода нажмите кнопку «Создать». По умолчанию HDL Coder™ генерирует код VHDL в целевом объекте hdlsrc папка.

Чтобы создать код Verilog для модели:

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings).

На панели «Создание кода HDL» в поле «Язык» выберите Verilog. Оставьте другие параметры по умолчанию. Щелкните Применить (Apply), а затем Создать (Generate).

Кодер HDL компилирует модель перед созданием кода. В зависимости от опций отображения модели, таких как типы данных портов, модель может изменяться в виде после генерации кода. По мере формирования кода кодер HDL отображает сообщения о ходе выполнения в командной строке MATLAB с помощью:

Ссылка на набор конфигурации, указывающий модель, для которой применяются параметры конфигурации.

Ссылки на созданные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните ссылки.

symmetric_fir.vhd: Код VHDL. Этот файл содержит определение сущности и архитектуру RTL, реализующую symmetric_fir.vhd фильтр.

symmetric_fir_compile.do: Mentor Graphics ® ModelSim ® сценарий компиляции (команда vcom) для компиляции созданного кода VHDL.

symmetric_fir_synplify.tcl: Сценарий синтеза Synplify ®.

symmetric_fir_map.txtЭтот отчет сопоставляет сгенерированные объекты с сгенерировавшими их подсистемами. См. раздел Код трассировки с использованием файла сопоставления

Процесс завершается сообщением:

### HDL Code Generation Complete.