Консультант по рабочим процессам HDL проводит этапы создания кода HDL для подсистемы Simulink ® и процесса проектирования FPGA, такие как:

Проверка модели на совместимость генерации кода HDL и автоматическое исправление несовместимых настроек.

Создание кода HDL, тестового стенда и сценариев для создания и запуска кода и тестового стенда.

Создание испытательных стендов cosimulation или SystemVerilog DPI и покрытия кода (требуется Verifier™ HDL).

Синтез и анализ времени посредством интеграции со сторонними инструментами синтеза.

Обратная аннотация модели с информацией о критическом пути и другой информацией, полученной в процессе синтеза.

Завершите автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA, включая моделирование FPGA в цикле (требуется проверка HDL) и рабочий процесс ввода-вывода Simulink Real-Time™ FPGA.

Чтобы выбрать параметры тестового стенда и покрытия кода для генерации кода HDL из модели Simulink с помощью помощника по рабочим процессам HDL, выполните следующие действия.

Выполните шаги настройки для генерации кода HDL и синтеза FPGA из Simulink Model.

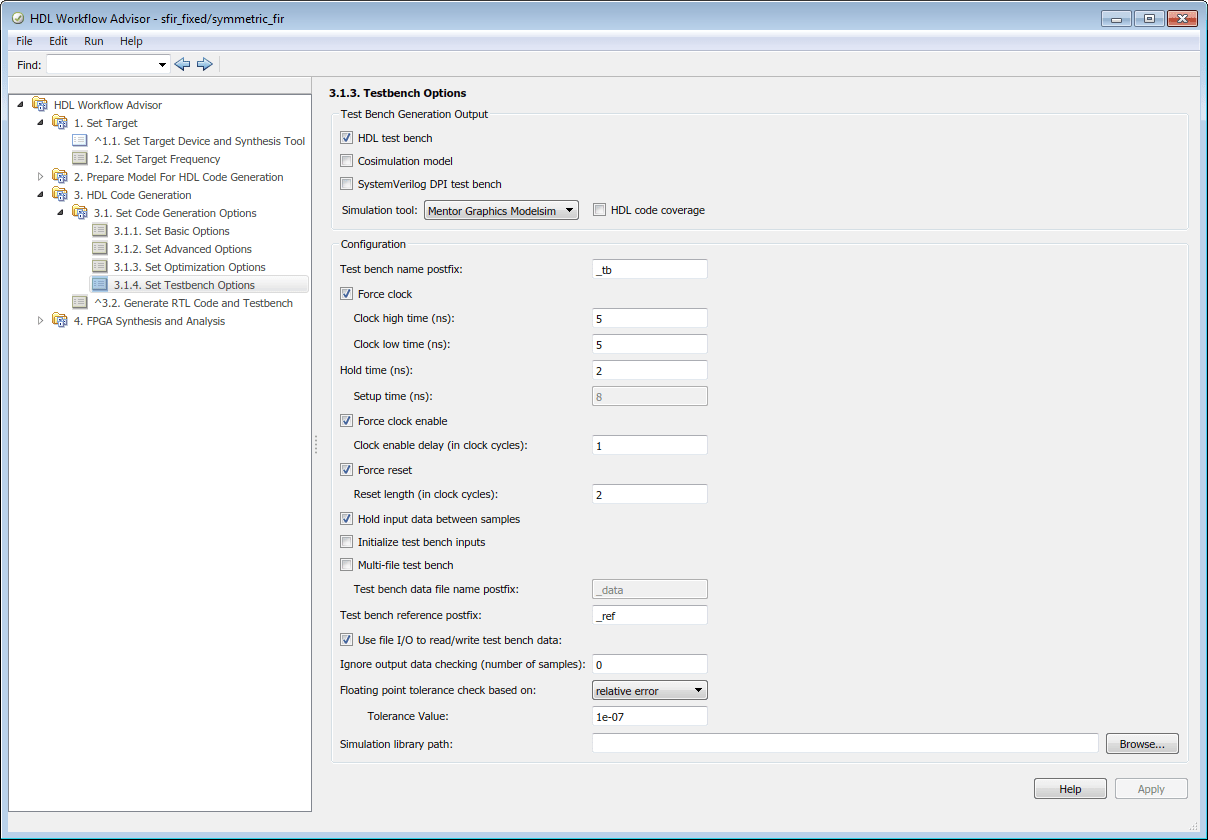

На шаге 3.1.4 мастера рабочего процесса HDL (Set Testbench Options) выберите параметры тестового стенда и покрытия кода в разделе «Выходные данные генерации тестового стенда». Кодер создает сценарий build-and-run для тестового стенда и указанного инструмента моделирования. Если выбрано несколько параметров тестового стенда, кодер генерирует один тестовый стенд и сценарий для каждого выбранного типа тестового стенда. Если выбрано покрытие кода HDL, скрипты тестового стенда включают покрытие кода для созданного кода HDL. Дополнительные сведения о различных типах тестовых стендов см. в разделе Выбор тестового стенда для сгенерированного кода HDL. После выбора параметров тестового стенда нажмите кнопку «Применить».

На шаге 3.2, Generate RTL Code and Testbench, выберите Generate test stench. Нажмите кнопку «» Применить «», а затем - кнопку «» Выполнить эту задачу «». Кодер генерирует код HDL для вашей подсистемы, а также тестовые стенды и сценарии, выбранные на шаге 3.1.3.

Если выбрана модель Cosimulation, то шаг 3.3, Verify with HDL Cosimulation, появится в Консультаторе по рабочим процессам HDL. На этом шаге автоматически запускается созданная модель косимуляции. Модель сравнивает результат выполнения кода HDL в имитаторе HDL с выводом подсистемы Simulink.

Если выбран тестовый стенд HDL, кодер генерирует сценарий компиляции, subsystemname_tb_compileи сценарий запуска, subsystemname_tb_simhdl_prj/hdlsrc/ и выполните следующие команды:modelname

do symmetric_fir_compile.do do symmetric_fir_tb_compile.do do symmetric_fir_tb_sim.do

Если выбран тестовый стенд SystemVerilog DPI, кодер создает файл сценария, subsystemname_dpi_tbhdl_prj/hdlsrc/ и выполните следующую команду:modelname

do symmetric_fir_dpi_tb.do

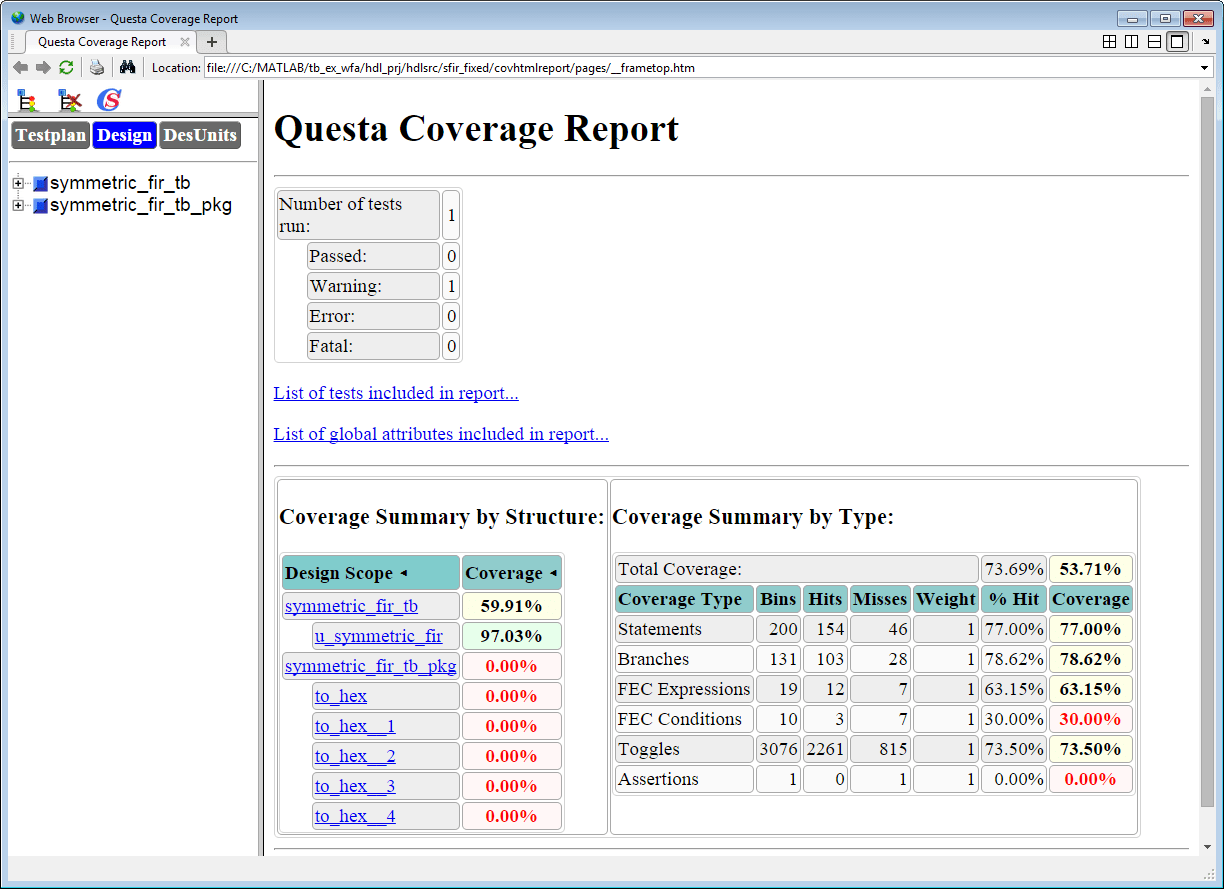

Если выбрано покрытие кода HDL, отчет о покрытии кода с любого тестового стенда, включая модель косимуляции, сохраняется в hdl_prj\hdlsrc\.modelname\covhtmlreport