В этом примере показано, как можно создать код HDL для простой модели счетчика и синтезировать созданный код в Xilinx ® FPGA с помощью Simulink ® HDL Workflow Advisor. Сведения о создании этой модели см. в разделе Создание модели Simulink, совместимой с HDL.

Консультант по рабочим процессам HDL помогает создавать код HDL для подсистемы Simulink и процесса проектирования FPGA, например:

Проверка модели на совместимость генерации кода HDL и автоматическое исправление несовместимых настроек.

Создание кода HDL, тестового стенда и сценариев для создания и запуска кода и тестового стенда.

Создание испытательных стендов cosimulation или SystemVerilog DPI и покрытия кода (требуется Verifier™ HDL).

Синтез и анализ времени посредством интеграции со сторонними инструментами синтеза.

Обратная аннотация модели с информацией о критическом пути и другой информацией, полученной в процессе синтеза.

Завершение автоматизированных рабочих процессов для отдельных целевых устройств разработки FPGA и рабочего процесса ввода-вывода Simulink Real-Time™ FPGA, включая моделирование FPGA в цикле.

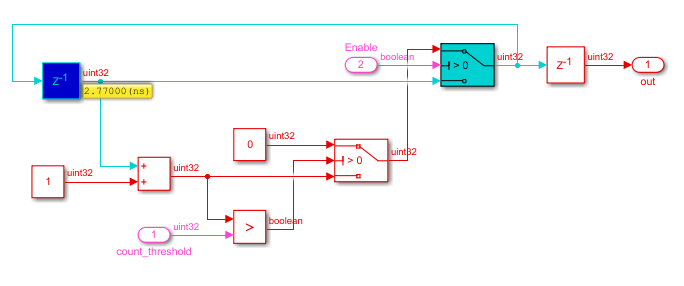

Откройте эту модель, чтобы увидеть простой счетчик. Модель подсчитывается от нуля до порогового значения, а затем возвращается к нулю. Пороговое значение устанавливается равным 15. Чтобы изменить пороговое значение, измените значение ввода на count_threshold порт. Сигнал Enable указывает, имеет ли счетчик предыдущее значение. Значение 1 указывает, что счетчик постоянно подсчитывается вверх.

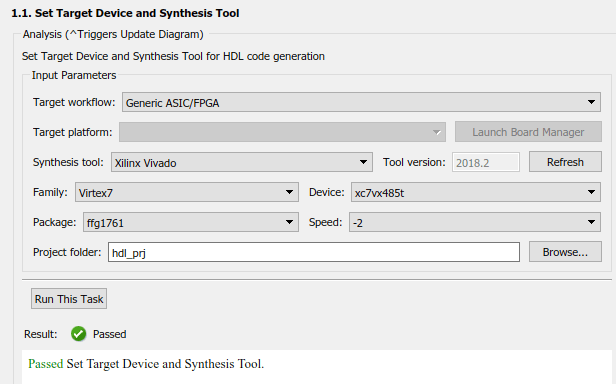

Чтобы синтезировать проект на целевой платформе, прежде чем открыть помощник по рабочим процессам HDL и запустить рабочий процесс, настройте путь к инструменту синтеза. В этом примере используется Xilinx Vivado ®, поэтому необходимо установить Xilinx Vivado. Чтобы задать траекторию движения инструмента, используйте hdlsetuptoolpath для указания на установленный исполняемый файл Xilinx Vivado 2019.2.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2019.2\bin\vivado.bat');

hdlsetuptoolpath. Сведения о новейших поддерживаемых инструментах см. в разделах Языковая поддержка HDL и Поддерживаемые сторонние инструменты и оборудование.Если требуется создать код HDL, но не синтезировать проект, нет необходимости задавать траекторию движения инструмента.

Чтобы запустить помощник по рабочим процессам HDL из модели Simulink,

На вкладке Приложения выберите Кодер HDL.

Выберите подсистему DUT в модели, HDL_DUTи убедитесь, что это имя отображается в параметре «Код для» на вкладке «Код HDL». Чтобы запомнить выбор, закрепите этот параметр. Щелкните Помощник по рабочим процессам (Workflow Advisor).

При открытии помощника по рабочим процессам HDL генератор кода может предупредить о несовместимости папки проекта. Чтобы открыть помощник, выберите Удалить и продолжить.

Помощник по рабочим процессам HDL отображает группу задач на левой панели, сгруппированную по папкам. При расширении папок отображаются доступные задачи в каждой папке. При выборе задачи или папки на правой панели отображаются сведения об этой задаче или папке. Правая панель имеет простые элементы управления для выполнения задачи с несколькими параметрами и опциями для создания кода или тестового стенда и содержит область отображения сообщений о состоянии и других результатов задачи.

Чтобы узнать больше о каждой отдельной задаче, щелкните ее правой кнопкой мыши и выберите «Что это?».

![]()

См. раздел Начало работы с консультантом по рабочим процессам HDL.

На шаге Set Target > Set Target Device and Synthesis Tool для инструмента Synthesis выберите Xilinx Vivado и выберите Запустить эту задачу. См. также Workflows in HDL Workflow Advisor. Чтобы сгенерировать код HDL, но не синтезировать код, оставьте для параметра Synthesis tool значение No Synthesis Tool Specified.

В задаче Задать целевую частоту (Set Target Frequency) укажите целевую частоту, которую должна достичь конструкция с помощью параметра Целевая частота (Target Frequency Parameter). В этом примере задайте для параметра Целевая частота (МГц) значение 200.

Чтобы проверить модель на совместимость с генерацией кода, выполните задачи в папке «Подготовка модели для генерации кода HDL». Щелкните правой кнопкой мыши задачу Проверка времени выборки и выберите Выполнить до выбранной задачи. Если при выполнении задачи создается предупреждение, выберите Изменить все и снова запустите задачу.

Чтобы изменить создание кода, используйте задачи в разделе Задать параметры создания кода. Например, чтобы настроить целевой язык HDL и папку создания целевого кода, используйте задачу Задать основные параметры. После внесения изменений нажмите кнопку «Применить».

Чтобы создать код, щелкните правой кнопкой мыши задачу Generate RTL Code and Testbench и выберите Run to Selected Task.

В окне FPGA Synthesis and Analysis (Синтез и анализ FPGA) > Perform Synthesis and P/R > Run Implementation (Выполнить синтез и анализ FPGA) снимите флажок Пропустить эту задачу и нажмите Apply (Применить). Затем щелкните правой кнопкой мыши эту задачу и выберите Выполнить до выбранной задачи.

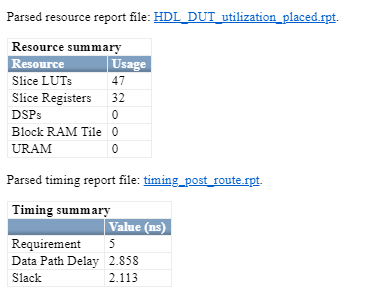

Задача отображает объем ресурсов, потребляемых конструкцией, и задержку пути данных. Провал - это разница между требуемым временем и временем поступления для комбинационного пути. В этом случае слабость является положительным значением, что означает, что данные поступили гораздо раньше требуемого времени.

Щелкните правой кнопкой мыши Аннотации модели с результатом синтеза (Annotate Model with Synthesis Result) и выберите Выполнить с выбранной задачей (Run to Selected Task). Если вы выбрали Intel Quartus Pro или Microsemi Libero SoC как инструмент синтеза, задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) недоступна. Чтобы просмотреть критический путь, запустите workflow-процесс для синтеза, а затем откройте отчеты о времени.

Просмотр аннотированного критического пути в модели.

Критический путь - это комбинированный путь между входом и выходом, который имеет максимальную задержку. Критическая задержка пути для модели счетчика 2.77ns. Задержка пути данных, указанная в задаче Run Implementation, превышает критический путь, поскольку она учитывает задержки маршрутизации в целевом FPGA. Для экономии ресурсов, оптимизации критического пути и улучшения синхронизации проектирования на целевом FPGA используйте оптимизацию скорости и площади в Coder™ HDL. Дополнительные сведения см. в разделе Оптимизация скорости и площади в кодере HDL.

Чтобы запустить рабочий процесс HDL в командной строке MATLAB ®, экспортируйте параметры помощника по рабочим процессам в сценарий. Для экспорта в сценарий в окне помощника по рабочим процессам HDL выберите «Файл» > «Экспорт в сценарий». В диалоговом окне «Экспорт конфигурации рабочего процесса» введите имя файла и сохраните сценарий. См. раздел Запуск потока операций HDL со сценарием.

hdladvisor | hdlsetuptoolpath | makehdl